#### The University of Queensland Binary Translator (UQBT) Framework

#### **Principal Investigators**

Cristina Cifuentes

The University of Queensland

Sun Microsystems Laboratories

Mike van Emmerik The University of Queensland

> Norman Ramsey Harvard University

Brian Lewis Sun Microsystems Laboratories

#### **Research Assistants/Summer Scholars/Interns**

1997: Shane Sendall (Honours student, UQ)

Dec 97 - Feb 98: Shane Sendall, Doug Simon (UQ)

1998: David Ung (PhD student, UQ)

Dec 98 - Feb 99: Ian Walters, Shawn Coyne, Trent Waddington (UQ)

Jan-Oct 99: Doug Simon, Trent Waddington (UQ)

1999: Ian Walters (Honours student, UQ)

Dec 99 - Feb 00: Simon Long (UQ)

Jun-Aug 00: Sameer Gulrajani (Sun)

Jun-Aug 00: Pavan Kumar (Sun)

Dec 00 - Feb 01: Simon Long (UQ)

Jan-Apr 01: Manel Fernandez (Sun)

May 01: Nathan Keynes (Sun)

Aug 01: Bernard Wong (Sun)

© 1996-2001, The University of Queensland © 1999-2001, Sun Microsystems, Inc

#### **Abstract**

Binary translation is a relatively new field of research. Existing binary translators rely on machine-dependent analyses that are written by hand. Such analyses are required to identify procedures, to find the code attached to those procedures, to find the targets of indirect branches, and to identify call sites and parameters. Redevelopment and hand implementation of such analyses makes it difficult and time-consuming to develop binary translators for new platforms.

In contrast, we propose to circumvent these problems by developing a machine-independent framework for analyzing binary codes. The framework will include register transfer lists (RTLs)—a machine-independent, machine-level representation of the effects of instructions—together with machine-independent analyses of code in RTL form.

We are also interested in applying these analyses to the translation of real binary programs on a variety of hardware platforms, including SPARC, x86, and Alpha. We have developed formal descriptions of the syntax and semantics of instructions on the first two platforms, and we plan to use the descriptions to derive the machine-dependent components used to translate between binary codes and RTLs. These automatically generated components will be useful not just in binary translators, but also in other binary manipulation tools, hence making it easier to port them to other architectures.

In the long term, we expect this framework to enable the development of new analyses to help improve the quality of automatically translated code.

This report attempts to document the design and implementation of **UQBT**, the University of Queensland Binary Translation framework, a retargetable translator for multiplatform operating systems.

We *tried* to keep this document up to date. It has been written throughout the last few years, some chapters are more up-to-date than others.

## Acknowledgments

This work has been possible thanks to funding from the Australian Research Council (ARC Grant No.A49702762, 1997-99), Sun Microsystems Laboratories (Sponsored by Neil Wilhelm and Mario Wolczko, 1996-2001), and The University of Queensland (Grant No.97/UQNSRG009G, 1997).

## **Contents**

| 1 | Hov           | v to Read this Book                                                | 21 |  |  |  |  |

|---|---------------|--------------------------------------------------------------------|----|--|--|--|--|

|   | 1.1           | The UQBT Frameworks                                                | 21 |  |  |  |  |

|   |               | 1.1.1 The Proposed 1997 UQBT Framework                             | 21 |  |  |  |  |

|   |               | 1.1.2 The 1999 UQBT Framework                                      | 23 |  |  |  |  |

|   |               | 1.1.3 The 2001 UQBT Framework                                      | 23 |  |  |  |  |

|   | 1.2           | Roadmap                                                            | 24 |  |  |  |  |

| Ι | Int           | croduction                                                         | 27 |  |  |  |  |

| 2 | Bina          | Binary Translation                                                 |    |  |  |  |  |

|   | 2.1           | Is Binary Translation the Solution to all Migration Problems?      | 29 |  |  |  |  |

|   | 2.2           | Goals and Objectives                                               | 31 |  |  |  |  |

|   | 2.3           | Types of Binary Translation                                        | 31 |  |  |  |  |

|   |               | 2.3.1 Static binary translation                                    | 32 |  |  |  |  |

|   |               | 2.3.2 Dynamic binary translator                                    | 33 |  |  |  |  |

| 3 | Previous Work |                                                                    |    |  |  |  |  |

|   | 3.1           | Binary translators and interpreters                                | 35 |  |  |  |  |

|   |               | 3.1.1 List of recent translators                                   | 37 |  |  |  |  |

|   | 3.2           | Binary-code manipulation tools                                     | 38 |  |  |  |  |

| 4 | The           | UQBT Framework                                                     | 41 |  |  |  |  |

|   | 4.1           | The Proposed 1997 Architecture of a Retargetable Binary Translator | 41 |  |  |  |  |

|   |               | 4.1.1 Components                                                   | 42 |  |  |  |  |

|    |      | 4.1.2 Core Translation based on RTLs                    | 44 |

|----|------|---------------------------------------------------------|----|

|    | 4.2  | The 1999 UQBT Framework                                 | 46 |

|    |      | 4.2.1 The Decoding Phase                                | 47 |

|    |      | 4.2.2 The Analysis Phase                                | 47 |

|    |      | 4.2.3 The Encoding Phase                                | 49 |

|    | 4.3  | The 2001 UQBT Framework                                 | 52 |

| II | Tł   | e Frontend                                              | 55 |

| 5  | The  | BinaryFile and ArchiveFile classes                      | 57 |

|    | 5.1  | Related Work                                            | 58 |

|    |      | 5.1.1 GNU's Binary File Descriptor Library              | 58 |

|    |      | 5.1.2 SRL - A Simple Retargetable Loader                | 58 |

|    |      | 5.1.3 Our Approach                                      | 59 |

|    | 5.2  | Binary-file formats                                     | 59 |

|    | 5.3  | The BinaryFile Object Hierarchy                         | 61 |

|    | 5.4  | Interface Functions to Construct and Use a BinaryFile   | 61 |

|    |      | 5.4.1 Construction and Loading                          | 61 |

|    |      | 5.4.2 Sections                                          | 62 |

|    |      | 5.4.3 Symbol Table                                      | 63 |

|    |      | 5.4.4 Relocation Table                                  | 63 |

|    |      | 5.4.5 Program Headers                                   | 64 |

|    |      | 5.4.6 Analysis Functions                                | 64 |

|    | 5.5  | Notes on Individual BinaryFiles                         | 65 |

|    | 5.6  | Interface Functions to Construct and use an ArchiveFile | 66 |

|    | 5.7  | Example Code                                            | 66 |

|    |      | 5.7.1 Example 1                                         | 67 |

|    |      | 5.7.2 Example 2                                         | 67 |

|    |      | 5.7.3 Example 3                                         | 68 |

|    |      | 5.7.4 Compiling and Linking                             | 69 |

| 6  | Dece | ding of Machine Instructions – Syntax Parsing           | 71 |

|    | 6.1  | SLED and Decoding of Machine Instructions               | 71 |

| 8 | Inte | rmediat   | e Representation                                                   | 119 |

|---|------|-----------|--------------------------------------------------------------------|-----|

|   | 7.7  | Implen    | nentation – Semantic Representation Decoder                        | 116 |

|   | 7.6  | SSL Si    | mplifications                                                      | 116 |

|   |      | 7.5.1     | Modelling Higher Order Instructions                                | 114 |

|   | 7.5  | Model     | ling the Semantics of 80286 and SPARC Instruction Sets             | 112 |

|   |      | 7.4.1     | Fetch-Execute Cycle                                                | 112 |

|   | 7.4  | Model     | ling Computer Architecture Features – The Architecture Environment | 110 |

|   |      | 7.3.10    | Parts of a Specification                                           | 110 |

|   |      | 7.3.9     | Instructions                                                       | 109 |

|   |      | 7.3.8     | Tables                                                             | 107 |

|   |      | 7.3.7     | Operands                                                           |     |

|   |      | 7.3.6     | Statements                                                         |     |

|   |      | 7.3.5     | Expressions                                                        |     |

|   |      | 7.3.4     | Functions                                                          | 101 |

|   |      | 7.3.3     | Constants                                                          | 101 |

|   |      | 7.3.2     | Variables and Values                                               | 100 |

|   | , .5 | 7.3.1     | Registers                                                          | 100 |

|   | 7.2  | •         | tic Specification Language Description                             | 99  |

|   | 7.1  | Ü         | er Transfer Lists                                                  | 98  |

| , | 7.1  |           | Decisions                                                          | 97  |

| 7 | Snec | rifyina ( | Semantics of Machine Instructions                                  | 97  |

|   |      | 6.2.6     | Appendix                                                           | 87  |

|   |      | 6.2.5     | Previous Work                                                      | 86  |

|   |      | 6.2.4     | Experimental Results                                               | 85  |

|   |      | 6.2.3     | Our Technique                                                      | 82  |

|   |      | 6.2.2     | Examples of Existing Indexed Jumps in Binary Code                  | 81  |

|   |      | 6.2.1     | Compiler Code Generation for N-Conditional Branches                | 80  |

|   | 6.2  | Recove    | ery of Jump Table Case Statements from Binary Code                 | 79  |

|   |      | 6.1.3     | Cost of Decoding Machine Instructions                              | 79  |

|   |      | 6.1.2     | Decoding Using the New Jersey Machine Code Toolkit                 | 73  |

|   |      | 6.1.1     | SLED Concepts                                                      | 71  |

|    | 8.1  | Regist  | er Transfer Lists                                   | 120 |

|----|------|---------|-----------------------------------------------------|-----|

|    |      | 8.1.1   | Types                                               | 121 |

|    |      | 8.1.2   | Interface Functions to Create and Use RTLs          | 121 |

|    |      | 8.1.3   | Usage of this Interface                             | 128 |

|    | 8.2  | Contro  | ol Flow Graphs                                      | 129 |

|    |      | 8.2.1   | Types of Basic Blocks                               | 130 |

|    |      | 8.2.2   | Abstractions                                        | 130 |

|    |      | 8.2.3   | Steps in Constructing a CFG                         | 131 |

|    |      | 8.2.4   | Interface Functions to Construct Basic Blocks       | 131 |

|    |      | 8.2.5   | Interface Functions to Construct a CFG              | 131 |

|    |      | 8.2.6   | Interface Functions for Analysis Purposes           | 132 |

|    |      | 8.2.7   | Usage of this Interface                             | 132 |

|    | 8.3  | Proced  | lure                                                | 134 |

|    |      | 8.3.1   | Abstractions                                        | 134 |

|    |      | 8.3.2   | Interface Functions to Construct and Use Procedures | 135 |

|    |      | 8.3.3   | Interface Functions for Analysis Purposes           | 136 |

|    |      | 8.3.4   | Usage of this Interface                             | 136 |

|    | 8.4  | Progra  | m                                                   | 137 |

|    |      | 8.4.1   | Abstractions                                        | 137 |

|    |      | 8.4.2   | Interface Functions to Construct and Use Programs   | 137 |

|    |      | 8.4.3   | Usage of this Interface                             | 138 |

|    | 8.5  | High-I  | Level Register Transfer Lists                       | 138 |

| II | I A  | nalysi  | is s                                                | 143 |

| 9  | Mat  | ching ( | Condition Code Uses and Definitions                 | 145 |

|    |      | Ü       | ining Uses and Definitions of Condition Codes       | 147 |

|    |      | 9.1.1   | Conditional branches and set instructions           |     |

|    |      | 9.1.2   | Assignments that use Condition Codes                |     |

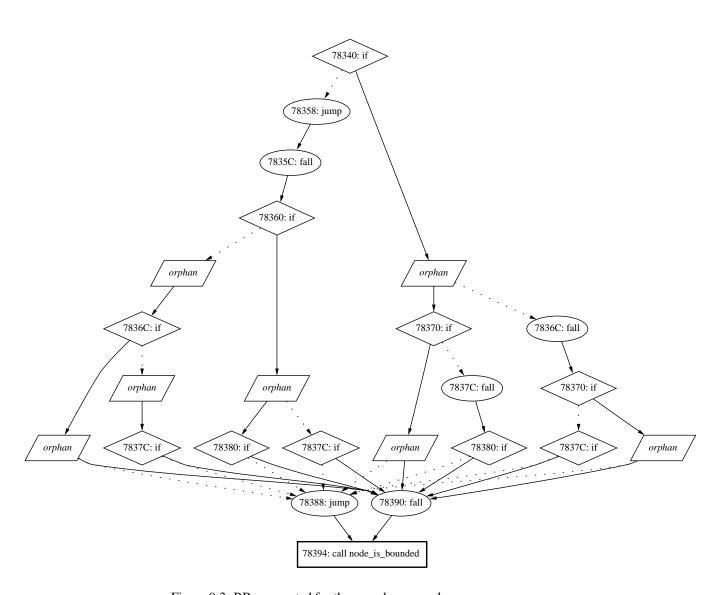

|    | 9.2  |         | lex example                                         |     |

| 10 | Trar | sforma  | ations of Delayed Transfers of Control              | 155 |

|    |      |         | itic framework                                      | 156 |

|    |      | 10.1.1 Register transfer lists                             | 156 |

|----|------|------------------------------------------------------------|-----|

|    |      | 10.1.2 Processor state for delayed branches                | 157 |

|    |      | 10.1.3 A canonical form of RTLs                            | 158 |

|    |      | 10.1.4 Instruction decoding and execution on two platforms | 159 |

|    |      | 10.1.5 Strategy for translating delayed branches           | 160 |

|    | 10.2 | Transforming the execution loop                            | 160 |

|    | 10.3 | Application to the SPARC instruction set                   | 163 |

|    |      | 10.3.1 Classification of SPARC instructions                | 163 |

|    |      | 10.3.2 Derivation of a translator                          | 164 |

|    | 10.4 | Proving Correctness                                        | 170 |

|    | 10.5 | Experience                                                 | 172 |

| 11 | Proc | edure Abstraction Recovery                                 | 175 |

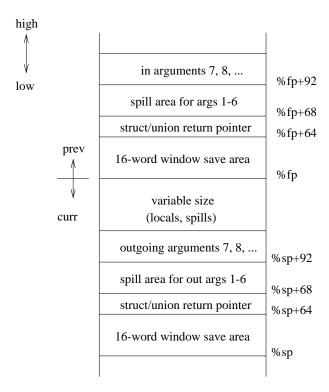

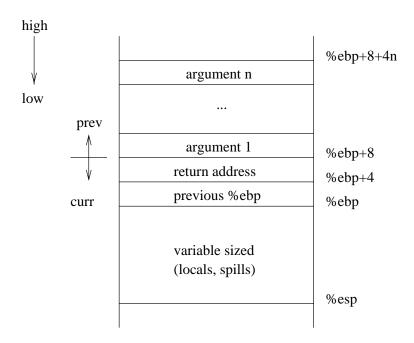

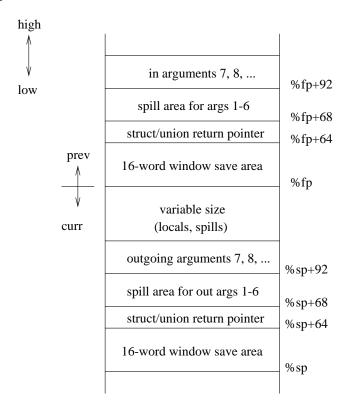

|    | 11.1 | Specifications to Support Procedure Abstraction            | 176 |

|    |      | 11.1.1 Prologues and Epilogues                             | 177 |

|    |      | 11.1.2 Frame Abstraction                                   | 179 |

|    |      | 11.1.3 Local Variables                                     | 180 |

|    |      | 11.1.4 Parameter Locations                                 | 180 |

|    |      | 11.1.5 Return Locations                                    | 182 |

|    |      | 11.1.6 Accesses to a Parent's Stack                        | 183 |

|    |      | 11.1.7 Prologues and Epilogues                             | 183 |

|    |      | 11.1.8 Frame Abstraction                                   | 186 |

|    |      | 11.1.9 Local Variables                                     | 186 |

|    |      | 11.1.10 Parameter Locations                                | 186 |

|    |      | 11.1.11 Return Locations                                   | 187 |

|    |      | 11.1.12 Accesses to a Parent's Stack                       | 188 |

|    | 11.2 | Procedure Abstraction Analysis                             | 188 |

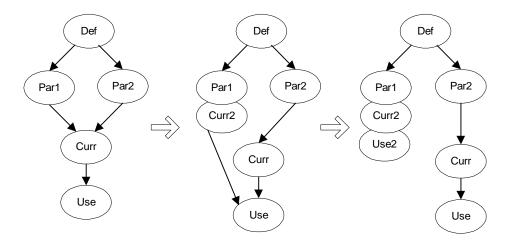

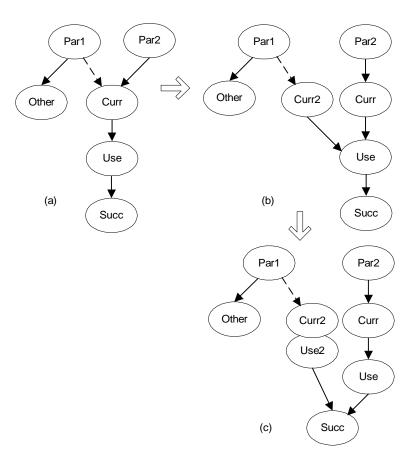

|    |      | 11.2.1 Recovery of Parameters                              | 189 |

|    |      | 11.2.2 Recovery of Return Value                            | 191 |

|    |      | 11.2.3 Issues Relating to Intel Call Signature Analysis    | 191 |

|    | 11.3 | EBNF for the PAL Language                                  | 194 |

|    | 11.4 | Location Sets                                              | 195 |

|    |      | 11.4.1 LocationMap class                                   | 195 |

|    |              | 11.4.2 BitSet class                                  | 195 |

|----|--------------|------------------------------------------------------|-----|

|    | 11.5         | Future Work for Procedure Abstraction Recovery       | 196 |

|    |              | 11.5.1 Pattern Language for Prologues and Epilogues  | 196 |

|    |              | 11.5.2 Local Variables                               | 197 |

|    |              | 11.5.3 Aggregate Types as Parameter and Return Types | 197 |

|    |              | 11.5.4 Implementation                                | 198 |

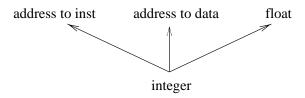

| 12 | Туре         | e Recovery Analysis                                  | 199 |

|    | 12.1         | Type Analysis for Registers                          | 201 |

|    |              | 12.1.1 Collecting Type Information at Decode Time    | 201 |

|    |              | 12.1.2 Determining Live Ranges of Registers          | 201 |

|    |              | 12.1.3 Propagating Type Information                  | 202 |

|    | 12.2         | Type Analysis for Other Memory Locations             | 202 |

|    | 12.3         | Speculative Decoding                                 | 203 |

|    | 12.4         | Register Live Ranges                                 | 203 |

|    | 12.5         | Reaching Definitions                                 | 204 |

|    | 12.6         | Type Recovery Analysis Implementation                | 204 |

|    |              | 12.6.1 Results                                       | 207 |

|    |              | 12.6.2 Future work                                   | 207 |

| IV | <b>у В</b> а | ackends                                              | 209 |

| 13 | The          | C Back End                                           | 211 |

|    | 13.1         | The Current Type and Casting                         | 211 |

|    | 13.2         | Overlapping registers                                | 212 |

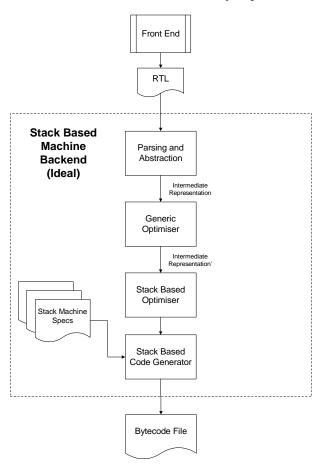

| 14 | The          | JVML Back End                                        | 215 |

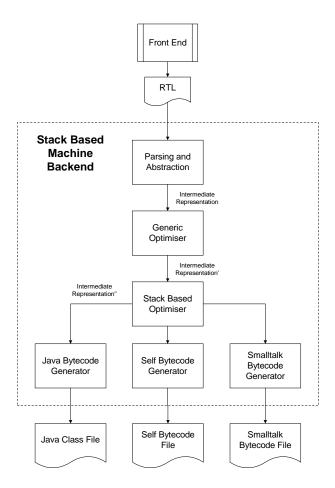

|    | 14.1         | jbmu - A JVM Backend                                 | 215 |

|    |              | 14.1.1 Non-Machine Specific Optimisations            | 216 |

|    |              | 14.1.2 Internal Representations                      | 217 |

|    |              | 14.1.3 Examples                                      | 220 |

|    |              | 14.1.4 The Runtime Environment                       | 223 |

|    |              | 14.1.5 Summary                                       | 224 |

| 14.3.1 Usage of the Java JVM Backend  15.11 Description  15.1.2 Handling expressions  15.1.3 Handling registers  15.1.4 Handling memory  15.1.5 Handling RT assignments  15.1.6 Handling Control Transfer instructions  15.1.7 Processing Frame instructions  15.1.9 Sample Generated Code  15.1.10 RTL Interface  15.1.11 VPOi Interface  15.2.1 Design of the IRTL to VPO backend  15.2.2 Status of the VPO backend  15.2.3 Experience  15.2.4 Lessons  15.2.5 Usage  15.3 The ARM VPO 2001 Back end  15.3.2 Use of the ARM backend  15.3.3 Overview of the ARM VPO backend's operation  15.3.4 Experience  16.3.4 Experience  16.3.5 Experience  16.3.5 Experience  16.1.1 Code Expander - A Retargetable Backend  16.1.1 Code Expander                                                                                                                     |    |      |                                                                  |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|------------------------------------------------------------------|-----|

| 15. The VPO Back End 15.1 The 1998 VPO Back End 15.1.1 Description 15.1.2 Handling expressions 15.1.3 Handling registers 15.1.4 Handling memory 15.1.5 Handling RT assignments 15.1.6 Handling Control Transfer instructions 15.1.7 Processing Frame instructions 15.1.8 Other VPO calls 15.1.9 Sample Generated Code 15.1.10 RTL Interface 15.1.11 VPOi Interface 15.2.1 Design of the IRTL to VPO backend 15.2.2 Status of the VPO backend 15.2.3 Experience 15.2.4 Lessons 15.2.5 Usage 15.3. The ARM VPO 2001 Back end 15.3.2 Use of the ARM VPO backend 15.3.3 Overview of the ARM VPO backend 15.3.4 Experience 15.3.4 Experience 15.3.5 Experience 15.3.5 Use of the ARM VPO backend 15.3.3 Overview of the ARM VPO backend 15.3.4 Experience                                                                                                           |    |      | gcc-jvm - A JVM Backend for the gcc Compiler                     |     |

| 15. The VPO Back End  15.1. The 1998 VPO Back End  15.1.1 Description  15.1.2 Handling expressions  15.1.3 Handling registers  15.1.4 Handling memory  15.1.5 Handling RT assignments  15.1.6 Handling Control Transfer instructions  15.1.7 Processing Frame instructions  15.1.8 Other VPO calls  15.1.9 Sample Generated Code  15.1.10 RTL Interface  15.1.11 VPOi Interface  15.2.1 Initial 2001 Experiments with VPO – Translating IRTL to VPO RTLs  15.2.1 Design of the IRTL to VPO backend  15.2.2 Status of the VPO backend  15.2.3 Experience  15.2.4 Lessons  15.2.5 Usage  15.3 The ARM VPO 2001 Back end  15.3.1 Status of the ARM VPO backend  15.3.2 Use of the ARM VPO backend  15.3.3 Overview of the ARM VPO backend  15.3.4 Experience  16 The Code Expander – A Retargetable Backend  16.1 Design and Implementation  16.1.1 Code Expander |    | 14.3 | The Java JVM Back end                                            | 232 |

| 15.1 The 1998 VPO Back End 15.1.1 Description 15.1.2 Handling expressions 15.1.3 Handling registers 15.1.4 Handling memory 15.1.5 Handling RT assignments 15.1.6 Handling Control Transfer instructions 15.1.7 Processing Frame instructions 15.1.8 Other VPO calls 15.1.9 Sample Generated Code 15.1.10 RTL Interface 15.1.11 VPOi Interface 15.2.1 Initial 2001 Experiments with VPO – Translating IRTL to VPO RTLs 15.2.1 Design of the IRTL to VPO backend 15.2.2 Status of the VPO backend 15.2.3 Experience 15.2.4 Lessons 15.2.5 Usage 15.3 The ARM VPO 2001 Back end 15.3.1 Status of the ARM VPO backend 15.3.3 Overview of the ARM VPO backend 15.3.4 Experience 15.3.4 Experience 15.3.5 Experience 15.3.5 Experience 15.3.6 Experience                                                                                                             |    |      | 14.3.1 Usage of the Java JVM Backend                             | 233 |

| 15.1 The 1998 VPO Back End 15.1.1 Description 15.1.2 Handling expressions 15.1.3 Handling registers 15.1.4 Handling memory 15.1.5 Handling RT assignments 15.1.6 Handling Control Transfer instructions 15.1.7 Processing Frame instructions 15.1.8 Other VPO calls 15.1.9 Sample Generated Code 15.1.10 RTL Interface 15.1.11 VPOi Interface 15.2.1 Initial 2001 Experiments with VPO – Translating IRTL to VPO RTLs 15.2.1 Design of the IRTL to VPO backend 15.2.2 Status of the VPO backend 15.2.3 Experience 15.2.4 Lessons 15.2.5 Usage 15.3 The ARM VPO 2001 Back end 15.3.1 Status of the ARM VPO backend 15.3.3 Overview of the ARM VPO backend 15.3.4 Experience 15.3.4 Experience 15.3.5 Experience 15.3.5 Experience 15.3.6 Experience                                                                                                             | 15 | The  | VPO Back End                                                     | 235 |

| 15.1.1 Description 15.1.2 Handling expressions 15.1.3 Handling registers 15.1.4 Handling memory 15.1.5 Handling RT assignments 15.1.6 Handling Control Transfer instructions 15.1.7 Processing Frame instructions 15.1.8 Other VPO calls 15.1.9 Sample Generated Code 15.1.10 RTL Interface 15.1.11 VPOi Interface 15.2.1 Initial 2001 Experiments with VPO – Translating IRTL to VPO RTLs 15.2.1 Design of the IRTL to VPO backend 15.2.2 Status of the VPO backend 15.2.3 Experience 15.2.4 Lessons 15.2.5 Usage 15.3 The ARM VPO 2001 Back end 15.3.1 Status of the ARM VPO backend 15.3.3 Overview of the ARM VPO backend 15.3.4 Experience 15.3.4 Experience 15.3.5 Experience 15.3.5 Use of the ARM VPO backend 15.3.6 Use of the ARM VPO backend                                                                                                        |    |      |                                                                  | 235 |

| 15.1.2 Handling expressions 15.1.3 Handling registers 15.1.4 Handling memory 15.1.5 Handling RT assignments 15.1.6 Handling Control Transfer instructions 15.1.7 Processing Frame instructions 15.1.8 Other VPO calls 15.1.9 Sample Generated Code 15.1.10 RTL Interface 15.2.1 Initial 2001 Experiments with VPO – Translating IRTL to VPO RTLs 15.2.1 Design of the IRTL to VPO backend 15.2.2 Status of the VPO backend 15.2.3 Experience 15.2.4 Lessons 15.2.5 Usage 15.3 The ARM VPO 2001 Back end 15.3.2 Use of the ARM VPO backend 15.3.3 Overview of the ARM VPO backend 15.3.4 Experience 16 The Code Expander – A Retargetable Backend 16.1.1 Code Expander                                                                                                                                                                                          |    |      |                                                                  |     |

| 15.1.3 Handling registers 15.1.4 Handling memory 15.1.5 Handling RT assignments 15.1.6 Handling Control Transfer instructions 15.1.7 Processing Frame instructions 15.1.8 Other VPO calls 15.1.9 Sample Generated Code 15.1.10 RTL Interface 15.1.11 VPOi Interface 15.2 Initial 2001 Experiments with VPO – Translating IRTL to VPO RTLs 15.2.1 Design of the IRTL to VPO backend 15.2.2 Status of the VPO backend 15.2.3 Experience 15.2.4 Lessons 15.2.5 Usage 15.3 The ARM VPO 2001 Back end 15.3.1 Status of the ARM VPO backend 15.3.2 Use of the ARM VPO backend 15.3.3 Overview of the ARM VPO backend 15.3.4 Experience                                                                                                                                                                                                                               |    |      | •                                                                |     |

| 15.1.4 Handling memory 15.1.5 Handling RT assignments 15.1.6 Handling Control Transfer instructions 15.1.7 Processing Frame instructions 15.1.8 Other VPO calls 15.1.9 Sample Generated Code 15.1.10 RTL Interface 15.1.11 VPOi Interface 15.2.1 Initial 2001 Experiments with VPO – Translating IRTL to VPO RTLs 15.2.1 Design of the IRTL to VPO backend 15.2.2 Status of the VPO backend 15.2.3 Experience 15.2.4 Lessons 15.2.5 Usage 15.3 The ARM VPO 2001 Back end 15.3.1 Status of the ARM VPO backend 15.3.2 Use of the ARM VPO backend 15.3.3 Overview of the ARM VPO backend 15.3.4 Experience 16 The Code Expander – A Retargetable Backend 16.1 Design and Implementation 16.1.1 Code Expander                                                                                                                                                     |    |      |                                                                  |     |

| 15.1.5 Handling RT assignments 15.1.6 Handling Control Transfer instructions 15.1.7 Processing Frame instructions 15.1.8 Other VPO calls 15.1.9 Sample Generated Code 15.1.10 RTL Interface 15.1.11 VPOi Interface 15.2 Initial 2001 Experiments with VPO – Translating IRTL to VPO RTLs 15.2.1 Design of the IRTL to VPO backend 15.2.2 Status of the VPO backend 15.2.3 Experience 15.2.4 Lessons 15.2.5 Usage 15.3 The ARM VPO 2001 Back end 15.3.1 Status of the ARM VPO backend 15.3.2 Use of the ARM VPO backend 15.3.3 Overview of the ARM VPO backend 15.3.4 Experience 16.1 The Code Expander – A Retargetable Backend 16.1 Design and Implementation 16.1.1 Code Expander                                                                                                                                                                            |    |      |                                                                  |     |

| 15.1.6 Handling Control Transfer instructions 15.1.7 Processing Frame instructions 15.1.8 Other VPO calls 15.1.9 Sample Generated Code 15.1.10 RTL Interface 15.1.11 VPOi Interface 15.2 Initial 2001 Experiments with VPO – Translating IRTL to VPO RTLs 15.2.1 Design of the IRTL to VPO backend 15.2.2 Status of the VPO backend 15.2.3 Experience 15.2.4 Lessons 15.2.5 Usage 15.3 The ARM VPO 2001 Back end 15.3.1 Status of the ARM VPO backend 15.3.2 Use of the ARM VPO backend 15.3.3 Overview of the ARM VPO backend 15.3.4 Experience 16 The Code Expander – A Retargetable Backend 16.1.1 Code Expander                                                                                                                                                                                                                                            |    |      |                                                                  |     |

| 15.1.7 Processing Frame instructions 15.1.8 Other VPO calls 15.1.9 Sample Generated Code 15.1.10 RTL Interface 15.1.11 VPOi Interface 15.2 Initial 2001 Experiments with VPO – Translating IRTL to VPO RTLs 15.2.1 Design of the IRTL to VPO backend 15.2.2 Status of the VPO backend 15.2.3 Experience 15.2.4 Lessons 15.2.5 Usage 15.3 The ARM VPO 2001 Back end 15.3.1 Status of the ARM VPO backend 15.3.2 Use of the ARM VPO backend 15.3.3 Overview of the ARM VPO backend's operation 15.3.4 Experience  16 The Code Expander – A Retargetable Backend 16.1.1 Code Expander                                                                                                                                                                                                                                                                             |    |      |                                                                  |     |

| 15.1.9 Sample Generated Code 15.1.10 RTL Interface 15.1.11 VPOi Interface 15.2 Initial 2001 Experiments with VPO – Translating IRTL to VPO RTLs 15.2.1 Design of the IRTL to VPO backend 15.2.2 Status of the VPO backend 15.2.3 Experience 15.2.4 Lessons 15.2.5 Usage 15.3 The ARM VPO 2001 Back end 15.3.1 Status of the ARM VPO backend 15.3.2 Use of the ARM backend 15.3.3 Overview of the ARM VPO backend's operation 15.3.4 Experience  16 The Code Expander – A Retargetable Backend 16.1 Design and Implementation 16.1.1 Code Expander                                                                                                                                                                                                                                                                                                              |    |      | 15.1.7 Processing Frame instructions                             |     |

| 15.1.10 RTL Interface 15.1.11 VPOi Interface 15.2 Initial 2001 Experiments with VPO – Translating IRTL to VPO RTLs 15.2.1 Design of the IRTL to VPO backend 15.2.2 Status of the VPO backend 15.2.3 Experience 15.2.4 Lessons 15.2.5 Usage 15.3 The ARM VPO 2001 Back end 15.3.1 Status of the ARM VPO backend 15.3.2 Use of the ARM backend 15.3.3 Overview of the ARM VPO backend's operation 15.3.4 Experience  16 The Code Expander – A Retargetable Backend 16.1 Design and Implementation 16.1.1 Code Expander                                                                                                                                                                                                                                                                                                                                           |    |      | 15.1.8 Other VPO calls                                           | 237 |

| 15.1.11 VPOi Interface  15.2 Initial 2001 Experiments with VPO – Translating IRTL to VPO RTLs  15.2.1 Design of the IRTL to VPO backend  15.2.2 Status of the VPO backend  15.2.3 Experience  15.2.4 Lessons  15.2.5 Usage  15.3 The ARM VPO 2001 Back end  15.3.1 Status of the ARM VPO backend  15.3.2 Use of the ARM backend  15.3.3 Overview of the ARM VPO backend's operation  15.3.4 Experience  16 The Code Expander – A Retargetable Backend  16.1.1 Code Expander                                                                                                                                                                                                                                                                                                                                                                                    |    |      | 15.1.9 Sample Generated Code                                     | 237 |

| 15.2 Initial 2001 Experiments with VPO – Translating IRTL to VPO RTLs  15.2.1 Design of the IRTL to VPO backend  15.2.2 Status of the VPO backend  15.2.3 Experience  15.2.4 Lessons  15.2.5 Usage  15.3.1 The ARM VPO 2001 Back end  15.3.1 Status of the ARM VPO backend  15.3.2 Use of the ARM backend  15.3.3 Overview of the ARM VPO backend's operation  15.3.4 Experience  16 The Code Expander – A Retargetable Backend  16.1 Design and Implementation  16.1.1 Code Expander                                                                                                                                                                                                                                                                                                                                                                          |    |      | 15.1.10 RTL Interface                                            | 239 |

| 15.2.1 Design of the IRTL to VPO backend  15.2.2 Status of the VPO backend  15.2.3 Experience  15.2.4 Lessons  15.2.5 Usage  15.3 The ARM VPO 2001 Back end  15.3.1 Status of the ARM VPO backend  15.3.2 Use of the ARM backend  15.3.3 Overview of the ARM VPO backend's operation  15.3.4 Experience  16 The Code Expander – A Retargetable Backend  16.1 Design and Implementation  16.1.1 Code Expander                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |      | 15.1.11 VPOi Interface                                           | 240 |

| 15.2.2 Status of the VPO backend  15.2.3 Experience  15.2.4 Lessons  15.2.5 Usage  15.3 The ARM VPO 2001 Back end  15.3.1 Status of the ARM VPO backend  15.3.2 Use of the ARM backend  15.3.3 Overview of the ARM VPO backend's operation  15.3.4 Experience  16 The Code Expander – A Retargetable Backend  16.1 Design and Implementation  16.1.1 Code Expander                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 15.2 | Initial 2001 Experiments with VPO – Translating IRTL to VPO RTLs | 240 |

| 15.2.3 Experience 15.2.4 Lessons 15.2.5 Usage  15.3 The ARM VPO 2001 Back end 15.3.1 Status of the ARM VPO backend 15.3.2 Use of the ARM backend 15.3.3 Overview of the ARM VPO backend's operation 15.3.4 Experience  16 The Code Expander – A Retargetable Backend 16.1 Design and Implementation 16.1.1 Code Expander                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |      | 15.2.1 Design of the IRTL to VPO backend                         | 241 |

| 15.2.4 Lessons 15.2.5 Usage 15.3 The ARM VPO 2001 Back end 15.3.1 Status of the ARM VPO backend 15.3.2 Use of the ARM backend 15.3.3 Overview of the ARM VPO backend's operation 15.3.4 Experience  16 The Code Expander – A Retargetable Backend 16.1 Design and Implementation 16.1.1 Code Expander                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |      | 15.2.2 Status of the VPO backend                                 | 241 |

| 15.2.5 Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |      | 15.2.3 Experience                                                | 242 |

| 15.3 The ARM VPO 2001 Back end  15.3.1 Status of the ARM VPO backend  15.3.2 Use of the ARM backend  15.3.3 Overview of the ARM VPO backend's operation  15.3.4 Experience  16 The Code Expander – A Retargetable Backend  16.1 Design and Implementation  16.1.1 Code Expander                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |      | 15.2.4 Lessons                                                   | 247 |

| 15.3.1 Status of the ARM VPO backend  15.3.2 Use of the ARM backend  15.3.3 Overview of the ARM VPO backend's operation  15.3.4 Experience  16 The Code Expander – A Retargetable Backend  16.1 Design and Implementation  16.1.1 Code Expander                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |      | 15.2.5 Usage                                                     | 247 |

| 15.3.2 Use of the ARM backend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 15.3 | The ARM VPO 2001 Back end                                        | 248 |

| 15.3.3 Overview of the ARM VPO backend's operation 15.3.4 Experience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |      | 15.3.1 Status of the ARM VPO backend                             | 248 |

| 15.3.4 Experience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |      | 15.3.2 Use of the ARM backend                                    | 248 |

| 16 The Code Expander – A Retargetable Backend  16.1 Design and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |      | 15.3.3 Overview of the ARM VPO backend's operation               | 248 |

| 16.1 Design and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |      | 15.3.4 Experience                                                | 249 |

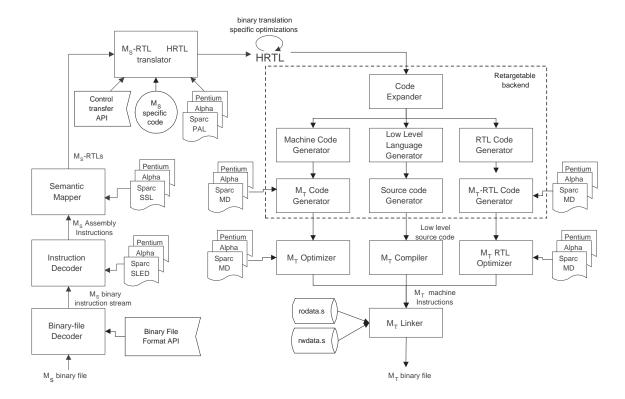

| 16.1 Design and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16 | The  | Code Expander – A Retargetable Backend                           | 251 |

| 16.1.1 Code Expander                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10 |      | -                                                                | 251 |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | 10.1 |                                                                  | 252 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |      | 16.1.2 Code Expander subclasses                                  | 253 |

| 12 | CONTENTS |

|----|----------|

|    |          |

|    | 16.2                  | A SPARC code generator                                                                                                                                                                                                                                                                                                                            | 254                                                                   |

|----|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

|    |                       | 16.2.1 Status                                                                                                                                                                                                                                                                                                                                     | 255                                                                   |

|    |                       | 16.2.2 Example: factorial                                                                                                                                                                                                                                                                                                                         | 255                                                                   |

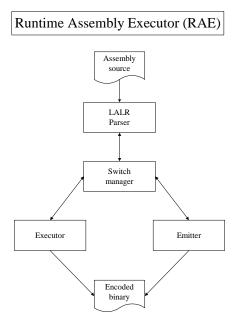

| 17 | Enco                  | oding of Assembly Instructions to Machine Code                                                                                                                                                                                                                                                                                                    | 259                                                                   |

|    | 17.1                  | Design and Implementation                                                                                                                                                                                                                                                                                                                         | 259                                                                   |

|    | 17.2                  | RAE Parser                                                                                                                                                                                                                                                                                                                                        | 260                                                                   |

|    |                       | 17.2.1 Data Segments                                                                                                                                                                                                                                                                                                                              | 261                                                                   |

|    |                       | 17.2.2 Text                                                                                                                                                                                                                                                                                                                                       | 263                                                                   |

|    |                       | 17.2.3 Others                                                                                                                                                                                                                                                                                                                                     | 263                                                                   |

|    | 17.3                  | RAE emitter                                                                                                                                                                                                                                                                                                                                       | 264                                                                   |

|    |                       | 17.3.1 NJMC toolkit                                                                                                                                                                                                                                                                                                                               | 264                                                                   |

|    | 17.4                  | RAE executor                                                                                                                                                                                                                                                                                                                                      | 264                                                                   |

|    | 17.5                  | On-demand                                                                                                                                                                                                                                                                                                                                         | 264                                                                   |

|    |                       |                                                                                                                                                                                                                                                                                                                                                   |                                                                       |

| V  | Re                    | sults                                                                                                                                                                                                                                                                                                                                             | 267                                                                   |

|    |                       |                                                                                                                                                                                                                                                                                                                                                   |                                                                       |

| 18 | Resu                  | ults                                                                                                                                                                                                                                                                                                                                              | 269                                                                   |

|    |                       | antiation of Translators                                                                                                                                                                                                                                                                                                                          | <ul><li>269</li><li>273</li></ul>                                     |

|    | Insta                 |                                                                                                                                                                                                                                                                                                                                                   | 273                                                                   |

|    | Insta                 | antiation of Translators                                                                                                                                                                                                                                                                                                                          | <b>273</b> 274                                                        |

|    | Insta                 | antiation of Translators  Instantiating a New Front-end                                                                                                                                                                                                                                                                                           | <ul><li>273</li><li>274</li><li>274</li></ul>                         |

|    | Insta                 | Instantiation of Translators  Instantiating a New Front-end                                                                                                                                                                                                                                                                                       | <ul><li>273</li><li>274</li><li>274</li><li>275</li></ul>             |

|    | <b>Insta</b><br>19.1  | Instantiating a New Front-end                                                                                                                                                                                                                                                                                                                     | <ul><li>273</li><li>274</li><li>274</li><li>275</li><li>276</li></ul> |

|    | <b>Insta</b><br>19.1  | Instantiating a New Front-end                                                                                                                                                                                                                                                                                                                     | 273<br>274<br>274<br>275<br>276<br>277                                |

|    | <b>Insta</b><br>19.1  | Instantiating a New Front-end                                                                                                                                                                                                                                                                                                                     | 273 274 274 275 276 277                                               |

|    | <b>Insta</b><br>19.1  | Instantiation of Translators  Instantiating a New Front-end  19.1.1 Binary-file Decoder Support  19.1.2 Instruction Decoding Support  19.1.3 Instruction Semantics Support  Instantiating to HRTL Level  19.2.1 Control Transfer Support                                                                                                          | 273<br>274<br>274<br>275<br>276<br>277<br>277                         |

|    | Insta<br>19.1<br>19.2 | Instantiating a New Front-end  19.1.1 Binary-file Decoder Support  19.1.2 Instruction Decoding Support  19.1.3 Instruction Semantics Support  Instantiating to HRTL Level  19.2.1 Control Transfer Support  19.2.2 Procedural Abstraction Support                                                                                                 | 273 274 274 275 276 277 277 277                                       |

|    | Insta<br>19.1<br>19.2 | Instantiating a New Front-end  19.1.1 Binary-file Decoder Support  19.1.2 Instruction Decoding Support  19.1.3 Instruction Semantics Support  Instantiating to HRTL Level  19.2.1 Control Transfer Support  19.2.2 Procedural Abstraction Support  19.2.3 Machine-specific Support                                                                | 273 274 274 275 276 277 277 277 278                                   |

|    | Insta<br>19.1<br>19.2 | Instantiating a New Front-end  19.1.1 Binary-file Decoder Support  19.1.2 Instruction Decoding Support  19.1.3 Instruction Semantics Support  Instantiating to HRTL Level  19.2.1 Control Transfer Support  19.2.2 Procedural Abstraction Support  19.2.3 Machine-specific Support  Instantiating a New Back-end                                  | 273 274 274 275 276 277 277 277 278 279                               |

| 19 | Insta<br>19.1<br>19.2 | Instantiating a New Front-end  19.1.1 Binary-file Decoder Support  19.1.2 Instruction Decoding Support  19.1.3 Instruction Semantics Support  Instantiating to HRTL Level  19.2.1 Control Transfer Support  19.2.2 Procedural Abstraction Support  19.2.3 Machine-specific Support  Instantiating a New Back-end  19.3.1 Translation via RTL code | 273 274 274 275 276 277 277 277 278 279                               |

|    |       | 20.1.1 Development of the Framework                                       | 281               |

|----|-------|---------------------------------------------------------------------------|-------------------|

|    |       | 20.1.2 Reuse of the Framework—Low Cost                                    | 282               |

|    |       | 20.1.3 Endianness                                                         | 282               |

|    | 20.2  | Experiences with Translation to Bytecodes of the Java Platform            | 283               |

|    | 20.3  | Experiences in Instantiating a Palm Translator                            | 283               |

|    |       | 20.3.1 Instantiating a UQBT front end for mc68328 Palm binaries           | 284               |

|    |       | 20.3.2 Using UQBT back ends to translate mc68328 Palm binaries to the ARM | 285               |

| 21 | Debu  | ugging                                                                    | 293               |

|    | 21.1  | Simple debugging techniques                                               | 293               |

|    | 21.2  | How to view the contents of a register transfer                           | 293               |

|    | 21.3  | How to step through a binary with no debug symbols                        | 294               |

|    | 21.4  | Debugging in parallel - source and target binaries                        | 295               |

|    | 21.5  | Other tips                                                                | 296               |

|    | 21.6  | Current known problems                                                    | 296               |

|    |       |                                                                           |                   |

| V  | I R   | untime Support                                                            | 299               |

| 22 | Inter | rpreter                                                                   | 301               |

|    | 22.1  | Interpreter Design                                                        | 301               |

|    |       | 22.1.1 Virtual Machine Design                                             | 302               |

|    |       | 22.1.2 Class Interface                                                    | 302               |

|    |       | 22.1.3 Remaining Work                                                     | 302               |

|    |       | 22.1.4 Other Approaches                                                   | 303               |

| V  | II A  | Appendix                                                                  | 305               |

|    |       |                                                                           | 20-               |

| A  |       | figuring UQBT                                                             | 307               |

|    | A.1   | Compilers and Tools Needed to build UQBT                                  | 307               |

|    |       | ·                                                                         |                   |

|    |       | A.1.1 Special tools needed to build UQBT                                  | 307               |

|    |       | A.1.1 Special tools needed to build UQBT                                  | 307<br>308        |

|    | A.2   | A.1.1 Special tools needed to build UQBT                                  | 307<br>308<br>309 |

| 14 | CONTENTS |

|----|----------|

|    |          |

| Referen | References                           |     |  |  |  |  |  |

|---------|--------------------------------------|-----|--|--|--|--|--|

| A.7     | Generating and Running Disassemblers | 316 |  |  |  |  |  |

| A.6     | Regression Testing                   | 316 |  |  |  |  |  |

| A.5     | UQBT Options                         | 315 |  |  |  |  |  |

|         | A.4.1 Generating JVM files           | 313 |  |  |  |  |  |

| A.4     | Running the Translator               | 311 |  |  |  |  |  |

|         | A.3.2 Warnings from the make         | 311 |  |  |  |  |  |

|         | A.3.1 Dependencies and "make depend" | 311 |  |  |  |  |  |

|         |                                      |     |  |  |  |  |  |

## **List of Figures**

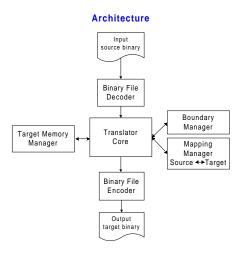

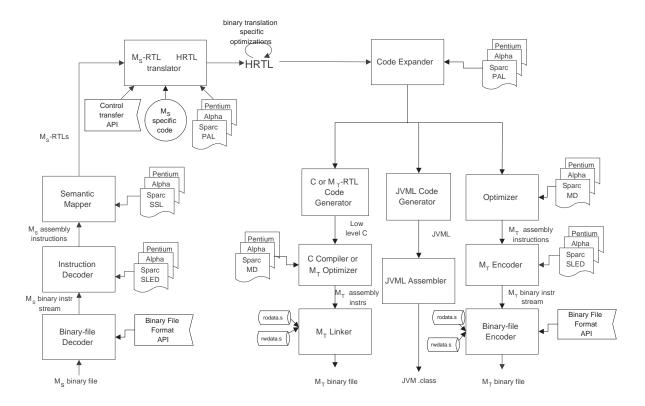

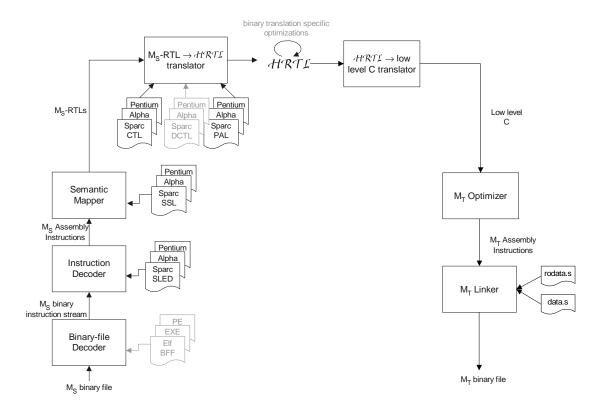

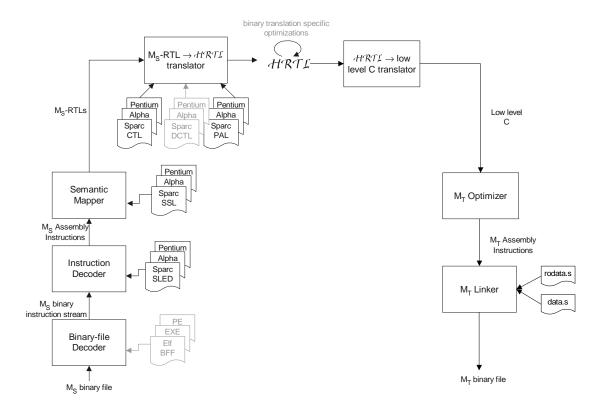

| 1.1 | The Proposed 1997 Architecture for UQBT                                                                                                                     | 22 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

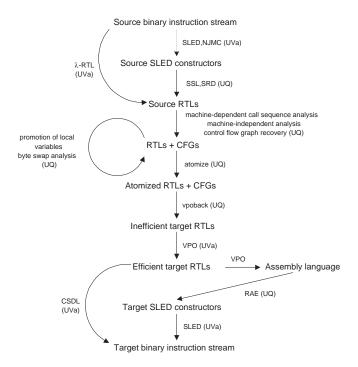

| 1.2 | The Proposed 1997 UQBT Framework                                                                                                                            | 22 |

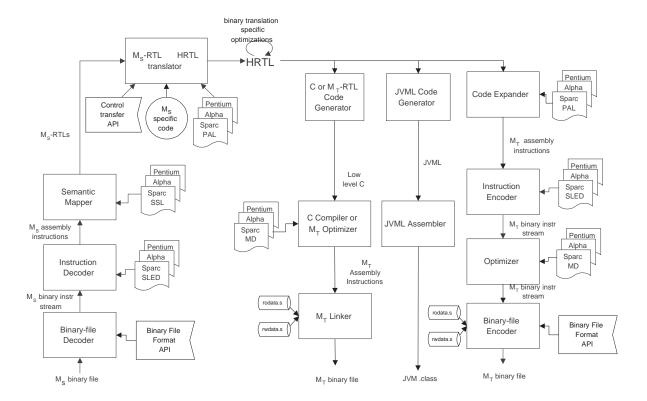

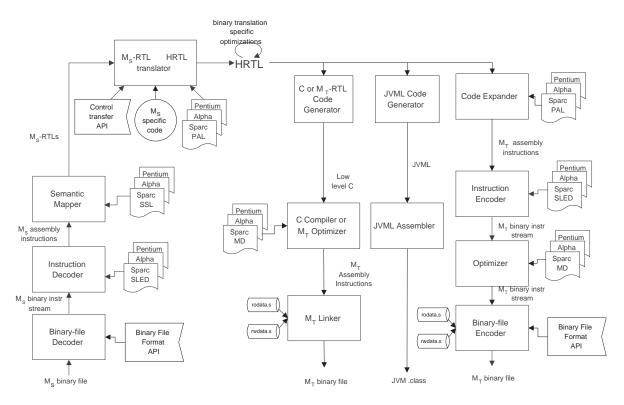

| 1.3 | The 1999 UQBT Framework                                                                                                                                     | 23 |

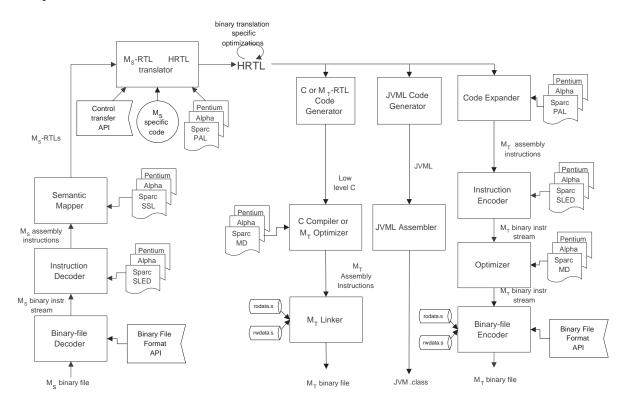

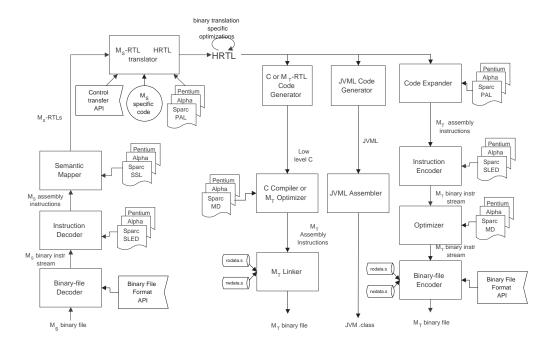

| 1.4 | The 2001 UQBT Framework                                                                                                                                     | 24 |

| 1.5 | The Ideal Framework                                                                                                                                         | 25 |

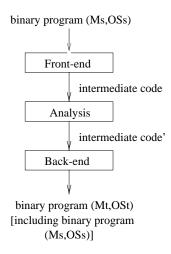

| 2.1 | Structure of a static binary translator for source machine $M_s$ , target machine $M_t$ , source operating system $OS_s$ and target operating system $OS_t$ | 32 |

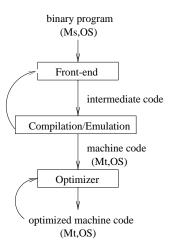

| 2.2 | Structure of a dynamic binary translator for a source machine Ms, a target machine Mt and a multi-platform operating system OS                              | 34 |

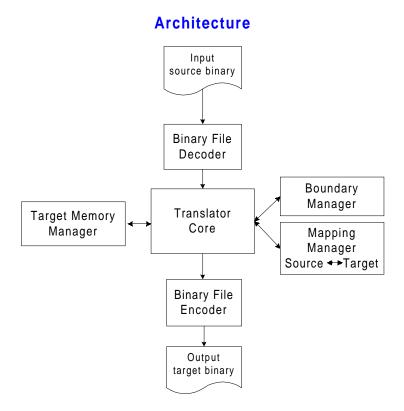

| 4.1 | Architecture for a Retargetable Binary Translator. Components are Represented in Boxes                                                                      | 42 |

| 4.2 | Flow of Data through the System                                                                                                                             | 45 |

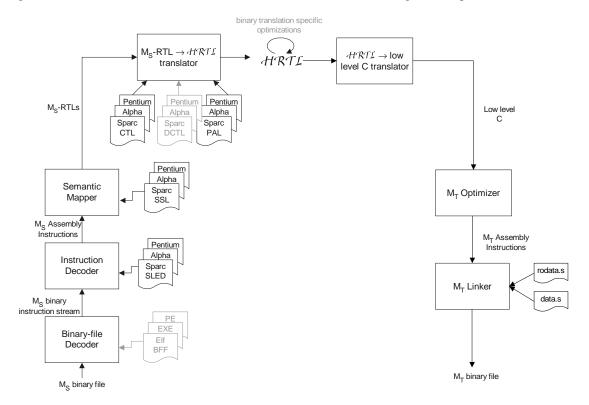

| 4.3 | Framework for a Resourceable Binary Translator                                                                                                              | 48 |

| 4.4 | Example of the result of the use of PAL specifications to translate SPARC-RTL code (left-hand side) to HRTL (right-hand side) in a fibonacci program        | 49 |

| 4.5 | Example generated low-level C code for the partial fibonacci example of Figure 4.4                                                                          | 50 |

| 4.6 | Example of generated bytecode after gcc optimizations (right-hand side) for low-level C code generated from Pentium fibonacci binary (left-hand side)       | 51 |

| 4.7 | The 2001 UQBT Framework                                                                                                                                     | 52 |

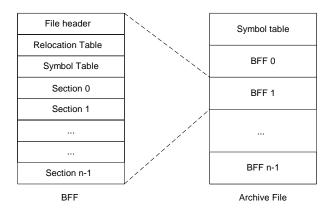

| 5.1 | Binary-File Format Grammar                                                                                                                                  | 59 |

| 5.2 | BFF and archive file abstraction                                                                                                                            | 60 |

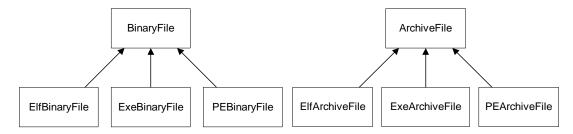

| 5.3 | BinaryFile Class Hierarchy                                                                                                                                  | 61 |

| 6.1 | Partial SLED specification for the SPARC                                                                                                                    | 73 |

| 6.2 | Matching Statement EBNF Specification                                                                                                                       | 74 |

16 LIST OF FIGURES

| 6.3  | Snippet Code for a SPARC Decoder                                                                                                                                                                                                                                       | 76  |  |  |  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|

| 6.4  | Partial SLED Spec for the x86 Instruction Set                                                                                                                                                                                                                          | 78  |  |  |  |  |

| 6.5  | Snippet Code for an x86 Decoder                                                                                                                                                                                                                                        | 88  |  |  |  |  |

| 6.6  | Sample switch program written in the C language                                                                                                                                                                                                                        | 89  |  |  |  |  |

| 6.7  | Pentium assembly code for sample switch program, produced by the Sun cc compiler                                                                                                                                                                                       | 89  |  |  |  |  |

| 6.8  | SPARC assembly code for sample switch program, produced by the Sun cc compiler 9                                                                                                                                                                                       |     |  |  |  |  |

| 6.9  | SPARC assembly code from the vi program, produced by the Sun cc version 2.0.1 compiler.                                                                                                                                                                                |     |  |  |  |  |

| 6.10 | Pentium assembly code from the m88ksim program, produced by the Sun cc version 4.2 compiler                                                                                                                                                                            | 92  |  |  |  |  |

| 6.11 | C source code for example in Figure 6.10                                                                                                                                                                                                                               | 92  |  |  |  |  |

| 6.12 | Normal forms for n-conditional code after analysis                                                                                                                                                                                                                     | 93  |  |  |  |  |

| 6.13 | Number of indexed jumps for SPARC benchmark programs                                                                                                                                                                                                                   | 93  |  |  |  |  |

| 6.14 | Number of indexed jumps for Pentium benchmark programs                                                                                                                                                                                                                 | 93  |  |  |  |  |

| 6.15 | Coverage of code for SPARC benchmarks                                                                                                                                                                                                                                  | 94  |  |  |  |  |

| 6.16 | Coverage of code for Pentium benchmarks                                                                                                                                                                                                                                | 94  |  |  |  |  |

| 6.17 | Form O example for SPARC assembly code                                                                                                                                                                                                                                 | 95  |  |  |  |  |

| 6.18 | Form O example for SPARC assembly code (vi 2.5) using position independent code. Offsets are relative to the address of the call instruction                                                                                                                           | 95  |  |  |  |  |

| 6.19 | A different form O example for SPARC assembly code, also using position independent code. This code is generated from the same source code as the example in Figure 6.18, but with a different version of the compiler. Offsets are relative to the start of the table | 96  |  |  |  |  |

| 7.1  | Expression Operators in the SSL Language                                                                                                                                                                                                                               | 104 |  |  |  |  |

| 7.2  | SSL definition of the arithmetic and logical instruction from the 80286 architecture $\ \ldots \ \ldots$                                                                                                                                                               | 113 |  |  |  |  |

| 7.3  | SSL definition of the load double word instructions from the SPARC architecture $\ \ldots \ \ldots$                                                                                                                                                                    | 113 |  |  |  |  |

| 7.4  | SSL Specification for Rotates in the 80286                                                                                                                                                                                                                             | 114 |  |  |  |  |

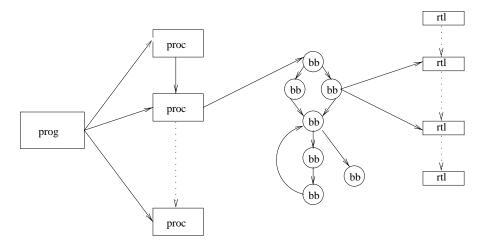

| 8.1  | Data Structures to Represent a Binary Program                                                                                                                                                                                                                          |     |  |  |  |  |

| 8.2  | Expression Operators for RTL (cont over page)                                                                                                                                                                                                                          | 140 |  |  |  |  |

| 8.3  | Expression Operators for RTL (cont from prev page)                                                                                                                                                                                                                     | 141 |  |  |  |  |