### University of Edinburgh

## **Department of Computer Science**

# A Model of Register Transfer Systems with Applications to Microcode and VLSI correctness

by Mike Gordon

Internal Report

CSR-82-81

James Clerk Maxwell Building, The King's Buildings, Mayfield Road, Edinburgh, EH9 3JZ. March, 1981 Revised May, 1982 Corrected version of Department of Computer Science Internal Report CSR-82-81, University of Edinburgh.

# A MODEL OF REGISTER TRANSFER SYSTEMS WITH APPLICATIONS TO MICROCODE AND VISI CORRECTNESS

#### Mike Gordon

Computer Laboratory, University of Cambridge Corn Exchange Street, Cambridge CB2 3QG, UK

#### Abstract

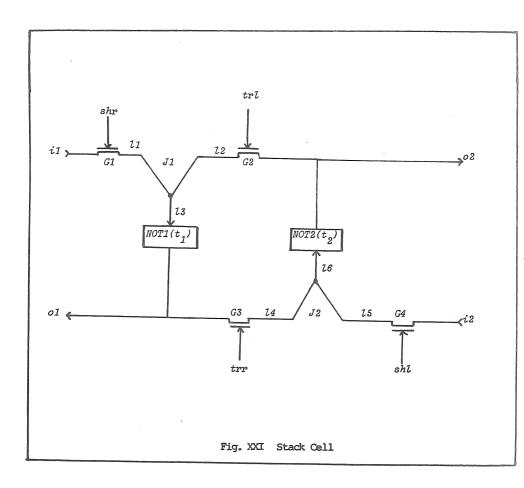

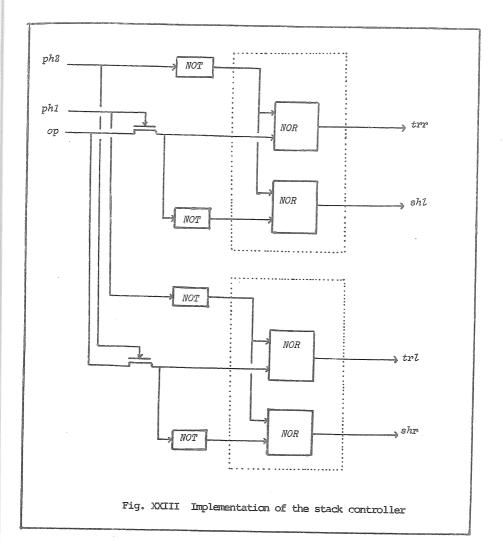

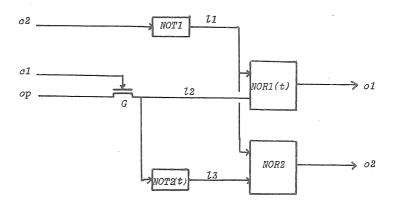

In this paper we describe and illustrate a simple semantic model of register transfer systems - i.e. systems built by connecting together storage devices like registers and memories via combinational circuits like gates and arithmetic units. The goal is to develop an elegant and efficient framework in which to conduct correctness proofs. After explaining the model we illustrate our methods by presenting two case studies. In the first of these we completely specify a small general purpose computer, and then prove correct a microcoded implementation. This involves showing that the signals generated by the microprogrammed controller cause register transfers in the host which correctly fetch, decode and execute machine instructions; and also that the control unit correctly interprets and sequences microinstructions according to the microcode semantics. In the second case study we go down a level and verify nMOS implementations of devices like those used to build the computer. Starting from four primitives - gates, joins, pullups and ground - we first implement and verify not and nor elements. Using these we then specify, implement and verify a stackcell and controller taken from Mead and Conway's book "Introduction to VLSI Systems". In both case studies the proofs are highly structured. For example, in the nMOS study the stack controller is expressed as the composition of two subsystems and a clock, and its correctness follows from the correctness of the subsystems; the correctness of these, in turn, follows from the correctness of their immediate constituents (not and nor elements). It is not necessary to flatten down to the gate level and hence proofs do not explode in size.

N.B. I would be very grateful for any comments and advice on the work reported here. Please write to me at the Computer Laboratory, Cambridge.

#### Introductory Overview

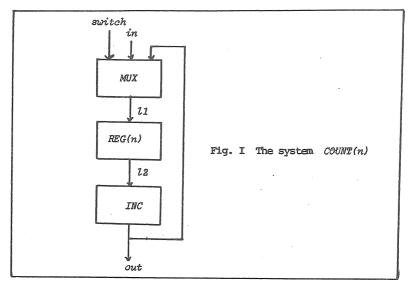

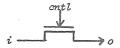

A typical register transfer system is shown in Fig.I

The complete system COUNT(n) is composed out of three components MUX, REG(n) and INC. MUX and INC are combinational devices; the value on the output line is a function of the values on the input lines. We abstract away from the finite delay present in practice. The value on the output line l1 of MUX is either the value on the input line in, if true is the value on the input line switch, or it is the value on the input line out if false is the value on switch. The value on the output line out of INC is one plus the value on its input line l2.

REG(n) is a sequential device. It behaves like a state machine which changes state when signalled to do so by the clock. In a state in which the device is storing the value n it outputs n on to the output line l2; when the system is clocked the value on the input line l1 is stored, overwriting the previous value.

Suppose we put true on line switch and  $\theta$  on line in, then  $\theta$  will be on line l1 and so if we clock the system  $\theta$  will be stored in the register. We

express this by saying COUNT(n) becomes  $COUNT(\theta)$ . If we now put false on line switch then the value on l1 will be the value on out which is one plus the value on l2 which is the value stored - i.e. we will have 0,1,1 on lines l2,out and l1 respectively. Thus if we clock the system it becomes COUNT(1). Clearly, successively clocking the system whilst keeping false on line switch will cause the system to become COUNT(2), COUNT(3) ...

In this paper we explain a notation for representing and verifying both specifications and implementations of register transfer systems. This notation is based on the  $\lambda$ -calculus and is interpreted within the theory of domains developed by Dana Scott [11]. However, to make what follows accessible to as wide an audience as possible, we do not assume knowledge of this theory. In the next section we explain everything that we need.

#### Technical Preliminaries

$\{x \mid \dots x \dots \}$  denote the set of all x such that  $\dots x \dots$  is true;  $\{\}$  denotes the empty set;  $S \cup S'$ ,  $S \cap S'$  and S - S' denote respectively the union, intersection and difference of the sets S and S';  $x \in S$  means x is a member of S.

If  $f:S \to S'$  is a function and  $x \in S$  then we write either fx or f(x) for the result of applying f to x. If  $f:S \to S'$  and  $f':S' \to S''$  then  $f' \circ f:S \to S''$  is the functional composition of f and f' defined by  $(f' \circ f)(x) = f'(f(x))$ .

If S and S' are sets then  $S \times S'$  is the set of ordered pairs  $\{(x,y) \mid x \in S \text{ , } y \in S'\}$ . The functions  $fst:(S \times S') \to S$  and  $snd:(S \times S') \to S'$  are defined by:

$$fst(x,y) = x$$

$snd(x,y) = y$

The set of all functions from S to S' is denoted by S + S', thus f: S + S' is equivalent to  $f' \in (S + S')$ . We abbreviate  $S_1 + (S_2 + \ldots + (S_n + S), \ldots)$  by  $S_1 + S_2 + \ldots + S_n + S_n - i$ .e.  $\rightarrow$  associates to the right. If  $f: S_1 + S_2 + \ldots + S_n + S_n - i$  and  $x_i \in S_i$  (for  $1 \le i \le n$ ) then  $fx_1x_2 \ldots x_n$  abbreviates  $((\ldots ((fx_1)x_2), \ldots)x_n) - i$ .e. function application association to the left.

We denote the set of integers by Int and assume the usual operations over them. The set  $\{true, false\}$  of truth values, or booleans, is denoted by Bool. The unary operation 7 and binary operations  $\land$  and  $\lor$  denote negation (not), conjunction (and) and disjunction (or) respectively. We shall sometimes use 1 instead of true and 0 instead of false; it should be clear from context when 0.1 denote integers and when they denote booleans.

If E is some expression which takes values in a set  $S^*$  whenever x takes values in a set S. then  $\lambda x.E$  denotes the function  $f:S \to S^*$  defined by f(x)=E. For example,  $\lambda x.x^2+1$  denotes the function which maps a number to the successor of its square. Such function denoting expressions are called  $\lambda$ -expressions. In  $\lambda x.E$  we call x the bound variable, and E the body. Note that renaming the bound variable of a  $\lambda$ -expression does not alter its meaning; for example,  $\lambda x.x^2+1$  and  $\lambda n.n^2+1$  both denote the same function.

We sometimes denote pairs (x,y) by just x,y - i.e. we omit the brackets. An expression of the form  $\lambda x.E.E^{\dagger}$  means  $\lambda x.(E.E^{\dagger})$  not  $(\lambda x.E).E^{\dagger}$ .

If E is an expression which takes values in S' whenever  $x_i$  takes a value in a set  $S_i$  (for  $1 \le i \le n$ ), then  $\lambda(x_1,\ldots,x_n)$ . E denotes the function  $f:(S_1 \times S_2 \times \ldots \times S_n) \to S'$  defined by  $f(x_1,\ldots,x_n) = E$  and  $\lambda x_1 x_2 \ldots x_n$ . E denotes the function  $f':S_1 \to S_2 + \ldots \to S_n \to S$  defined by  $fx_1 x_2 \ldots x_n \in E$ . For example,  $\lambda(x,y)$  x+y denotes the addition function  $add:(Int \times Int) \to Int$  defined by add(x,y) = x+y, and  $\lambda xy.x+y$  denotes the 'curried' addition function  $add:Int \to (Int \to Int)$  defined by  $addc(x) = \lambda y.x+y$  or equivalently addc x y = x+y. Note that the result of applying addc to an integer is a function – for example, addc 1 is the successor function.

If  $x_1,\ldots,x_n$  are distinct variables and  $E,E_1,\ldots,E_n$  are expressions then let  $\{x_1=E_1,\ldots,x_n=E_n\}$  in E denotes the value of E when each  $x_i$  denotes the value of  $E_i$ . For example, "let  $\{x=1,\ y=2\}$  in x+y" denotes 3. The expression "let  $\{x_1=E_1,\ldots,x_n=E_n\}$  in E" is equivalent to (but often more readable than)  $(\lambda(x_1,\ldots,x_n),E)(E_1,\ldots,E_n)$ .

We shall often want to define functions recursively, for example.  $factorial\ (n) = \text{if } n = 0 \text{ then } I \text{ else } n \times factorial\ (n-1)$  such 'definitions' do not obviously make sense because the thing they purport to define (e.g. the factorial function) is assumed to exist by

the defining expression. We shall give meaning to these definitions via the theory of least fixed points: According to this theory, recursive definitions are equations (analogous to  $x = \frac{1}{2}(x^2+1)$ ) which are taken to define their solutions (just as  $x = \frac{1}{2}(x^2+1)$  defines x to be 1). Unfortunately solutions to recursive function equations may either not exist - for example, there is no  $f:Int \to Int$  such that f(x) = f(x)+1 or may exist, but not be unique; for example, every  $f:Int \rightarrow Int$  satisfies f(x) = f(x). The theory of least fixed points solves these problems by imposing an ordering on functions in such a way that every 'well formed' recursive definition has a least solution. To define this ordering it is required that the ranges of functions be domains - i.e. ordered sets containing a least member 1 and for which every ascending chain has a least upper bound. We shall not assume the reader is familiar with the theory of domains and least fixed points. All that is needed to understand What follows is a willingness to accept recursive definitions as unproblematical. Such definitions can be thought of intuitively as defining the function that would be computed if they were expressed in a programming language such as LISP. The interpretation of the undefined element  $\perp$ is as the 'result' returned by a function when applied to an argument on which it does not terminate. For example if we define f(x) = f(x)+1then this defines f(x)=1 for all x. For this to work we must make Int into a domain by adding 1 to it.

As well as recursively defined functions we will also need recursively defined domains. More specifically if  $\, {\it D} \,$  and  $\, {\it D}^{\, \circ} \,$  are given domains we will use the domain B defined by  $B = D \rightarrow (D' \times B)$  - much of the next section is concerned with motivating this. Technically such domain equations are solved using a beautiful theory developed by Dana Scott [11] a theory that we do not assume the reader is familiar with. Intuitively domains can be thought of as data types, and then recursive domain equations can be thought of as recursive data type definitions. As a first glimpse of how we shall use the recursively defined domain  $\ensuremath{\mathcal{B}}$  to model register transfer systems, note that if  $f \in B$ , then as  $B = D \Rightarrow (D' \times B)$ , we have  $f: D \Rightarrow (D' \times B)$  and hence  $(fst \circ f): D \Rightarrow D'$  $(\varepsilon \cdot d \circ f): D \rightarrow B$ . If we think of B as the set of states of a sequential machine with input alphabet D and output alphabet D' then  $(fst \circ f)$ will turn out to be the output function and  $(snd \circ f)$  the next-state function. This should become clear later, but first we must continue with the technical preliminaries.

Because of our policy of trying to make this paper accessible to readers not familiar with the theory of domains, we shall cmit all proofs which require appeal to this theory. In fact there is absolutely nothing of intrinsic mathematical interest in what follows, and all the omitted proofs are routine applications of standard techniques, although some of them are rather tedious. We shall also sometimes avoid discussing technicalities which arise from the use of domains rather than sets. For instance we will gloss over continuity questions, and the handling of I in our examples. Readers familiar with the necessary theory should easily be able to supply the missing details.

We assume that both *Int* and *Bool* are flat domains (and hence contain  $_{1}$ ), and that the standard operations (=,  $_{7}$ ,  $_{3}$ ,  $_{3}$ ,  $_{3}$ ,  $_{4}$ ,  $_{5}$ ,  $_{5}$ ,  $_{7}$ ,  $_{8}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$ ,  $_{9}$

If D is any domain then the conditional function  $cond_D : Bool \rightarrow (D \times D) \rightarrow D$  is defined by:

$$cond_D t (x,y) = \begin{cases} x & \text{if } t = true \\ y & \text{if } t = false \\ 1 & \text{if } t = 1 \end{cases}$$

Because we use conditionals so much we introduce the special notation (t + x, y) (due to McCarthy) for  $cond_D$  t (x, y). We also write:

$$(t_1 \rightarrow x_1, t_2 \rightarrow x_2, \dots, t_n \rightarrow x_n)$$

to mean  $(t_1 \rightarrow x_1, (t_2 \rightarrow x_2, (\ldots, (t_n \rightarrow x_n, 1), \ldots)))$ . The value of this expression is  $x_i$  if  $t_i$ =true and for all  $j < i, t_j$ =false, and is 1 otherwise.

If  $x_1, \dots, x_n$  are distinct variables and  $E, E_1, \dots, E_n$  are expressions then:

letrec  $\{x_1=E_1,\ldots,x_n=E_n\}$  in E denotes the value of E when each  $x_1,\ldots,x_n$  is defined mutually recursively by the equations  $x_1=E_1,\ldots,x_n=E_n$ . The difference between this and

let  $\{x_1^{=E_1},\ldots,x_n^{=E_n}\}$  in E is that in the former any occurrence of  $x_i$  in an  $E_j$  (where j may, or may not, equal i) is interpreted recursively as referring to  $E_i$ , whereas in the latter such  $x_i$ 's are assumed to be defined in the enclosing context, and are interpreted with respect to this. For example:

let

$$\{y=1\}$$

in letrec  $\{x=y+1,y=2\}$

in  $(x,y)$

denotes the pair (3,2), whereas:

let  $\{y=1\}$

in let  $\{x=y+1, y=2\}$

in(x,y)

denotes the pair (2,2). As another example:

let  $\{f=\lambda x.0\}$

in letrec  $\{f=\lambda x. (x=0 \rightarrow 1, x \times f(x-1))\}$

in f(6)

denotes 6!=720, whereas:

let  $\{f=\lambda x.0\}$

in let  $\{f=\lambda x. (x=0 \rightarrow 1, x \times f(x-1))\}$

in f(6)

denotes  $6 \times ((\lambda x.0)(5)) = 6 \times 0 = 0$ . In the former case the occurrence of f in the right hand side of the equation is interpreted recursively. In the latter case it is interpreted in the enclosing context where it is defined to be  $(\lambda x.0)$ .

In expressions:

let  $\{x_1 = E_1, \dots, x_n = E_n\}$  in E

and

letrec  $\{x_1 = E_1, \dots, x_n = E_n\}$  in E

if any of the  $E_i$  have the form  $\lambda x. E_i{'}$  then we may write  $x_i(x) = E_i{'}$  instead of  $x_i = \lambda x. E_i{'}$  For example:

let  $\{f(x)=0\}$

in letrec  $\{f(x)=(x=0 \rightarrow 1, x \times f(x-1))\}$

in f(6)

This concludes the necessary preliminaries; we can now proceed to our model.

#### The Model

The semantics of a combinational device will be represented by a function from signals to signals, where a signal is just a function from lines to values. Assume we are given a set *Line* of lines, and a domain *Val* of values; variables ranging over *Line* will be written in small italics (e.g. in, switch, 12). For simplicity we shall assume all lines carry values drawn from a single domain - namely *Val*. More generally lines could be typed and only carry values of their associated types. For example, in the system of Fig. 1 the line switch carries values from *Bool*, whilst all

other lines carry values from Int. We shall assume Val contains all the values we need (e.g. integers and truthvalues). The theory that follows routinely extends to encompass differently typed lines.

#### Definition 1

If X is a non-empty subset of Line then the domain Sig[X] is the set  $\{f|f:X+Val\}$  with the pointwise ordering.  $Sig[\{\}]$  is the one element domain, and Sig=Sig[Line]. Members of Sig[X] are called signals. We use the notation  $\{x_1=E_1,\ldots,x_n=E_n\}$  to denote the signal  $s\in Sig[\{x_1,\ldots,x_n\}]$  defined by  $s(x_i)=E_i$  for  $1\leq i\leq n$ .

We also use the notation  $\lambda\{x_1=v_1,\ldots,x_n=v_n\}$ . E, where E is an expression taking values in D, to denote the function  $f:Sig[\{x_1,\ldots,x_n\}]\to D$  defined by:

$$f(s) = \text{let } \{v_1 = s(x_1), \dots, v_n = s(x_n)\} \text{ in } E$$

A very convenient abbreviation of this notation is to write  $\lambda\{x_1,\ldots,x_n\}$ . E for  $\lambda\{x_1=x_1,\ldots,x_n=x_n\}$ . E. In this case we are using the same name for a line and for the variable associated with it to which the incoming value is bound.

#### Example 1

The combinational behaviour of the device INC of Fig. 1 is:

$\lambda\{12=v\}, \{out=v+1\}$

or, equivalently:

$\lambda\{l2\}.\{out=l2+1\}$

The combinational behaviour of MUX of Fig. 1 is:

$\lambda$ {switch, in, out}.{ll=(switch + in, out)}

In general the combinational behaviour of a device whose set of input lines is X and set of output lines is Y is a function from Sig[X] to Sig[Y].

#### Definition 2

The domain Com[X;Y] of combinational behaviours from X to Y is defined by:

$Com[X;Y] = Sig[X] \Rightarrow Sig[Y]$

The semantics of a sequential device with set of input lines X and set of output lines Y is a member of Seq[X;Y] where:

#### Definition 3

The domain Seq[X;Y] of sequential behaviours from X to Y is defined to be the least solution of the domain equation:

$$Seq[X_{\hat{s}}Y] = (Sig[X] \Rightarrow (Sig[Y] \times Seq[X_{\hat{s}}Y]))$$

The idea of sequential behaviours is that a device with semantics  $f \in Seq[X;Y]$  acts like a combinational device with behaviour  $(fst \circ f) \in Com[X;Y]$  until it is clocked, whereupon it changes behaviour to  $(snd(fs)) \in Seq[X;Y]$ , where  $s \in Sig[X]$  is the input signal when the clocking occurs.

To further motivate sequential behaviours consider the sequential machine:

$$\begin{split} &M = (S_{M^0} out_{M^0} next_M) \\ &\text{where } S_M \text{ is the set of states} \\ &\text{and } out_M : Sig[X] \times S_M + Sig[Y] \text{ is the output function} \\ &\text{and } next_M : Sig[X] \times S_M + S_M \text{ is the next-state function.} \end{split}$$

In a state  $x \in S_M$  this machine acts like a combinational device with behaviour  $\lambda_{S,out_M}(s,x)$ . On being clocked with input signal s it moves to state  $next_M(s,x)$ . The sequential behaviour corresponding to machine M is given by the function  $\mathfrak{B}[M]:S_M \to Seq[X;Y]$  defined recursively by:

$$\mathfrak{B}[M]_x = \lambda s. (out_M(s,x), \mathfrak{B}[M](next_M(s,x)))$$

The behaviour of M in state x is  $\mathfrak{B}[M]x$ . This relationship between sequential machines and members of the recursively defined domain Seq[X;Y] derives from Milner's early theory of processes [7]. For further details of the connection see [5].

#### Example 2

The register REG(n) of Fig.I is modelled as a member of  $Seq[\{l1\};\{l2\}]$  by the definition:

$$REG(n) = \lambda \{l1 = v\}. (\{l2 = n\}, REG(v))$$

which is equivalent to the more concise:

$$REG(n) = \lambda\{11\},\{12=n\},REG(11)$$

This corresponds to the machine (Int, out, next) where:

$$out(\{21=n\},n') = \{22=n'\}$$

$next(\{21=n\},n') = n$

At this point the reader might wonder why we use sequential behaviours at all - why not just work with machines? There are two main reasons: (1), when writing specifications it is often natural just to give a desired behaviour, having to give a machine realising this behaviour would lead to overspecification, and (2), if we worked with machines we would have to define some notion of simulation to express what it means for an implementing machine to correctly meet a specification. Such a notion of simulation would be essentially equivalent to equality of behaviour, and we feel that working directly with behaviours (rather than equivalence classes of machines under simulation) leads to a cleaner, more algebraic theory. In fact, at various times during the development of our model, we have tried to eliminate behaviours in favour of machines, in order to avoid having to use the recursive domain equation which defines Seq[X;Y]. We have never succeeded; considerations of elegance and manipulative simplicity have always driven us back to the more abstract notion of behaviour. We hope the two case studies at the end of this paper will justify these remarks.

From the informal description we gave of COUNT(n) of Fig.I we see that its behaviour is given by:

$$COUNT(n) = \lambda \{switch, in\}. \{out = n + 1\}, COUNT(switch \rightarrow in, n + 1\}$$

Fig. II. Behaviour of  $COUNT(n)$

We now show how to write down an expression representing the combination of the components MUX, REG(n) and INC corresponding to Fig. I. We can then prove that this expression denotes the behaviour COUNT(n) defined directly above. This will illustrate (albeit on a completely trivial example) the way we intend to verify register transfer systems: we write down an expression corresponding to the structure of the system being verified, and then show that this has the desired behaviour.

For much of what follows it is convenient to regard combinational devices as degenerate sequential devices - namely sequential devices which never change state.

#### Definition

If  $f \in Com[X;Y]$  define  $seq(f) \in Seq[X;Y]$  recursiyely by:

$$seq(f) = \lambda s. (f(s), seq(f))$$

Thus the combinational component of the sequential behaviour seq(f) is always the same - namely f.

#### Example 3

The combinational behaviour of the device INC of Fig.I is  $\lambda\{l2\}$ ,  $\{out=l2+1\}$ . The sequential behaviour of it is  $seq(\lambda\{l2\},\{out=l2+1\})$  which is equal to  $INC \in Seq[\{l2\};\{out\}]$  defined recursively by:

$$INC = \lambda\{12\}.\{out = 12 + 1\},INC$$

We can now define all three components of the device shown in Fig.I as sequential behaviours:

$$MUX = \lambda \{switch, in, out\}. \{11 = (switch \rightarrow in, out)\}, MUX$$

$$REG(n) = \lambda \{11\}_{s} \{12 = n\}_{s} REG(11)$$

$$INC = \lambda \{12\}. \{out = 12 + 1\}, INC$$

Fig.III. Behaviour of the components of COUNT(n)

From these definitions we see that:

$$\textit{MUX} \in Seq[\{\textit{switch}, \textit{in}, \textit{out}\}; \{\textit{l1}\}]$$

$REG(n) \in Seq[\{11\};\{12\}]$

$INC \in Seq[\{12\}; \{out\}]$

In order to join these three components together to get the device portrayed in Fig.I we must do two things:

- (i) connect together output lines to input lines with the same name,

- (ii) hide the internal lines (out is an output line of the composite device, but neither l1 nor l2 are).

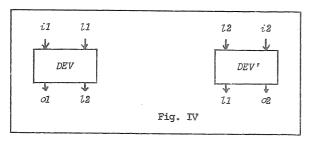

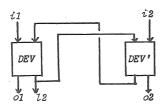

To model (i) we will define for behaviours  $f_1,\dots,f_n$  a composition  $\mathbb{E}[f_1|\dots|f_n]$  which is the behaviour obtained by joining all output lines of  $f_1,\dots,f_n$  to input lines with the same name. For example if f and f' are the behaviours of the devices  $\mathit{DEV}$  and  $\mathit{DEV}'$  shown below

Then [ [f]f'] is the behaviour of

The output lines of  $\mathbb{I} f | f' \mathbb{I}$  are just the output lines of f and f', whilst the input lines are those input lines which are not output lines as well.

If  $f_i \in Seq[X_i;Y_i]$  then  $\mathbb{T}_{f_i}|\dots|f_n]$  is only defined when  $Y_1,\dots,Y_n$  are pairwise disjoint. This is because the semantics of joining two lines depends on what one is modelling. For example, if lines represent wires carrying truthvalues then a join could either be disjunction or conjunction depending on whether one was modelling positive or negative logic. Thus instead of allowing:

we force one to explicitly represent the join with a device; for example, by:

we thus avoid building a fixed meaning of joining into the model.

In our case study on nMOS algorithms we will use a join which is an extended disjunction — extended because it has to cope with a special value representing 'floating'. In contrast to the situation with output lines we do allow devices to share input lines. For example:

A value on a line which forks is just duplicated on to the two outgoing lines.

In summary if  $f_i \in Seq[\mathbb{X}_i; \mathbb{Y}_i]$  and  $\mathbb{Y}_1, \dots, \mathbb{Y}_n$  are pairwise disjoint then we shall define  $[\![f_1]\!] \dots |f_n]\!] \in Seq[\underbrace{\psi\mathbb{X}_i}\!] - \underbrace{\psi\mathbb{Y}_i}\!]$

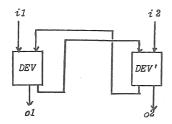

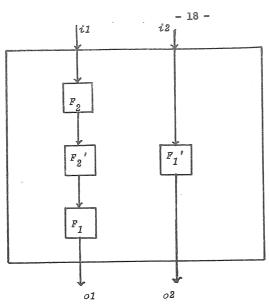

To model the hiding of internal lines ((ii) above), we shall define for each  $l \in Line$  a restriction operator  $\label{line} l : Seq[X;Y] \rightarrow Seq[X;Y-\{l\}]$ . Thus if f and f' represent the behaviour of the devices in Fig. IV, then  $\|f\|f'\| \|l| l$  is the behaviour of:

and  $[f|f'] \ 11 \ 12$  is the behaviour of:

Thus we have:

$$[f|f'] \in Seq[\{i1, i2\}; \{01, 02, 11, 12\}]$$

$$[f|f'] \setminus l1 \in Seq[\{i1, i2\}; \{o1, o2, l2\}]$$

Before defining the exact meaning of composition and restriction in our model we need some definitions.

#### Definition 4

If  $s \in Sig[X]$  and  $s' \in Sig[X']$  then  $s[s'] \in Sig[X \cup X']$  is defined by:

$$s[s'](x) = \begin{cases} s'x & \text{if } x \in X' \\ sx & \text{otherwise} \end{cases}$$

and if  $X \cap X' = \{\}$  we define  $s.s' \in Sig[X \cup X']$  by:

$$s.s'(x) = \begin{cases} s'x & \text{if } x \in X' \\ sx & \text{if } x \in X \end{cases}$$

Intuitively s[s'] is the signal obtained by 'updating' s with the values specified by s', and s.s' is the 'concatenation' of s and s'. It is convenient to have separate notations for these two conceptually distinct operations, although mathematically they are rather similar.

#### Definition 5

If  $s \in Sig[X]$  and  $X' \subseteq Line$  then  $s \mid X' \in Sig[X \cap X']$  is the restriction of s to X'.

#### Definition 6

If  $f_i \in Com[X_i; Y_i]$   $(1 \le i \le n)$  and  $Y_1, \dots, Y_n$  are pairwise disjoint then

define

$$f_1|\dots|f_n\in Com[\begin{tabular}{l} \begin{tabular}{l} \begin{t$$

The expression  $f_1|\dots|f_n$  corresponds to putting  $f_1,\dots,f_n$  side by side but not joining any lines. For example, if f and f' are the behaviours of the devices in Fig. IV then  $f|f'\in Seq[\{i1,l1,l2,i2\};\{o1,l2,l1,o2\}]$  is the behaviour of the device obtained by regarding the two devices in Fig. IV as one.

If f is a combinational behaviour then Definition 7 below defines  $[\![f]\!]$  to be the behaviour obtained by joining input lines of f to output lines with the same name.

For example, if f is the behaviour of:

then [f] would be the behaviour of:

and so  $[f] \setminus i$  would be the behaviour of

#### Definition 7

If  $f \in Com[X;Y]$  define  $[[f]] \in Com[X-Y;Y]$  recursively by:  $[[f]] \cdot s = f(s[[f]] \cdot s)^{1}(X)$

Combining Definition 6 and Definition 7 we see that for combinational behaviours we have defined  $[\![f_1]\!] \dots [\![f_n]\!]$ . We shall extend the definitions to the sequential case shortly, but first we state a lemma which helps to show that it works. In order to state this, and succeeding lemmas, we will abbreviate signal expressions of the form  $\{x_1 = E_1, \dots, x_n = E_n\}$  by  $\{x = E_x | x \in X\}$  where it is understood that  $X = \{x_1, \dots, x_n\}$  and  $E_x = E_i$ . This way of denoting signal expressions enables us to succinctly describe various expression manipulation laws. For example, we can express the fact that if  $S = \{x_1 = E_1, \dots, x_m = E_n\}$  and  $S' = \{x_1' = E_1', \dots, x_n' = E_n'\}$  then  $S = \{x_1 = E_1, \dots, x_m = E_n, x_1' = E_1', \dots, x_n' = E_n'\}$  by the law:

$$\{x \!\!=\!\! E_x \!\mid\! x \in X\}, \{x \!\!=\! E_x \!\!\mid\! x \in X'\} \!\!=\!\! \{x \!\!=\! E_x \!\!\mid\! x \in X \cup X'\} \quad \text{if} \quad X \cap X' \!\!=\!\! \{\}$$

It is such laws which give our model manipulative fluency and enable us to perform proofs by simple calculations.

We will also abbreviate expressions of the form  $\lambda\{x_1,\ldots,x_n\}$ . E by  $\lambda\{x\,|\,x\in X\}$ . E where  $X=\{x_1,\ldots,x_n\}$ . These abbreviations are, I hope, harder to explain than to understand!

#### Lemma 1: The Combinational Composition Lemma

$$\begin{split} & [[\lambda\{x \mid x \in X_{\underline{I}}\}, \{y = E_y \mid y \in Y_{\underline{I}}\}], \dots |\lambda\{x \mid x \in X_n\}, \{y = E_y \mid y \in Y_n\}]] \\ & = & \lambda\{x \mid x \in \bigcup_i X_i \cap \bigcup_i Y_i\}, \\ & \text{letrec } \{y = E_y \mid y \in \bigcup_i X_i \cap \bigcup_i Y_i\} \\ & \text{in} \qquad \{y = E_y \mid y \in \bigcup_i Y_i\} \end{split}$$

#### Example 4

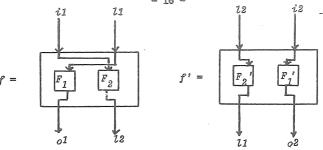

Suppose the behaviour of the devices shown in Fig. IV are:

$$\begin{split} f = & \lambda \{i1, l1\}, \{o1 = F_1(l1), \ l2 = F_2(i1)\} \\ f' = & \lambda \{i2, l2\}, \{o2 = F_1(i2), \ l1 = F_2(i2)\} \end{split}$$

where  $F_1, F_2, F_1', F_2'$ :  $Val \rightarrow Val$ . We might diagram this by drawing the two devices as:

Then by the Combinational Composition Lemma:

$$\begin{split} \mathbb{E}f|f'\mathbb{I} = & \lambda\{i1,i2\}, \\ & \text{letrec } \{l1 = F_2'(l2), \ l2 = F_2(i2)\} \\ & \text{in } \{o1 = F_1(l1), \ l2 = F_2(i2), \ l1 = F_2'(l2), \ o2 = F_1'(i2)\} \\ & = & \lambda\{i1,i2\}, \{o1 = F_1(F_2'(F_2i2)), \ l2 = F_2(i2), \ l1 = F_2'(F_2i2), \ o2 = F_1'(i2)\} \end{split}$$

Thus [f|f'] is the behaviour of:

#### Definition 8

If

$$f \in Com[X,Y]$$

and  $l \in Line$  define  $f \setminus l \in Com[X,Y-\{l\}]$  by:

$$(f \setminus l)s = (fs) \cap Y - \{l\}$$

If

$$L=\{l1,\ldots,ln\}$$

we write  $f\setminus L=f\setminus l1$   $l2\ldots ln=f\setminus l1\setminus l2\ldots\setminus ln$ .

Lemma 2 below shows, among other things, that the order in which one combines devices, and the way one chooses to group them, does not effect the behaviour.

#### Lemma 2

If  $f \in Com[X_i:Y]$ ,  $f_i \in Com[X_i:Y_i]$   $(1 \le i \le n)$  and  $Y_1, \dots, Y_n$  are pairwise disjoint then:

- 1. If  $X \cap Y = \{\}$  then f = [[f]]

- 2. If  $l \notin X \cap Y$  then  $[[f \setminus l]] = [[f]] \setminus l$

- 3.  $f|f_1| \dots |f_n = f|(f_1| \dots |f_n)$

- $\begin{array}{ll} \text{4.} & f_1 | f_2 = f_2 | f_1 \\ \text{5.} & f_1 | (f_2 | f_3) = (f_1 | f_2) | f_3 \end{array}$

The combinational composition theorem below shows the combined effect of composition and restriction.

#### Theorem 1: The Combinational Composition Theorem

$$\begin{split} &\mathbb{E}\,\lambda\{x\,|\,x\in X_{\underline{I}}\},\,\{y=&\overline{\mathcal{E}}_{\underline{y}}\,|\,y\in Y_{\underline{I}}\}\,|\,\dots\,|\,\lambda\{x\,|\,x\in X_{\underline{n}}\},\,\{y=&\overline{\mathcal{E}}_{\underline{y}}\,|\,y\in Y_{\underline{n}}\}\,\underline{\Pi}\,\,\backslash\,L\\ &=&\lambda\{x\,|\,x\in \ \overset{\cup}{\iota}\,X_{\underline{\iota}}-\overset{\cup}{\iota}\,Y_{\underline{\iota}}\},\\ &\text{letrec}\,\,\{y=&\overline{\mathcal{E}}_{\underline{y}}\,|\,y\in \ \overset{\cup}{\iota}\,X_{\underline{\iota}}\ \cap\ \overset{\cup}{\iota}Y_{\underline{\iota}}\}\\ &\text{in}\quad\,\{y=&\overline{\mathcal{E}}_{\underline{y}}\,|\,y\in \overset{\cup}{\iota}Y_{\underline{\iota}}-L\} \end{split}$$

#### Example 5

If f and f' are as in Example 4 then:

$$\begin{split} & \mathbb{E}f|f'\mathbb{I}\setminus l1\ l2\\ &= \lambda\{i1,i2\},\\ & \text{letrec } \{l1=F_2'(l2),\ l2=F_2(i2)\}\\ & \text{in } \{o1=F_1(l2),\ o2=f_1'(i2)\}\\ &= \lambda\{i1,i2\}, \{o1=F_1(F_2'(F_2i1)),\ o2=F_1'(i2)\} \end{split}$$

which is the behaviour of:

We now extend the definitions of composition and restriction to sequential behaviours.

#### Definition 9

If  $f \in Seq[X_i, Y]$ ,  $f_i \in Seq[X_i, Y_i]$ ,  $l \in Line$  and  $Y_1, \dots, Y_n$  are pairwise disjoint, then define:

$$\begin{split} & \text{ If } \mathbf{J} \in Seq[X-Y,Y] \\ & f \backslash l \in Seq[X,Y-\{l\}] \\ & f_1 | \cdots | f_n \in Seq[\underbrace{u^X}_i;\underbrace{u^Y}_i;\underbrace{u^Y}_i] \end{split}$$

by:

$$\begin{split} \mathbb{I}f\mathbb{I} &= \lambda s. \text{ let } \{s' = \mathbb{I}fst \circ f\mathbb{I} \mid s\} \text{ in } (s', \mathbb{I}snd(f(s[s']]X))\mathbb{I} \} \\ f \setminus l &= \lambda s. (fst(fs) \cap Y - \{l\}, (snd(fs)) \setminus l) \\ f_1 \mid \dots \mid f_n = \lambda s. \text{ let} \{s_1 = s \cap X_1, \dots, s_n = s \cap X_n\} \\ &= \inf (fst(f_1 s_1) \circ \dots \circ fst(f_n s_n), snd(f_1 s_1) \mid \dots \mid snd(f_n s_n)) \end{split}$$

where the occurrence of  $\llbracket fst \circ f

rbracket$  in the definition of  $\llbracket f

rbracket$  is as defined in Definition 7. Lemma 2 can now be extended to sequential behaviours.

#### Lemma 3

If  $f \in Seq[X;Y]$ ,  $f_i \in Seq[X_i;Y_i]$   $(1 \le i \le n)$  and  $Y_1, \ldots, Y_n$  are pairwise disjoint then:

- 1. If  $X \cap Y = \{\}$  then f = [[f]]

- 2. If  $l \notin X \cap Y$  then  $[f \setminus l] = [f] \setminus l$

- 3.  $f|f_1|...|f_n = f|(f_1|...|f_n)$

- 4.  $f_1 | \bar{f}_2 = f_2 | f_1$

- 5.  $f_1 | (f_2 | f_3) = (f_1 | f_2) | f_3$

#### Theorem 2: The Composition Theorem

$$\begin{split} & \mathbb{I} \ \lambda \{x \mid x \in X_1\}, (\{y = E_y \mid y \in Y_1\}, E_1\}, \dots, |\lambda \{x \mid x \in X_n\}, (\{y = E_y \mid y \in Y_n\}, E_n\}] \setminus L \\ &= \lambda \{x \mid x \in \bigcup_i i, -\bigcup_i i, i\}, \\ & \text{letrec} \ \{y = E_y \mid y \in \bigcup_i i, \cap \bigcup_i i\}, \\ & \text{in} \qquad (\{y = E_y \mid y \in \bigcup_i i, -L\}, \|E_1\|, \dots, E_n\| \setminus L) \end{split}$$

#### Example 6

Using the Composition Theorem we can derive the behaviour of the device portrayed in Fig. I with components as defined in Fig. III. Putting the components together as in Fig. I corresponds to defining:

(by Composition Theorem)  $= \lambda \{switch, in\}. \{out=n+1\}, \ COUNT(switch \rightarrow in, n+1)\}$

which is precisely the behaviour specified in Fig. II.

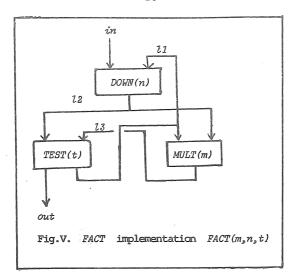

#### Example 7

Consider the system DEV(n, t) shown below:

with components defined by:

$REG(n) = \lambda\{i\}.\{11=n\}, REG(i)$

$ADD = \lambda\{l1, i\}.\{l2=l1+i\}, ADD$

$MUX = \lambda \{12, i, 13\}. \{\phi = (13 + i, 12)\}. MUX$

$NOT = \lambda\{13\}.\{14=713\}, NOT$

$FF(t) = \lambda\{14\}.\{13=t\}, FF(14)$

The whole system has two state variables n and t and is defined by:

$DEV(n,t) = [REG(n)|ADD|MUX|NOT|FF(t)] \setminus 11 12 13 14$

Notice that the devices MUX and REG(n) of this example are different from those of Fig. III since they have differently named lines. A better notation might be something like MUX[switch,in,out;t1], REG[11;t2](n) for the devices of Fig. III, and MUX[13,i,12;o], REG[i;t1](n) for the devices of this example. In fact the correct management of line names, in particular the way behaviour should be parameterised on them, is an important problem which needs care if one is being more formal (e.g. see [6]). However, at the informal level of this paper a fairly casual approach is sufficient.

By the Composition Theorem:

$$\begin{aligned} DEV(n,t) &= \lambda \{i\} \\ &= \text{letrec} \{l1 = n, l2 = l1 + i, l3 = t, l4 = nl3\} \\ &= \text{in } \{o = (l3 + i, l2)\}, DEV(i, l4) \\ &= \lambda \{i\}. \{o = (t + i, n + i)\}, DEV(i, nt) \end{aligned}$$

Let us unfold DEV(n, true) through two clock cycles:

$$DEV(n, true) = \lambda\{i\}.\{o=i\}, DEV(i, false)$$

Now we must be careful in unfolding  $\mathit{DEV}(i,false)$  because if we just substitute i for n then i gets captured by the  $\lambda\{i\}$ . We must thus revert to our less abbreviated notation, viz:

$$DEV(n, true) = \lambda \{i=x\}, \{o=x\}, DEV(x, false)$$

Now we can expand DEV(x, false) as:

$$DEV(x, false) = \lambda \{i=x^i\}. \{o=x+x^i\}, DEV(x^i, true)$$

Hence:

$$\label{eq:defDEV} \begin{split} DEV(n,true) &= \lambda\{i{=}x\}.\{o{=}x\},\lambda\{i{=}x'\}.\{o{=}x{+}x'\}\ ,\ DEV(x',true) \end{split}$$

From this we would expect intuitively that for all  $n.$   $DEV(n,true) = DEV1$

From this we would expect intuitively that for all n. DEV(n, true) = DEV1 where DEV1 is defined by:

$$DEV1 = \lambda \{i=x\}, \{o=x\}, \lambda \{i=x'\}, \{o=x+x'\}, DEV1$$

To prove this we will need a property of sequential behaviours which derives from the fact that Seq[X;Y] is the least solution of its defining domain equation.

This property is conveniently expressed as an 'induction rule' which says that to prove  $F_1(x) = F_2(x)$ , where  $F_1(x)$ ,  $F_2(x)$  are sequential behaviours, it is sufficient to prove for all x and all signals x that:

$$\begin{split} F_1(x)s &= (s', \ F_1(x')) \\ F_2(x)s &= (s', \ F_2(x')) \end{split}$$

for some s' and x' (which may depend on s). More precisely:

#### Theorem 3: Simulation Induction

Let S be a set and  $F_1, F_2: S \to Seq[X;Y]$  then  $F_1 = F_2$  if for all  $x \in S$  and  $s \in Sig[X]$  there exists  $x' \in S$  such that:

(1)

$$fst(F_1(x)s) = fst(F_2(x)s)$$

, and

(2)

$$snd(F_1(x)s) = F_1(x')$$

and  $snd(F_2(x)s) = F_2(x')$

The reason for the name "Simulation Induction" is because if  ${\it F}_1$  and  ${\it F}_2$  are as above, then they give the behaviour of machines which simulate each

other in 'lockstep'. To see this observe that if  $F:S \to Seq[X;Y]$  has the property that for all  $x \in S$ ,  $s \in Sig[X]$  there exists a member of S, f(s,x) say, such that snd(Fxs) = F(f(s,x)), then F = [M] where M = (S, h(x,s), fst(Fxs)), f).

#### Example 8

Let DEV and DEV1 be as in Example 7, i.e.

$$DEV(n, true) = \lambda\{i\}.\{o = i\}, DEV(i, false)$$

$DEV(n, false) = \lambda\{i\}.\{o = n + i\}, DEV(i, true)$

and

$$DEV1 = \lambda \{i = x\}. \{o = x\}, \lambda \{i = x^{\ell}\}. \{o = x + x^{\ell}\}, DEV1$$

We use simulation Induction to show that for all n

$$DEV(n, true) = DEV1$$

To do this let

$$DEV2(n) = \lambda\{i\}.\{o = n + i\}, DEV1$$

so that:

$$DEV1 = \lambda\{i\}.\{o = i\}, DEV2(i)$$

and then define:

$$F(n,t) = t \Rightarrow DEV1, DEV2(n)$$

We then use Simulation Induction to show for all  $\ n,t$  that:

$$DEV(n_s t) = F(n_s t)$$

- (1)  $fst(DEV(n,t)s) = \{o = (t \rightarrow si, n + (si))\}$   $fst(F(n,t)s) = t \rightarrow fst(DEV1s), fst(DEV2(n)s)$   $= t \rightarrow \{o = si\}, \{o = n + (si)\}$  $= \{o = (t \rightarrow si, n + (si))\}$

- (2) snd(DEV(n,t)s) = DEV(s i, t)  $snd(F(n,t)s) = t \Rightarrow snd(DEV1 s i, snd(DEC2(n)s i)$   $= t \Rightarrow DEV2(s i), DEV1$   $= t \Rightarrow DEV2, DEV2(s i)$ = F(s i, t i)

Hence by Simulation Induction DEV(n,t) = F(n,t), and so in particular DEV(n,true) = F(n,true) = DEV1

Suppose we wish to compute some function  $fun: Val \rightarrow Val$ . To do this we could build a device:

with the property that if  $x \in Val$  is put on the input line in, and then the device is clocked time(x) times, where  $time:Val \to Int$ , then fun(x) will appear on the output line out. We might also specify that whilst the device is computing fun(x) it puts some "safe" value  $v \in Val$  on out (e.g. v might correspond to 'high impedance' as in three state busses). The behaviour of such a device would be COMPUTE(fun, time, v) where:

#### Definition 10

If  $fun: Val \rightarrow Val$ ,  $time: Val \rightarrow Int$  and  $v \in Val$  then define  $COMPUTE(fun, time, v) \in Seq[\{in\}; \{out\}]$

by:

$COMPUTE(fun, time, v) = \lambda \{in\}. \{out = v\},$

DELAY(COMPUTE(fun, time, v), v, fun(in), time(in))

where

$\label{eq:deltay} DELAY(b_sv_sx_sn) = (n=0) \Rightarrow (\lambda\{in\},\{out=x\},b), \\ (\lambda\{in\},\{out=v\},DELAY(b_sv_sx_sn-1))$

intuitively  $\mathit{DELAY}(b,v,x,n) \in \mathit{Seq}[\{in\},\{out\}]$  is the behaviour corresponding to outputting v for n clock cycles, then outputting x and then becoming behaviour k

#### Example 9

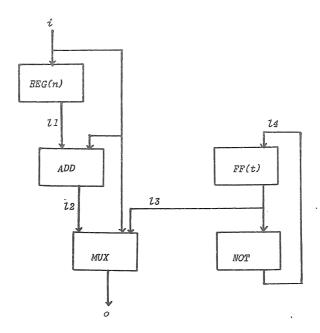

We shall do a top down design and verification of a device to compute fact(n) = n! in n steps.

The specification of our device is that it has behaviour FACT defined by:  $FACT = COMPUTE(fact, (\lambda n, n), 0)$

To implement this we shall use two devices DOWN(n) and MULT(m) for counting down on n and building up the results by multiplication respectively. The operation of these will be controlled by a device TEST(t). Our implementation, obtained by connecting these devices together, is FACTIMP(m,n,t) and is shown in Fig.V. below.

#### FACTIMP(m,n,t) is defined by:

$\mathit{MULT}(m)$  and  $\mathit{DOWN}(n)$  are fairly natural,  $\mathit{TEST}(t)$  required some experimentation before its specification was got right. Before descending a level and implementing these devices we should check that they do lead to a correct implementation of  $\mathit{FACT}$ .

By the Composition Theorem:

$$\begin{split} &FACTIMP(m_sn_st) \\ &= \lambda \{in\} \\ &\quad \text{letrec} \{l1=t_sl2=n_sl3=m\} \\ &\quad \text{in} \{out=((l2=0) \land \exists t+l3,0)\}, FACTIMP((l1+1_sm\times l2l_s(l1+in_sn-1l_s(l2=0) \land \exists t)\}, \\ &\quad \text{in} \{out=(l2=0) \land \exists t+l3,0\}, FACTIMP((l1+1_sm\times l2l_s(l1+in_sn-1l_s(l2=0) \land \exists t)\}, \\ &\quad \text{in} \{out=(l2=0) \land \exists t+l3,0\}, FACTIMP((l1+1_sm\times l2l_s(l1+in_sn-1l_s(l2=0) \land \exists t)\}, \\ &\quad \text{in} \{out=(l2=0) \land \exists t+l3,0\}, FACTIMP((l1+1_sm\times l2l_s(l1+in_sn-1l_s(l2=0) \land \exists t)\}, \\ &\quad \text{in} \{out=(l2=0) \land \exists t+l3,0\}, FACTIMP((l1+1_sm\times l2l_s(l1+in_sn-1l_s(l2=0) \land \exists t)\}, \\ &\quad \text{in} \{out=(l2=0) \land \exists t+l3,0\}, FACTIMP((l1+1_sm\times l2l_s(l1+in_sn-1l_s(l2=0) \land \exists t)\}, \\ &\quad \text{in} \{out=(l2=0) \land \exists t+l3,0\}, FACTIMP((l1+1_sm\times l2l_s(l1+in_sn-1l_s(l2=0) \land \exists t)\}, \\ &\quad \text{in} \{out=(l2=0) \land \exists t+l3,0\}, FACTIMP((l1+1_sm\times l2l_s(l1+in_sn-1l_s(l2=0) \land \exists t)\}, \\ &\quad \text{in} \{out=(l2=0) \land \exists t+l3,0\}, FACTIMP((l1+1_sm\times l2l_s(l1+in_sn-1l_s(l2=0) \land \exists t)\}, \\ &\quad \text{in} \{out=(l2=0) \land \exists t+l3,0\}, FACTIMP((l1+1_sm\times l2l_s(l1+in_sn-1l_s(l2=0) \land \exists t)\}, \\ &\quad \text{in} \{out=(l2=0) \land \exists t+l3,0\}, \\ &\quad \text$$

=  $\lambda \{in\}$ . {out = ( $n = 0 \land \forall t \rightarrow m_2 0$ )}, FACTIMP(( $t \leftrightarrow 1, m \times n$ ), ( $t \leftrightarrow in, n - 1$ ),  $n = 0 \land \forall t$ )

Define:

$$F(m,n,t) = t \rightarrow FACT$$

,  $DELAY(FACT, 0, m \times n!, n)$

Then we show by Simulation Induction that FACTIMP=F and hence for all m and n:

$$FACTIMP(m,n,true) = F(m,n,true) = FACT$$

Thus as long as t is initialised to true it doesn't matter what m and n are initialised to; we still compute FACT.

Case 1: t=true

=

$$\lambda$$

{in}.{out=0}, FACTIMP(1, in, false)

F(m, n, true)

= FACT

=

$$COMPUII(fact_s(\lambda n.n), 0)$$

=

$$\lambda$$

{in}.{out=0}, DELAY(FACT, 0, in!, in)

=

$$\lambda$$

{in}.{out=0},  $F(1, in, false)$

Case 2: t=false

=

$$\lambda \{in\}\{out=(n=0 \rightarrow m, 0)\}$$

, FACTIMP $(m \times n, n-1, n=0)$

F(m, n, false)

$$= DELAY(FACT, 0, m \times n!, n)$$

=

$$n=0 \rightarrow (\lambda \{in\}, \{out=m \times n!\}, FACT), (\lambda \{in\}, \{out=0\}, DELAY(FACT, 0, m \times n!, n-1))$$

=

$$\lambda$$

{in}. {out=(n=0 \rightarrow m, 0)}, (n=0 \rightarrow FACT, DELAY(FACT, 0, m \times n.1, n-1))

=

$$\lambda \{in\}. \{out=(n=0 \rightarrow m, 0)\}, F(m \times n, n-1, n=0)$$

So by Simulation Induction FACTIMP=F

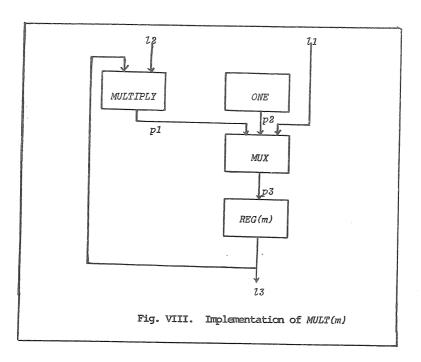

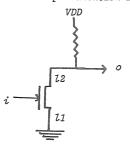

Thus if we implement  $\mathit{MULT}(m)$ ,  $\mathit{DOWN}(n)$  and  $\mathit{TEST}(t)$  to meet the specifications in Fig. VI, then Fig. V gives a correct implementation of  $\mathit{FACT}$ .  $\mathit{MULT}(m)$  can be implemented by:

To model this we define:

$\textit{MULT}(m) = [[\textit{MULTIPLY} | \textit{ONE} | \textit{MUX} | \textit{REG}(m)]] \setminus p1 \ p2 \ p3$

where:

MULTIPLY =  $\lambda\{12,13\}$ ,  $\{p1=12 \times 13\}$ , MULTIPLY ONE =  $\lambda\{\}$ ,  $\{p2=1\}$ , ONE MUX =  $\lambda\{p1,p2,12\}$ ,  $\{p3=(11 \rightarrow p2,p1)\}$ , MUX REG(m) =  $\lambda\{p3\}$ ,  $\{13=m\}$ , REG(p3)

#### By the Composition Theorem:

MULT(m)

$= \lambda \{ 11, 12 \}.$

letrec { $p1=12 \times 13$ , p2=1,  $p3=(11 \rightarrow p2,p1)$ , 13=m} in {13=m}, MULT(p3)

=  $\lambda\{11,12\}$ .  $\{13=m\}$ ,  $MULT(11 \rightarrow 1, m \times 12)$

As required.

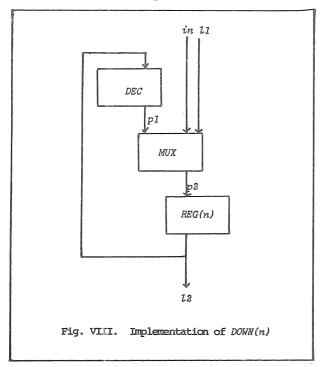

#### DOWN(n) can be implemented by:

To model this we define:

where:

$$\begin{split} DEC &=& \lambda \{12\}, \{p1=&12-1\}, DEC \\ REG(n) &=& \lambda \{p2\}, \{12=&n\}, REG(p2) \\ MUX &=& \lambda \{11, in, p1\}, \{p2=&(11 \rightarrow in, p1)\}, MUX \end{split}$$

#### By the Composition Theorem:

DOWN(n)

=  $\lambda \{in, 11\}$ . letrec  $\{p1=12-1, p2=(11+in, p1), 12=n\}$ in  $\{12=n\}, DOWN(p2)$ =  $\lambda \{in, 11\}, \{12=n\}, DOWN(11+in, n-1)$

As required.

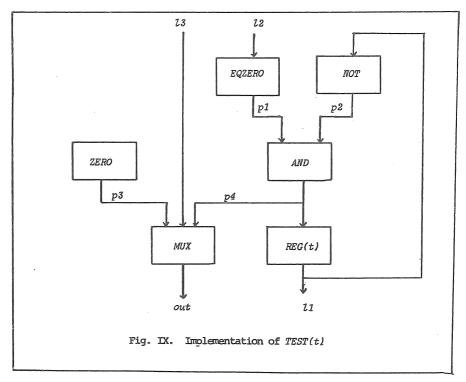

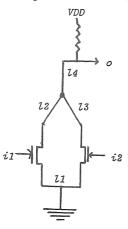

#### Finally TEST(t) may be implemented by:

To model this we define:

$TEST(t) = [[ZERO | EQZERO | NOT | AND | MUX | REG(t)]] \p1 p2 p3 p4$

where:

ZERO =

$$\lambda$$

{}.{p3=0}, ZERO

EQZERO = 1{12}.{p1=(12=0)}, EQZERO

NOT =  $\lambda$ {11}.{p2=\text{11}}, NOT

AND =  $\lambda$ {p1,p2}.{p4=\text{p1}} \text{AND}

MUX =  $\lambda$ {p3,13,p4}.{out=(p4+13,p3)}, MUX

REG(t) =  $\lambda$ {p4}.{11=t}, REG(p4)

By the Composition Theorem:

$$TEST(t) = \lambda\{12,13\}.$$

$$letrec \ \{p1=(12=0), \ p2=\exists 11, \ p3=0, \ p4=p1 \land p2, \ 11=t\}$$

$$in \ \{out=(p4 \Rightarrow 13,p3), \ 11=t\}, \ TEST(p4)$$

$$= \lambda\{12,13\}. \{out=(12=0) \land \exists t \Rightarrow 13,0\}, \ 11=t\}, \ TEST((12=0) \land \exists t\}$$

As required.

We have thus shown that the device specified by FACT is correctly implemented by FACTIMP(m,n,true) as shown in Fig. V, where the components are as specified in Fig. VI, and correct implementation of these components are shown in Fig. VII, Fig. VIII and Fig. IX.

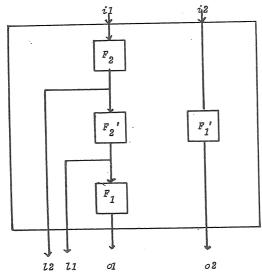

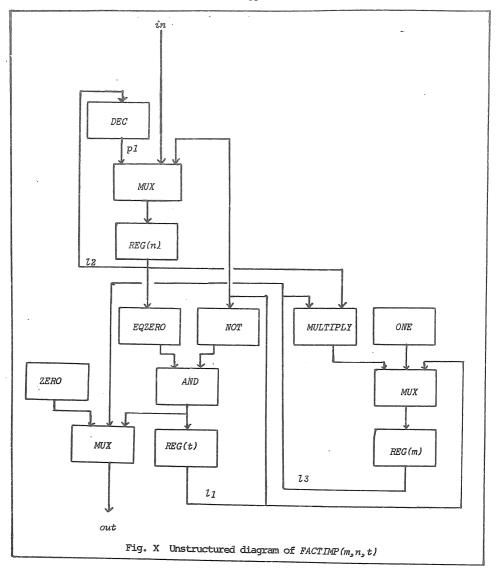

This example illustrates how the verification of large systems can be made tractable. If we remove the structure we imposed on FACTIMP(m,n,t) we get the unintelligible tangle of devices shown in Fig. X below:

By analysing the whole system in terms of the subsystems  $\mathit{MULT}(M)$ ,  $\mathit{DOWN}(n)$  and  $\mathit{TEST}(t)$  we not only made the verification much simpler, but also more robust. For example, if a change is made in a subsystem implementation we need only verify that it meets its specified sub-behaviour (see Fig. VI) - we do not have to repeat the entire proof, as we would if we had based our

analysis on Fig. X rather than Fig. V. The two case studies that follow illustrate this methodology on less trivial examples.

In all our examples so far the correctness of a device has been expressed by asserting that its behaviour should be equal to some specified behaviour. This requires that we fully determine each clock cycle - i.e. the specification and implementation are behaviours which run in 'lockstep'. It is often more natural not to require this, and to allow several 'microcycles' in an implementation to implement a single cycle in the specification. For instance, in our first case study below we will verify a host machine that implements a target machine that fetches, decodes and executes machine code instructions. At the target level fetch-decode-execute will be a single step, but down at the host level each such step will be implemented by several microinstructions and hence take several microcycles. To express the correctness of the host device we cannot simply assert that its behaviour must equal the target behaviour, instead we must first derive from the host's behaviour a 'courser' behaviour in which fetch, decode and execute microcycles are somehow merged into a single cycle, and then it is this derived behaviour which must equal the specified target behaviour. We must thus provide in our model a way of coalescing sequences of clock cycles into single cycles. The intuitive idea of what is needed is most simply explained with respect to machines (see page 8) rather than behaviours.

Suppose we have a machine M = (S, out, next) where S is a set of states and

out :  $Sig[X] \times S \rightarrow Sig[Y]$

$next : Sig[X] \times S \rightarrow S$

are the output and next-state functions respectively. Suppose that this machine implements a 'higher level' machine whose states correspond to some subset  $S' \subseteq S$  - think of states in (S-S') as occurring in the middle of microinstruction sequences. From M it seems natural to derive a new machine  $M + S^1 = (S', out', next')$  where:

$out': Sig[X] \times S' \Rightarrow Sig[Y]$

$next': Sig[X] \times S' \rightarrow S'$

and in which out' is the restriction of out to  $Sig[X] \times S'$  and next'(s,x) is obtained by repeatedly clocking machine M starting in state x and with constant input signal s until a member of S' is reached. Formally:

$$\begin{aligned} &out'(s,x) = out(s,x) \\ &next'(s,x) = (next(s,x) \in S') \rightarrow next(s,x), &next'(s,next(s,x)) \end{aligned}$$

The idea is that given a target specification as a behaviour  $f \in Seq[X;Y]$  we can express correctness by requiring that  $f = \Re [M + S']$ .

Unfortunately this construction of M+S' from M does not respect behaviour in the sense that from  $\mathfrak{B}[M_1] = \mathfrak{B}[M_2]$  it does not necessarily follow that  $\mathfrak{B}[M_1+S'] = \mathfrak{B}[M_2+S']$ . This has the unsatisfactory consequence that replacing a machine  $M_1$  which is correct (in the sense that  $\mathfrak{B}[M+S']$  has a specified behaviour) by a behaviourably identical machine  $M_2$  does not necessarily preserve correctness (since  $\mathfrak{B}[M_2+S']$  might not have the specified behaviour).

#### Example 10

Let

$$M_1 = (S_sout_1, next_1)$$

and  $M_2 = (S_sout_2, next_2)$  where:

$S = Int \times Bool$

$out_1(s, (n, t)) = out_2(s, (n, t)) = \{o = n\}$

$next_1(s, (n, t)) = (n + 1, t)$

$next_2(s, (n, t)) = (n + 1, t)$

Then it it easy to show that

$$\mathfrak{B}[M_1] = \mathfrak{B}[M_2] = \lambda(n,t).F(n)$$

where:  $F(n) = \lambda s. \{o = n\}.F(n+1)$

Now let

$$S' = \{(n,t) \mid t = true\} \subseteq S$$

, then  $M_1 + S' = (S', out'_1, next'_1)$

$M_2 + S' = (S', out'_2, next'_2)$

#### where

$$\begin{aligned} out'_1(s,(n,t)) &= out'_2(s,(n,t)) = \{o = n\} \\ next'_1(s,(n,true)) &= (n+1,true) \\ next'_2(s,(n,true)) &= (n+2,true) \end{aligned}$$

and so  $\mathfrak{B}[M_1 + S'] \neq \mathfrak{B}[M_2 + S'].$

To overcome the problem illustrated in this example we shall define an operation on machines which merges cycles, not on the basis of the states they pass through, but instead on the basis of the output signals produced.

#### Definition 11

Let M (S, out, next) be a machine where:

S is the set of states

out:  $Sig[X] \times S \rightarrow Sig[Y]$  is the output functions

$next: Sig[X] \times S \rightarrow S$  is the next-state function

If  $P:Sig[Y] \rightarrow Bool$  is a predicate on output signals, then define the machine M+P by  $M+P=(S_out_next_p)$  where:

$next_p(s,x) = P(out(s,next(s,x))) \rightarrow next(s,x), \ next_p(s,next(s,x))$

Thus M + P is got from M by changing the next-state function so that it moves to the next state in which the output satisfies P. While this moving is taking place the input signal is held constant.

This definition of M+P has the desirable property that if  $\Re[M_1]=\Re[M_2]$  then  $\Re[M_1+P]=\Re[M_2+P]$ . This follows from the fact that for all x  $\Re[M+P](x)=\Re[M](x)+P$ , where +P is defined on behaviours by.

#### Definition 12

Let  $f \in Seq[X;Y]$ ,  $P:Sig[Y] \rightarrow Bool$ . Define  $f \nmid P \in Seq[X;Y]$  by:

$f \downarrow P = \lambda s. (fst(fs), run P(snd(fs))s + P)$

where run  $Pfs = P(fst(fs)) \rightarrow f$ , run P(snd(fs))s

intuitively  $\operatorname{run} P f s$  moves to the 'nearest' behaviour after f in which the output satisfies P.

#### Theorem 4

For all machines  $M_r$  output predicates P and states x:

$\mathfrak{B}[M \downarrow P](x) = \mathfrak{B}[M](x) \downarrow P$

#### Example 11

Let FACTORIAL be defined by:

$$FACTORIAL(n) = \lambda \{in = x\}, \{out = n\}, FACTORIAL(x.)\}$$

and FACTIMP be as constructed in Example 9, i.e.

$$FACTIMP(m,n,t)$$

$$= \lambda \{in\}, \{out = (n = 0 \land \exists t \rightarrow m, 0)\}, FACTIMP(t \rightarrow (1, in, false), (m \times n, n - 1, n = 0))$$

Then we show that if we define  $P(s) \iff s(out) \neq 0$  then:

$$FACTIMP(m_sn_strue) + P = \lambda\{in\}, \{out = 0\}, FACTORIAL(m_s^*)\}$$

$$FACTIMP(m_sO_sfalse) + P = FACTORIAL(m)$$

This assertion is a weaker specification than the one in Example 9 since we only require that the factorial function is computed in some number of steps - we do not specify the number.

By Simulation Induction it is easy to see that  $FACTIMP = \Re[FACTMACHINE]$

where: FACTMACHINE = (Int x Int x Bool, out, next).

$$out(s_s(m_sn_st)) = \{out = (n = 0 \land \gamma t \rightarrow m_s 0)\}$$

$next(s_s(m_sn_st)) = t \rightarrow (1_s(in)_s false)_s(m \times n_sn - 1_sn = 0)$

Then  $FACTMACHINE + P = (Int \times Int \times Bool, out, next_p)$  where if n > 0:

$$next_p(\{in = x\}, (m, n, false))$$

- =  $next_{p}(\{in=x\}, (m \times n, n-1, false))$

- =  $next_{D}(\{in=x\}, (m \times n \times n 1, n 2, false))$

•

=  $next_{p}(\{in = x\}, (m \times n \times n - 1 \times ... \times 2, 1, falsel))$

=  $(m \times n!, 0, false)$

and hence if x > 0

$$next_p(\{in=x\}, (m,n,true))$$

$= next_{p}(\{in=x\}, (1,x,false))$

= (x!, 0, false)

and so:

$$next_p(\{in=x\},(m,0,false))$$

=  $next_p(\{in=x\},(0,-1,true))$

= $(x!,0,false)$

It follows that:

$\mathfrak{B}$  [ FACTMACHINE + P ] (m,n,true)=  $\lambda \{in=x\}.\{out=0\}, \mathfrak{B}$  [ FACTMACHINE + P ] (x!,0,false)

and:

and hence (by Simulation Induction)  $\mathfrak{B}[\mathit{FACTMACHINE} + P](m, 0, false) = \mathit{FACTORIAL}(m)$

and so

$\mathcal{B}[FACTMACHINE \downarrow P](m,n,true) = \lambda\{m\}.\{out=0\}, FACTORIAL\ (in!)$

Actually, as the reader may have noticed, the proof is only partial; we have not considered the cases when the devices fail to terminate (i.e. when we input a negative integer). We leave this as an exercise for those who like fiddling with 1. Alternatively, the problem could be eliminated by imposing suitable restrictions on the states and inputs.

We have now concluded the description of our model. In the next two sections we present two case studies which illustrate the range of applications we have in mind. In the first of these we completely specify a small general purpose computer, and then prove correct a microcoded implementation. In the second we show how devices like those used to implement the computer can be realised in nMOS. We would have like to have combined the two studies to yield a verification of an nMOS implementation of the computer, but there are too many details to manage by hand. We hope, however, to convince the reader that our model is capable of supporting such an analysis, and that by careful structuring of behaviour an explosion of proof size can be avoided.

# First case study: correctness of architecture and microcode

In this case study we illustrate how register transfer systems can be used to prove microcode correct. Our hope (and expectation) is that the kind of analysis described below can be scaled up to non-trivial examples, but to do this we will need machine assistance.

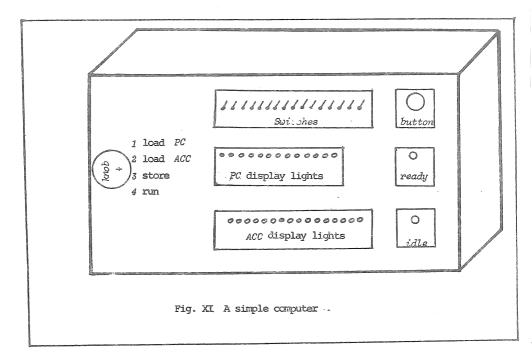

The system we shall verify implements the computer shown in Fig. XI.

This computer has two registers: the program counter PC which is 13 bits wide, and the accumulator ACC which is 16 bits wide. It has a random access memory which can store  $2^{13}$  16 bit words.

On the front panel there is a four position knob which determines what happens when the button on the right of the panel is pressed. There are three sets of lights: thirteen PC display lights which show the contents of the program counter; sixteen ACC display lights which show the contents of the accumulator; the ready light which is on when the computer is interruptable, and the idle light which is on when the computer is idling - i.e. not executing a program. There is also a bank of sixteen two position switches which are used for manually inputting data.

If the knob is in position  $n(1 \le n \le 4)$ , and the computer is ready and idling (i.e. the ready and idle lights are on), then pressing the button will cause the following to happen:

- n=1: The word determined by the state of the thirteen rightmost switches is loaded into  $PC_{\bullet}$

- n=2: The word determined by the state of the sixteen switches is loaded into ACC.

- n=3: The contents of ACC will be stored in memory at the location stored in PC.

- n=4: The program stored in memory will be executed starting at the location in PC. When the execution starts the idle and ready lights will go off. The idle light will stay off until the execution stops; this happens either when a halt instruction is reached or when an interrupt is generated by pressing the button. Interrupts are only accepted at the end of execution of each machine code instruction; readiness to accept an interrupt is indicated by the ready light being on. Thus to stop an executing program one must keep one's finger on the button until the ready light is on.

The instruction set for our little computer is shown in Fig. XII below

Format

| A CALLINA III     |                    |                                         |

|-------------------|--------------------|-----------------------------------------|

| opcode address(L) |                    |                                         |

| Instructions:     | Assembler mnemonic | Meaning                                 |

| Ololol L          | HALT               | Stops execution of program              |

| OOII L            | JMP L              | Jumps to L                              |

| Ollo L            | JZRO L             | Jumps to $L$ if $ACC$ contains $\theta$ |

|                   | $ADD\ L$           | Add contents of $L$ to $ACC$            |

|                   | SÜB L              | Subtract contents of L from ACC         |

| loll L            | LD $L$             | Load contents of $L$ into $ACC$         |

| 1 1 0  L          | ST L               | Store contents of $ACC$ in $L$          |

|                   | SKIP               | Skip to next instruction                |

Fig. XII Machine Code Instructions

Before formally specifying the semantics of our computer we need some lefinitions and notation for talking about bitstrings.

Let Word[n] be the (flat) domain of n bit words. We will also regard members of Word[n] as integers less than  $2^n$  and as n-tuples of truthvalues (so  $Word[n] = Bool \times \ldots \times Bool$ ). We interpret + (plus) and - (minus) on words as two's complement operators.

If  $w \in Word[n]$  and  $a \le b \le n$  then  $w < a:b > \epsilon Word[b-a+1]$  is the word corresponding to bits a to b of w. If  $a \le n \le b$  then w < a:b > is the top n-a+1 bits of w extended with 0's to a word of size b-a+1.

For example, if  $w \in Word[16]$  then w < 0:12 > is the address field of w and w < 13:15 > is the opcode field; if  $w \in Word[13]$  then  $w < 0:15 > \in Word[16]$  is the 16 bit word obtained by extending w with three 0's. Thus (w < 0:12 >) < 0:15 > is the word obtained from  $w \in Word[16]$  by zeroing the opcode. Note that from our conventions it follows that if  $w \in Word[13]$  then (w < 0:15 > +1) < 0:12 > = w +1. We use w < a > to mean the a<sup>th</sup> bit of w; if we regard bits as words of length one then w < a > = w < a:a >.

In our computer, addresses are 13 bits long, and contents of addresses are 16 bits long, hence to model the memory we define:

$$Mem = Word[13] \rightarrow Word[16]$$

A member  $m \in \mathit{Mem}$  is a function giving the contents  $m(w) \in \mathit{Word}[16]$  of each address  $w \in \mathit{Word}[13]$ . To model the semantics of storing we define  $m[w_2/w_1] \in \mathit{Mem}$  where  $m \in \mathit{Mem}$ ,  $w_1 \in \mathit{Word}[13]$ ,  $w_2 \in \mathit{Word}[16]$  to be the function identical to m except at  $w_1$  which it maps to  $w_2$ , i.e:

$$(m[w_2/w_1])w = \begin{cases} w_2 & \text{if } w = w_1 \\ \\ m(w) & \text{otherwise} \end{cases}$$

The state of our computer is characterised by the contents of the memory, the program counter and the accumulator, hence we define:

Thus, for example, if the computer is in state  $(m_s w_1, w_2) \in State$  and the knob is set to position 3 and the idle and ready lights are on, and the button is pushed, then the machine will move to state  $(m[w_2/w_1]_s w_1, w_2)$ .

We shall specify the semantics of the computer with two functions:

COMPUTER, EXECUTE: State  $\Rightarrow$  Seq[{knob,switches,button}];{pc,acc,ready,idle}] COMPUTER(m,w<sub>1</sub>,w<sub>2</sub>) gives the behaviour of the machine when it is ready and idling; EXECUTE(m,w<sub>1</sub>,w<sub>2</sub>) gives its behaviour when it is ready (for interrupts) but executing code (i.e. not idling). We do not specify the behaviour when the machine is not ready; why not should become clear later. The definitions of COMPUTER and EXECUTE are shown in Fig.XIII below; this constitutes the machine code, or 'target level' specification of the computer. The implementation which we will prove correct is based on the 'host' machine shown in Fig. XIV.

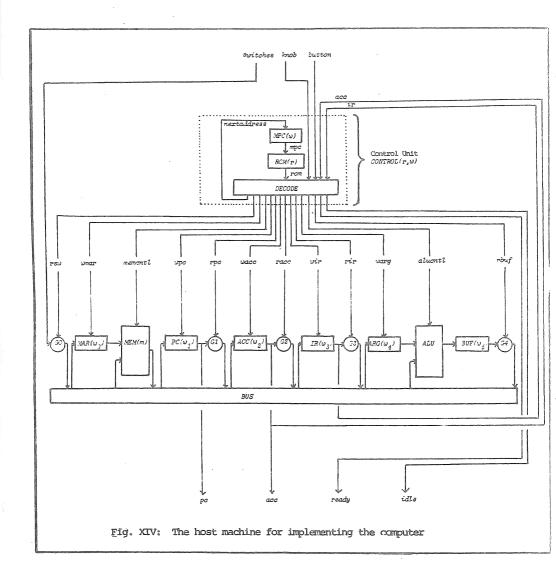

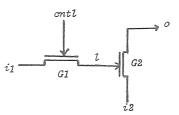

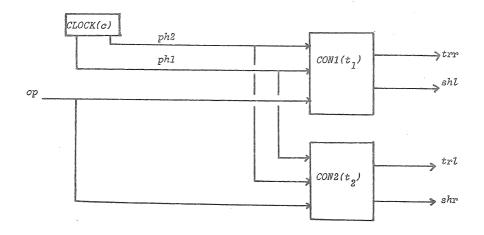

The host machine, which we will microprogram to emulate the target machine specified in Fig. XIII, is shown in Fig. XIV and has behaviour:

$\textit{HOST r } (w,m,w_0,w_1,w_2,w_3,w_4,w_5) \in Seq[\{knob,button,switches\}; \{pc,acc,ready,idle\}]$

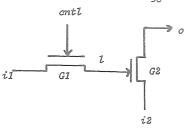

We have separated out the ROM contents r because later we shall characterise HOST(mucode) where mucode is a particular microprogram. The host's behaviour is much too complicated to define directly by a recursive definition like those in Fig. XIII, instead we will express it as a composition of the simpler behaviours of its various components. These naturally fall into two parts: first, a data part consisting of the memory MEM(m), the memory address register  $MAR(w_0)$ , the program counter  $PC(w_1)$ , the accumulator  $ACC(w_2)$ , the instruction register  $IR(w_3)$ , the argument register  $ARG(w_4)$ , the buffer register  $BUF(w_5)$ , the bus BUS, the arithmetic unit ALU, and the microcode controlled gates GO,GI,G2,G3,G4, and second, a microprogrammed control part CONTROL(r,w), which is shown in the dotted box, and has behaviour determined by ROM contents r (the microcode) and start address w.

The microcode stored in the read-only memory ROM(r) is shown in Fig.XVI written in a 'microassembler' notation which we explain shortly. If we name this chunk of microcode mucode and if we define the predicate  $P_{ready}$  by:

$P_{ready}(s) = true \iff s(ready) = 1$

then we will verify our implementation by proving for all  $m, w_0, \ldots, w_5$  that

$COMPUTER(m_s w_{1^s} w_2) = HOST \ mucode \ (0_s w_{0^s} w_{1^s} w_{2^s} w_{3^s} w_{4^s} w_5) + P_{ready}$

i.e. if we merge all non-interruptable 'microcycles' into a single 'macrocycle' then the behaviour of the computer and the host are equal.

```

\begin{split} & \textit{COMPUTER}(\textit{m}, \textit{w}_1, \textit{w}_2) \\ &= \lambda \left( \textit{knob}, \textit{switches}, \textit{button} \right), \\ & \{ pc = \textit{w}_1, \textit{ acc} = \textit{w}_2, \textit{ ready} = 1, \textit{ idle} = 1 \}, \\ & (\textit{¬button} \  \, \rightarrow \textit{COMPUTER}(\textit{m}, \textit{w}_1, \textit{w}_2), \\ & \textit{button} \  \, \rightarrow (\textit{knob} = 1 \  \, \rightarrow \textit{COMPUTER}(\textit{m}, \textit{switches} < 0:12 >, \textit{w}_2), \\ & \textit{knob} = 2 \  \, \rightarrow \textit{COMPUTER}(\textit{m}, \textit{w}_1, \textit{switches}), \\ & \textit{knob} = 3 \  \, \rightarrow \textit{COMPUTER}(\textit{m}[\textit{w}_2/\textit{w}_1], \textit{w}_1, \textit{w}_2), \\ & \textit{knob} = 4 \  \, \rightarrow \textit{EXECUTE}(\textit{m}, \textit{w}_1, \textit{w}_2))) \end{split}

```

```

· EXECUTE (m, w<sub>1</sub>, w<sub>2</sub>)

= \lambda {knob, switches, button},

\{pe = w_{1}, acc = w_{2}, ready = 1, idle = 0\}

let \{op = m(w_1) < 13:15 >, addr = m(w_1) < 0:12 > \}

in (op = 0 \lor button \rightarrow COMPUTER(m_2 w_1, w_2)

\Rightarrow EXECUTE (m_s addr_s w_2)_s

op = 1

\Rightarrow EXECUTE(w_2 = 0 \Rightarrow (m_s addr_s w_2), (m_s w_1 + 1_s w_2))

op = 2

\Rightarrow \textit{EXECUTE}(\textit{m}, \textit{w}_1 + 1, \textit{w}_2 + \textit{m(addr)}),

op = 3

op = 4

\Rightarrow EXECUTE(m_sw_1 + 1_sw_2 - m(addr))

op = 5

\Rightarrow EXECUTE(m_sw_1 + 1_sm(addr))

\Rightarrow EXECUTE(m[w_2/addr], w_1 + 1, w_2)

op = 6

\Rightarrow EXECUTE (m_s w_1 + 1_s w_2) ]

op = 7

```

FIG. XIII. Specification of the computer

The control lines rsw, wwar, wpe, rpe, wace, race, wir, rir, warg,  $rbw^p$ , ready, idle are all one bit wide as is the input line button from the button. The line knob from the knob is two bits wide (to encode the four positions), as are the control lines memcntl and aluentl to the memory and arithmetic unit respectively. All other lines are sixteen bits wide (PC and MAR ignore the three most significant bits of their input, and pad their outputs to sixteen bits with  $\theta$ 's). When a gate (i.e.  $G\theta$ , G1, G2, G3 or G4) is off (i.e. its control input is  $\theta$ ) then it outputs a special value  $\theta$  on to its output line. The idea is that this represents 'floating'or 'high impedance'; only one non-  $\theta$  must be put on the bus at once for correct operation. Thus the bus is defined by:

$$BUS = \lambda \{g\theta, g1, g2, g3, g4, mem\}. \{bus = join(g\theta, g1, g2, g3, g4, mem)\}, \ \exists US \}$$

where

$$join \ (x_1, x_2, \dots, x_n) = \begin{cases} x_i & \text{if} \quad x_j = \theta \text{ for all } j \neq i \\ undefined \text{ otherwise} \end{cases}$$

and a typical gate  $\it G$  with input  $\it in$ , Control  $\it cntl$  and output  $\it out$  is defined by:

$G = \lambda \{in,cntl\}. \{out = (cntl + in, \theta)\}, G$  The exact definition of gates G0,G1,G2,G3,G4 are:

$G0 = \lambda \{switches, rsw\}. \{g0 = (rsw + switches, \theta \}\}, G0$

$G1 = \lambda \{pe, rpe\}. \{g1 = (rpe \rightarrow pe, \theta)\}, G1$

$G2 = \lambda \{acc, racc\}. \{g2 = (racc \rightarrow acc, \theta)\}, G2$

$G3 = \lambda \{ir, rir\}. \{g3 = (rir \rightarrow ir, \theta)\}, G3$

$G4 = \lambda \{buf, rbuf\}. \{g4 = (rbuf + buf, \theta)\}, G4$

Notice that all these definitions are obtained from the definition of the 'generic gate' G by renaming lines. Thus — in what we hope is a self explanatory notation — we could have written:

$G0 = G\{in \mapsto switches, cntl \mapsto rsw, out \mapsto g0\}$

$G1 = G\{in \mid pc, cntl \mid pc, out \mid g1\}$

Such a notation is essential to handle devices built by connecting together large numbers of identical components. However, for simplicity we shall avoid introducing definitions and manipulative laws necessary to support line renaming. This will lead to some verbosity both in this case study and the next one.

The registers MAR, PC, ACC, IR, ARG all have a microprogram controlled write line. A typical one, with input in, write line wreg, and output dut has behaviour:

$REG(w) = \lambda \{in, wreg\}. \{out=w\}, REG(wreg + in, w)$

Since MAR and PC only hold thirteen bit words we must adjust the size of values got off and put onto the sixteen bit wide bus. The behaviour of these two registers is thus specified to be:

$$\begin{aligned} & \mathit{MAR}(w_0) = \lambda\{\mathit{bus}, \mathit{wmax}\}. \{\mathit{max} = \omega_0 < 0:15>\}, \ & \mathit{MAR}(\mathit{wmax} \rightarrow \mathit{bus} < 0:12>, \ w_0\} \\ & \mathit{PC}(w_1) = \lambda\{\mathit{bus}, \mathit{wpc}\}. \{\mathit{pc} = \omega_1 < 0:15>\}, \ & \mathit{PC}(\mathit{wpc} \rightarrow \mathit{bus} < 0:12>, \ w_1\} \end{aligned}$$

The other registers are sixteen bits wide, hence:

$$\begin{array}{lll} \mathit{ACC}(w_2) &=& \lambda \{bus, wacc\}. \{acc=w_2\}, \ \mathit{ACC}(wacc \rightarrow bus, \ w_2) \\ \mathit{IR}(w_3) &=& \lambda \{bus, wir\}. \{ir=w_3\}, \ \mathit{IR}(wir \rightarrow bus, \ w_3) \\ \end{array}$$

$$ARG(w_A) = \lambda \{bus, warg\}. \{arg = w_A\}, ARG(warg \rightarrow bus, w_A)$$

The ALU's buffer register BUF has no write line as it always stores the value on its imput, hence:

$$BUF(w_5) = \lambda \{alu\}. \{buf=w_5\}, BUF(alu)$$

is a sequential device whose state is determined by a memory function  $m \in Mem$  giving the contents of each address. Its behaviour is:

$$\begin{split} \textit{MEM}(\textit{m}) &= \lambda \{ \textit{max}_s \textit{bus}_s \textit{memcntl} \} \\ & (\textit{m@mcntl} = 1 \rightarrow (\{ \textit{mem} \neg \textit{m}(\textit{max}) \}_s \textit{MEM}(\textit{m})), \\ & (\textit{memcntl} = 2 \rightarrow (\{ \textit{mem} = \theta \}_s \textit{MEM}(\textit{m}(\textit{bus}/\textit{max}))), \\ & (\{ \textit{mem} = \theta \}_s \textit{MEM}(\textit{m}) \}) \end{split}$$

Thus 1 on memcntl causes a read - i.e. the contents of the value on line max is output; 2 on memcntl causes a write - i.e. results in the address on line max being updated to contain the value on bus. Except during a read the memory puts  $\Theta$  on to the bus.

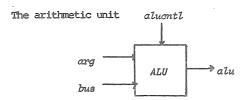

is a combinational device with behaviour given by:

ALU =  $\lambda \{arg,bus,aluentl\}$ . . . . .  $\{alu = (aluentl = 0 \Rightarrow bus, \\ aluentl = 1 \Rightarrow bus + 1 \\ aluentl = 2 \Rightarrow arg + bus \\ aluentl = 3 \Rightarrow arg - bus) \}, ALU$

Thus  $\theta$  on the control line causes the value on the bus to be passed through unchanged; 1 on the control line causes one plus the value on the bus to be output; 2 on the control line causes the sum of the two inputs to be output and 3 on the control line causes their difference to be output.

We can now define the data part of the host machine by:

$$\begin{split} \operatorname{DATA}(m_s \omega_0, \omega_1, \omega_2, \omega_3, \omega_4, \omega_5) \\ &= \operatorname{IMEM}(m) |\operatorname{MAR}(\omega_0)| \operatorname{PC}(\omega_1) |\operatorname{ACC}(\omega_2)| \operatorname{IR}(\omega_3) |\operatorname{ARG}(\omega_4)| \operatorname{BUF}(\omega_5) |\\ & \operatorname{GO}|\operatorname{G1}|\operatorname{G2}|\operatorname{G3}|\operatorname{G4}|\operatorname{ALU}|\operatorname{BUS}|\operatorname{1\hspace{-0.1cm}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}\rule{1.5pt}{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule{1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt{1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt{1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt{1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt{1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt{1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt{1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt{1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt{1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt{1.5pt}\rule1.5pt}\rule1.5pt}\rule1.5pt{1.5pt}\rule1.5pt}\rule1.5pt}\rule1$$

The control unit CONTROL(r,w) emits a sequence of signals to the other devices which cause them to perform the appropriate operations. It is a sequential device whose behaviour is defined by a microprogram stored in the read only memory ROM starting at address w. We shall go into details of the microcode soon put first, to give an idea of how the control unit works, we describe two examples which illustrate how emitting the appropriate sequence of signals causes the right thing to happen.

Suppose the knob is set to position 1 (load PC), the ready and idle lights are on, and the button is pushed. The control unit will then put 1 on the lines rsw and wpc and 0 on all other lines. Thus gate GO will open and the value from the switches - i.e. value on line switches will be put on the bus. During the same cycle, since the program counter write line wpc carries a 1, the value on the bus (i.e. the value from the switches) will be written into PC. Thus the word set up on the switches is loaded into the program counter in one microcycle.

Suppose next that the knob is set to position 3 (store) and the button is pushed. The control unit in this case will first signal 1 on lines rice and umar and 0 on all other lines. This causes G1 to open, and so the contents of PC is put on the bus and then this is written into the memory address register MAR. To complete the store operation, on the next cycle the control unit signals 1 on line race to put the contents of the accumulator on the bus, and during the same cycle signals 2 (i.e. write) on memont1 causing the memory to store the value which is on the bus (viz. the contents of ACC) at the address in MAR (viz. the contents of PC). Thus the contents of ACC is stored at the address in PC in two microcycles.

Note that the descriptions above are imprecise and incomplete; full details can be found in the microcode, which we now describe.

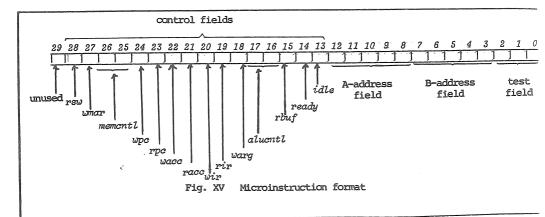

In order to complete the description of the host machine all we have to do is specify the control unit, and to do this we must describe the microinstructions which it interprets. These microinstructions are represented by 30-bit words stored in a read only memory (the ROM) which can hold thirty-two microinstructions.

Each microinstruction has a 3-bit test field, two 5-bit address fields (the A-address field and the B-address field), two 2-bit control fields (for memort1 and alucnt1), twelve single bit control fields and one unused bit (just in case we need it later!). The format is shown in Fig. XV below:

During each (micro) cycle the value put on a control line is the value in the corresponding control field of the current microinstruction. For example, the microinstruction to load the program counter from the switches must cause a 1 on lines rsw and wpc and 0 on all other lines, thus it has bits 28 and 24 set to 1 and all other control bits set to 0.