# THE DESIGN OF SYSTEMS FOR TELECOMMUNICATIONS BETWEEN SMALL AND LARGE COMPUTERS

Robin B. John

Thesis presented for the Degree of Doctor of Philosophy Faculty of Science, University of Edinburgh

November, 1973.

#### ABSTRACT

This thesis describes the development of a data communication system for small computers to enable them to link to large computers. The particular advantages and additional facilities made available to computer users through the use of such a link are described. A detailed description is given of the hardware and software components needed to achieve this link, together with the reasons for choosing the particular techniques employed. The discussions given highlight the problems involved in this type of operation. Some of these problems, such as lack of standardization, are short-term and will be overcome with the natural evolution of computer systems, while others are of a more fundamental nature related to the use of data transmission over long distances.

The system was designed to be applicable to a number of different This has resulted in a system which is easily small computers. transferable between machines, through the careful choice of interfaces This is seen as a step towards a more flexible to other components. and more modular method of system construction whereby complete software systems for arbitrary configurations can be put together using 'off-the-shelf' components already well-developed and tested. This contrasts with the present situation in which whole new systems are developed for a new computer, frequently duplicating systems already developed on other hardware. A detailed description of the factors involved in producing machine-independent, easily-transferable system components is given as a guide to other developments in this It is felt that there is need for a better-engineered direction. approach to the construction of software systems and it is hoped that the work described makes some contribution towards this end.

# CONTENTS

| Chapter  | 1       |                                              | 1  |

|----------|---------|----------------------------------------------|----|

| TELECOM  | IUNICAI | TIONS BETWEEN SMALL AND LARGE COMPUTERS      |    |

|          | 1.1     | Introduction                                 | 1  |

|          | 1.2     | Small computer capabilities                  | 1  |

|          | 1.3     | Central computers                            | 3  |

|          | 1.4     | Communications requirement                   | 3  |

|          | 1.5     | Summary of developments                      | 4  |

|          | 1.6     | The General System approach                  | 6  |

| Chapter  | 2       |                                              | 8  |

| USER APP | PLICATI | IONS FOR SMALL COMPUTER COMMUNICATION LINKS  |    |

|          | 2.1     | ERCC PDP-8/L                                 | 8  |

|          | 2.2     | Physics PDP-8                                | 10 |

| • *      | 2.3     | Social Medicine PDP-8                        | 13 |

|          | 2.4     | Computer Science CAD Project PDP-7           | 16 |

|          | 2.5     | IBM 1130 in ABRO and Dept. of Statistics     | 19 |

|          | 2.6     | Conclusions                                  | 21 |

| Chapter  | 3       |                                              | 24 |

| GENERAL  | COMMUN  | VICATIONS HARDWARE CONSIDERATIONS            |    |

|          | 3.1     | Main features of data communication hardware | 24 |

|          | 3.2     | Asynchronous communications adapter          | 26 |

|          | 3.3     | Synchronous communications adapter           | 27 |

|          | 3.4     | Telegraphic signalling                       | 29 |

|          | 3.5     | Modems                                       | 30 |

|          | 3.6     | Electrical circuit facilites                 | 33 |

|          | 3.7     | Conclusions                                  | 35 |

.

|        | Chapter   | 4             | •••••••••••••••••••••••                           |

|--------|-----------|---------------|---------------------------------------------------|

|        | SYNCHRONO | DUS V.        | ASYNCHRONOUS FOR COMPUTER-COMPUTER COMMUNICATIONS |

|        |           | <b>8.1</b>    | Introduction                                      |

|        |           | 4.2           | Handling of transmission errors                   |

|        |           | 4.3           | Error detection                                   |

|        |           | 4.4           | Block-oriented error detection 41                 |

|        |           | 4.5           | Comparisons                                       |

|        |           | 4.6           | Conclusions                                       |

| -      | Chapter   | 5             | <u>- + 4</u> 4                                    |

| •      | LARGE CON | PUTER         | COMMUNICATIONS HARDWARE                           |

|        |           | 5.1           | Introduction                                      |

|        |           | 5.2           | Communications controllers                        |

|        |           | 5.3           | IBM synchronous controllers                       |

|        | •         | 5.4           | ICL synchronous controller                        |

|        |           | 5.5           | Problem of compatibility                          |

| •<br>• |           | · <b>5.</b> 6 | Conclusions                                       |

|        |           | •             |                                                   |

|        | Chapter   | 6             | ••••••••                                          |

|        | INTERFAC  | ING TO        | THE SMALL COMPUTER NO SECTION SCORE SCORE SCORE   |

|        |           | 6.1           | Introduction                                      |

|        |           | 6.2           | The 'uniform interface' requirement 50            |

|        |           | 6.3           | Small computer input/output interfaces 52         |

|        |           | 6.4           | PDP-8                                             |

|        |           | 6.5           | Modular One                                       |

|        |           | 6.6           | ICL 100                                           |

|        |           | 6.7           | IBM 1130                                          |

|        |           |               |                                                   |

|        |           |               |                                                   |

|        |           |               |                                                   |

50 Chapter 6 INTERFACING TO THE SMALL COMPUTER (cont.) Common facilities of the input/output interfaces. . 64 6.8 6.9 General applicability 67 6.10 · · • · 69 Chapter SMALL COMPUTER COMMUNICATIONS HARDWARE 7.1 69 Introduction 69 7.2 Flexibility requirement 70 7.3 Basic functional requirements . . . . 72 Extra functions . . . . . . . . . . . . . . . . 7.4 Preliminary functional specification .... 75 7.5 Non-interrupt mode of operation . . . . . . . 77 7.6 Program interface . . . . . 77 7.7 Communications interface specification. . . . . . 7.8 82 Experience of first implementation. . . . . . . . 85 7.9 89 Improved functional specification . . . . . . 7.10 Interface test facility . . . . . . . . . . 91 7.11 Conclusions on small computer communications 7.12 92 hardware 94 Chapter 8 SPECIFICATION FOR SYNCHRONOUS COMMUNICATIONS INTERFACE FOR SMALL COMPUTERS 94 8.1 Basic requirement . Modem interface consierations . . 94 8.2 . .

iii

|                    | iv iv                                                                   |

|--------------------|-------------------------------------------------------------------------|

| Chapter            | 8                                                                       |

| SPECIFIC<br>COMPUT | ATION FOR SYNCHRONOUS COMMUNICATIONS INTERFACE FOR SMALL<br>ERS (cont.) |

|                    | 8.4 General                                                             |

|                    | 8.5 Receive (RX) channel                                                |

|                    | 8.6 Modem interface considerations for RX channel 98                    |

|                    | 8.7 Transmit (TX) channel                                               |

|                    | 8.8 Modem interface considerations for TX channel 100                   |

|                    | 8.9 Timeout control                                                     |

|                    | 8.10 Interrupt control                                                  |

|                    |                                                                         |

| Chapter            | 9                                                                       |

| COMMUNIC           | ATIONS SOFTWARE FOR THE SMALL COMPUTER                                  |

|                    | 9.1 Overview                                                            |

|                    | 9.2 General requirements                                                |

|                    | 9.3 Package implementation-general details 104                          |

|                    | 9.4 The user interface                                                  |

|                    | 9.5 The communications hardware interface 112                           |

|                    | 9.6 The executive interface                                             |

|                    | 9.7 Remote host computer interface                                      |

|                    | 9.8 Conclusions                                                         |

.

.

| IMPLEMENTATION DE | ETAILS IN ACTUAL SISTEMS                              |

|-------------------|-------------------------------------------------------|

| 10.1 St           | ummary                                                |

| 10.2 PI           | DP-8 with ERCC communications controller 126          |

| 10.3 PI           | DP-8 with Data Dynamics 6310 controller 128           |

| 10.4 10           | CL 4100 with ERCC communications controller 132       |

| 10.5 M            | odular One with 1.61 communications multiplexor. 133  |

| 10.6 PI           | DP-11 with DP11 communications controller 140         |

| 10.7 C            | onclusions                                            |

|                   |                                                       |

| Chapter 11        |                                                       |

| IMPLEMENTING THE  | COMMUNICATIONS SYSTEM ON A NEW SMALL COMPUTER         |

|                   | 216                                                   |

|                   | ntroduction                                           |

| 11.2 G            | eneral                                                |

| 11.3 D            | Difficulty of 'live' testing                          |

| 11.4 U            | Jser program                                          |

| 1155 C            | Communications hardware                               |

| 11.6 C            | Communications software                               |

| <b>11.7</b> H     | lardware interfacing routines                         |

| 11.8 U            | Jser interface routines and executive interface . 177 |

| 11.9 C            | Conclusions about transferability                     |

|                   | ·                                                     |

| Chapter 12        |                                                       |

| COMMUNICATIONS P  | PROTOCOLS FOR INTER-COMPUTER WORKING                  |

| 12.1 1            | Introduction                                          |

| 12.2 0            | General characteristics of protocols 181              |

v

COMMUNICATIONS PROTOCOLS FOR INTER-COMPUTER WORKING 12.4 12.5 12.6 12.7 Half-duplex protocol with one-way data traffic . 187 Half-duplex with two-way transmission interleaved 196 12.8 Full-duplex with two-way simultaneous traffic ... 211 12.9 12.10 Conclusions on communications protocols . . . . . 217 . . . .. :

SYSTEM PROGRAMMING ON SMALL COMPUTERS WITH HIGH-LEVEL LANGUAGES

| 13.1  | Introduction                                    |

|-------|-------------------------------------------------|

| 13.2  | Compilation on a different computer             |

| 13.3  | Language facilities - general consideration 224 |

| 13.4  | Data elements                                   |

| 13.5  | Data structures                                 |

| 13.6  | Machine address manipulation                    |

| 13.7  | Program structure and statements                |

| 13.8  | Expressions                                     |

| 13.9  | Conditional statements                          |

| 13.10 | Programmed loops                                |

| 13.11 | Programmed transfers                            |

| 13.12 | Machine-code                                    |

| 13.13 | Routines and functions                          |

| 13.14 | Block structure                                 |

| 13.15 | Run-time environment                            |

| 13.16 | Conclusions                                     |

vi

vii

CONCLUSIONS

|         | 14.1    | Introduction                               | 47 |

|---------|---------|--------------------------------------------|----|

| ·       | 14.2    | Uses of computer telecommunications 2      | 47 |

|         | 14.3    | Technical aspects of data communications 2 | 50 |

|         | 14.4    | System construction techniques             | 53 |

|         | 14.5    | Transferable system components 2           | 54 |

|         | 14.6    | Interfaces                                 | 56 |

|         | 14.7    | Real-time components 2                     | 57 |

|         | 14.8    | Use of high-level languages                | 58 |

|         | 14.9    | Transferable hardware                      | 58 |

|         | 14.10   | System construction in the future 2        | 59 |

|         | 14.11   | Further developments                       | 62 |

|         |         |                                            |    |

| ACKNOWL | EDGEMEN | TS                                         | 64 |

| REFEREN | CES     | ••••••••••••••••••                         | 65 |

|         |         |                                            |    |

Appendix A

Chronology of significant developments, indicating items of work involving other people.

# Appendix B

Other available documents on particular implementations.

#### Chapter 1

TELECOMMUNICATIONS BETWEEN SMALL AND LARGE COMPUTERS

#### 1.1 Introduction

The development of computing to support research and teaching work in Edinburgh University has involved the use of both a large, central computer run as a general university service and a number of small computers local to one department or research unit. A similar pattern of development has taken place in other universities, as well as many other large institutions using computers in diverse applications. The central computer provided the capability for handling large-scale jobs in respect of core store, processing requirements and backing storage. The small computers were applied to local small-scale computing problems, such as on-line control of experiments, data collection and reduction, interactive graphics, etc. There was a wide variety of such computers in use in Edinburgh and a small list is given in Table 1.1 to illustrate some of the applications.

#### 1.2 Small computer capabilities

These small computers were performing tasks which would be difficult to implement in an efficient way on large general - purpose computers, because of the requirement for fast response to real time events, 'hands-on' access, attachment of special peripherals, etc. For these reasons, it was not feasible to use the central computer directly for these applications.

- 1 -

| Computer | Location             | Applications                        |

|----------|----------------------|-------------------------------------|

| PDP-8    | Physics              | Experiment control; data collection |

| PDP-8    | Social Medicine      | Analysis of survey data             |

| PDP-7    | Computer Science     | CAD work                            |

| PDP-8    | Computer Science     | Teaching and research               |

| TPM 130  | Dept. of Statistics  | Statistical analysis problems       |

| IBM1130  | ABRO                 | Analysis of experimental data       |

| ICL4130  | School of Mach. Int. | Machine Intelligence Research       |

| ICL903   | Royal Infirmary      | Path. Lab. work; medical data       |

|          |                      | analysis                            |

# Table 1.1

However, while the small computer was best suited to the special - purpose system, it did not generally have the computing power, store size or backing store capacity to handle the larger non - real - time problems that followed, such as the processing of experimental data by applications programs, or even the compilation of programs written in a comprehensive high-level language.

These difficulties could be overcome by providing the small computer with easy access to a powerful backup computing facility by means of a direct communications link. In other words, the small computer could have the same degree of access to large - scale computing power as the on-line teletype user. However, a much higher data rate would be necessary for the link to be useful to the small computer since the volume of data involved would be much greater than could be sensibly handled at a teletype speeds.

- 2 -

Furthermore, the small computer would not be limited in its speed of operation by human operator action times, and therefore the data rate would be limited only by technical and economic considerations.

## 1.3 Central computers

There were two relevant central computers in Edinburgh in 1969. The first was the ICL 4-75 which was installed in early 1969 and for which a sophisticated multi-access system was being developed jointly by ICL and the Edinburgh University Computer Science Department. The second was the IBM 360/50 which was installed in mid 1969 to take over the batch processing workhoad from the ICL KDF9 which was the first central computer installed in the University. The central facility was run in all cases by the Edinburgh Regional Computing Centre (ERCC). The use of other large computers was also considered as the source of backup computing power in order to allow for any possible future developments. All large computers currently available seemed to provide the capability for communication at speeds significantly higher than teletype speeds.

#### 1.4 Communications requirement

The general requirement, then, was to provide a facility for all the small computers currently in use or likely to be used by individual departments which would enable them to communicate at high speed with any possible large mainframe computer, the initial target machines being the ICL 4-75 and the IBM 360/50.

- 3 -

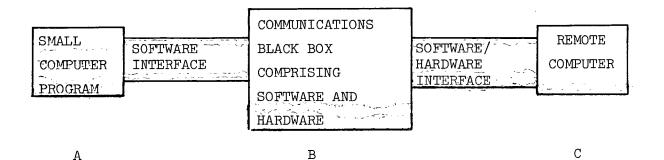

This requirement can be shown diagrammatically as follows:

A suitable implementation of item B had to be devised which would match the requirements of item A against the constraints imposed by accessing item C via a communications link. This implementation of item B should provide facilities whereby the user program could send and receive any type of data that he might wish to process on the remote computer. Furthermore, item B should be constructed in such a way that it would require a minimum of effort to transfer it to any other small computer once the first implementation had been completed successfully.

### 1.5 Summary of developments

In order to achieve this objective, detailed studies were made of a number of areas as follows:-

- a) user applications implemented by item A in order

to determine the facilities to be provided.

- b) the communications facilities supported by the possible large remote computers, particularly the ICL 4-75 and the IBM 360/50.

- 4 -

- c) the communications facilities provided by the GPO.

- d) the communications facilities provided by the various small computers.

- e) the development of communications hardware suitable for attaching to any small computer in the event that there was no suitable communications peripheral available.

- f) ways of incorporating new peripheral handling software into the small computer software system, involving direct physical control of the peripheral.

- g) the use of a high-level language for the small computer software to facilitate the transfer to other small computers.

- h) the development of software construction

techniques to aid the debugging of the real time, interrupt driven software needed to

handle the communications link.

- i) communications techniques for achieving maximum utilization of the communications link while guaranteeing error - free transmission.

These studies are described in later sections of this report.

As a result of these studies, a communications system has been developed which has been successfully implemented on a number of small computers. This system comprises both software and hardware, although in some cases where the computer had suitable communications hardware, only the software component was needed. The software is constructed in such a way that it will work with any suitable communications hardware, irrespective of the way the hardware is programmed. Because of the ease with which the system has been mounted on different computers, even one which did not exist when the original studies were made, there is now a high degree of confidence that the system can be applied to any small computer.

A detailed description of the implementation of this system, together with a description of the routine procedures for applying it to a new computer, is given in subsequent sections of this report.

Two other sections of this report give a general discussion of computer-to-computer communications protocols and a general discussion on the useoofffhigh-level languages on small computers. The last section attempts to summarize the particular aspects of the work described which are considered to be of importance, both in the specialized area of communications and in the more general area of system construction and development.

#### 1.6 The General System Approach

Although other work has been described in the literature on the subject of communication links for small computers, notably (1) and (2), no attempt has been made to produce a system generally applicable in a wide range of environments. This report describes an attempt to produce a properly engineered communication system which can be

- 6 -

easily 'plugged-in' to an existing system to provide communication facilities.

As such, the ideas developed apply to the comparatively new drea of computer system development in transportable software techniques. Other relevant work has been described in (3) and (4). Hopefully, we are moving away from the situation where identical systems are programmed anew for each new computer and there is no possibility of transferring well-developed systems from existing computers. In the future, it should be possible to transfer complete systems onto new hardware with the minimum amount of new programming and it is hoped that the system described in this report makes some contribution to the techniques required to achieve this end.

- 7 -

#### Chapter 2

USER APPLICATIONS FOR SMALL COMPUTER COMMUNICATIONS LINKS

# 2.1 Introduction

When the development of suitable communications facilities for small computers was first being investigated during 1969, there existed a small number of specific applications which had well-defined objectives for the use of a communications link. There also existed a much larger number of potential applications because of the rapidly-growing number of small computers being used for dedicated purposes within individual departments. The intention was that as a result of studying carefully the requirements of the velldefined applications, a general communications support system could be developed which would also be suitable for the potential future users with their as yet undefined applications.

The The specific applications which existed at the time are described below.

### 2.2 ERCC PDP-8/L

The proposed use for this computer was to support the Calcomp graph plotter, which was at the time directly attached to the KDF9. The graph plotter service had to be transferred initially to the 360/50 and eventually to the 4-75. Although it was possible to connect the Calcomp plotter directly to the 360/50 and also to the 4-75, this method of connection was expensive, and the controller involved could obviously only be used to support the graph plotter.

- 8 ~

Furthermore, the standard software available for the 360/50 did not support the use of a graph plotter as a standard output peripheral, so that special software would have been needed, the expertise for which did not exist within ERCC at that time. It was decided therefore to use a small computer to control the plotter directly, and connect the small computer via a communication This solution had several advantages. link. Firstly, the hardware needed on the 360/50 to control the communications link could also be used for other remote computer links, since the plotter would not be in use all the time. Secondly, since the support for remote computer links was also planned for the 4-75, there would be no special problems involved with the planned transfer of the graph plotter to the 4-75. Thirdly, the standard software for the 360/50 supported the use of remote computer links, so there would be no requirement for special software on the 360/50. The requirement for the PDP-8/L communications system was to support the transmission of the graph plotter files from the 360/50. These files were effectively binary data files specifying XY vectors and pen control commands.

A second service planned for the PDP-8/L was the support of paper-tape input to the 360/50. There was no paper-tape equipment on the 360/50 as there had been on the KDF9, yet there were still many users who produced paper-tape from experiments using dataloggers or small computers. These users were initially catered for by transferring the paper-tape to magnetic tape on the 3-75 and then reading this magnetic tape on the 360/50, where the user could

- 9 =

process the data. Since it was a comparatively simple job to interface a paper-tape reader to the PDP-8/L, the paper-tapes could be read directly into the 360/50 if the communication system provided the appropriate facilities. There was no standard format for paper-tape data - some of it was in Edinburgh ISO code, some was in other less common character codes, some was genuine binary data and there was also some 5-channel paper-tape. In order to cater for all these diverse requirements, two facilities would be Firstly, support for the locally recognised ISO code, sufficient. which would be handled as character data, and converted to a form which would be recognised as characters by the 360/50. Secondly, all other data formats would be treated as 8-bit binary data, whether it be binary or not, and the user could then interpret the data according to his own conventions.

The requirements for communications support for the PDP-8/L were therefore character and binary data outwards, and binary data inwards.

#### 2.2 Physics PDP-8

The Physics department had been using a sophisticated PDP-8 installation for some time for the direct control of on-line experiments, and the gathering of data from a variety of analogue equipment. A small time-sharing system had been developed for the computer which supported the use of programs written in a subset of IMP for the control of the experiments<sup>(5)</sup>. The compiler for this IMP subset was itself written in IMP, but was far too big a program to be run on the 8K PDP-8 system. Compilations were therefore

- 10 -

carried out on the 360/50 or 4-75, and the resulting binary object programs punched out on paper-tape at ERCC. This process therefore involved long delays for the PDP-8 users at Physics, since their turnaround was limited by the wan schedules.

If a communication link could provide a fast and convenient way of accessing this remote compiler, and getting the program listing and object program back quickly into the PDP-8 filing system, program development for the PDP-8 user would be much more convenient.

A second application for the communication link at Physics concerned the data that was being gathered from the experiments and The IMP programs in the PDP-8 could perform the analogue equipment. a certain amount of first level data analysis in order to vet the raw Any major computational work on the data, however, had to be data. performed on the 4-75 or 360/50 because of the very limited size The data, which was stored on DEC-tape and speed of the PDP-8. during the experiment, had to be punched out on paper-tape and sent to ERCC for transfer to a magnetic tape before any major analysis could take place. This obviously entailed considerable delays. If the data could be sent directly from the DEC-tape to the 360/50, and the analysis program called up at the same time, these delays would practically disappear since the only holdups then would be the actual transmission time for the data and the natural turnaround delay for executing the program on the 360/50.

Experimental data consisted either of numbers in character format, or numbers in 12-bit PDP-8 binary format, so the communication link

- 11 -

should be able to handle both types.

The communication link requirements for this system were therefore character data and binary data inwards and outwards.

A further requirement became apparent in this application on considering the quantities of data accumulated by the experiments. The data transmission speed provided by the communication link would have to be considerably in excess of the speed available for, say, teletype communications. Otherwise, it would take several hours to transmit the data from an average experiment, and the advantage gained from the direct communication link would be nullified. There were several cases where a time in excess of 24 hours would have been required to transmit the data at teletype speed. The changes that all elements of the communications link, including both computers, would continue operating for that length of time were quite low, so it is unlikely that such cases would be handled at all.

It was an essential requirement for this application, therefore, that the data transmission speed should be at least an order of magnitude faster than teletype speed.

It might be argued in connection with this application that it would be even more satisfactory if the data could be transmitted directly as it was being gathered, rather than going through an intermediate stage of storing it on DEC-tape. The feasibility of doing this depends very much on the rate at which data is being gathered, and the reliability of the main computer. A dedicated small computer usually has a much higher probability of staying up through the whole of an experiment than a general-purpose computer

- 12 -

which is performing a number of other un-related functions at the same time. Also, there may be upredictable delays involved in servicing the communication link on the main computer because of peak load situations caused by the other activities on the system. Such delays would be unacceptable in a real-time experiment and valuable data might be lost. Because the small computer is working in a dedicated environment, and the data is being output to the relatively fast medium of DEC-tape, an adequate response time can be guaranteed, even if it means running only the one experiment. Although there may be some situations where the data gathering is not time-critical, and the experiment can be repeated if the communication link or remote computer fails in any way, in general it is more convenient to gather the data locally, thereby minimizing the number of different components involved in the real-time situtation.

#### 2.3 Social Medicine PDP-8

The Department of Social Medicine had been using a small PDP-8 system for statistical analysis of survey data. The installation comprised a PDP-8 with 4k of core and teletype, paper-tape reader and punch and a card reader which could read column binary cards. The paper-tape equipment was just used for ease of program development, the main peripheral being the card reader. All the survey data to be analysed was punched onto cards and extensive use was made of so-called column binary cards, in which any combination of the 12 holes in a particular column may be punched, rather than the restricted combinations allowed by certain standard card codes, such

- 13 -

as EBCDIC or BCD. The use of column binary can produce a considerable increase in the packing density of data on cards when purely numeric data is being recorded. This feature is obviously useful therefore where a large volume of data is being processed. The use of column binary was also attractive to the PDP-8 users at Social Medicine since the PDP-8 is a 12-bit machine, and it is very easy to store and manipulate each individual card column.

Although the processing of the column binary cards was easily handled on the 12-bit PDP-8, problems arose when larger and more complicated survey programs necessitated the use of the main ERCC machine. Both the 4-75 and the 360/50 are organized around the 8-bit byte unit of storage, and the peripheral equipment is intended to handle 8-bit data characters, implying the use of the restricted EBCDIC card codes for card data. It is possible to have special hardware options fitted to the 4-75 and 360/50 card readers which enable column binary cards to be read by splitting each card column The mode of reading, EBCDIC or binary, is into two 8-bit bytes. selected by software command. However, it is operationally very inconvenient to read jobs in which program and control cards are punched in normal EBCDIC code, and the data is punched in column binary format. In fact, the standard spooling software on both the 4-75 and the 360/50 did not cater for this situation, and the only way to handle column binary was to run a special utility which bypassed the normal spooling software and read the cards directly into core from where they were stored on magnetic tape. The user program could then access the data in a subsequent run. Such special procedures obviously produced considerable delays for any

- 14 -

user with columnebinary card data.

In one sense, the problem of handling column binary cards was a historical one, since, if users could be discouraged from producing any new binary cards, then all the binary cards currently in use could be copied onto magnetic tape with the special utility and that would be the end of the problem. However, a strong requirement was developing within the University for the use of mark sense cards and documents. The use of these facilities could eliminate the laborious data preparation work involved in transcribing the information from manually prepared forms and documents into a machine-readable form. There was a demand for such facilities in the areas of gathering data for surveys and for examinations involving the use of multiple-choice questions.

Mark sense cards and documents produce data of a very similar form to binary cards, the difference being that there may be less than 80 columns per card. The demand for the use of such facilities, therefore, reinforced the requirement for a convenient way of reading column binary cards as normal program data.

Since there is no sophisticated spooling software being used on a dedicated small machine, the program is reading the cards directly, one at a time, and it is a simple matter to change reading modes by a suitable operator command. The normal program and control cards can be read and translated according to the card code being used and transmitted as character data. The 12-bit column cards can be converted to a suitable 2-byte representation such that each binary card is sent as 160 binary data characters. This format can

- 15 -

be easily reconstituted by the program to the original binary card representation of required, using the 16-bit half-word data type in IMP or FORTRAN to store each card column. This facility then means that binary card data can be processed as easily as normal card data on the 360/50 or 4-75.

The requirement for the communication system was simply to be able to transmit character data and binary data and be able to switch between them in the same transmission.

## 2.4 Computer Science CAD Project PDP-7.

The CAD group in the Department of Computer Science were using a PDP-7 computer to support a number of projects in interactive They had long recognised the difficulty of writing graphics. large, complicated graphics applications programs to run in the PDP-7 itself and were wedded to the philosophy of using a larger, general purpose computer as a backup machine. The PDP-7 would be responsible for managing the low-level control of the display, and handling those things that required a fast real-time response to maintain the interaction, such as pen-tracking. The graphics application program, which actually generated the display file, would run in the powerful backup machine. This program, which frequently involved a considerable amount of numerical work and manipulation of complex data structures could be written almost entirely in a high-level language. This meant that it was much easier to write and test than if it were written in the PDP=7 assembler language, and also that the size of application that could be handled was not limited by the small amount of core storage available on the PDP-7.

- 16 -

This type of two-computer system obviously requires the use of some sort of communication link between the two machines. The speed of this link must be sufficient to avoid long delays in making changes to the picture displayed which require the re-generation and re-transmission of the display file.

The CAD group were already using a two-computer system of this nature, the back-up computer being the Elliott 4130 in the Department of Machine Intelligence. Since the PDP-7 was situated in the next room to the 4130, a high-speed local connection had been established which gave a data rate equivalent to a serial data transmission speed of about 40 kilobauds. This speed was sufficiently high that there were never any delays involved in changing the picture being displayed.

Although this arrangement gave a very satisfactory performance for the display system, there was considerable inconvenience involved in using it. This was caused by the fact that the other main activity for the 4130 was running the multi-access POP-2 system for the Machine Intelligence Department. This was a specialpurpose system and was not suitable for running the large graphics application programs, for which the favoured language was FORTRAN which was not compatible with the Multi-POP system. Therefore, pressure for time on the 4130 meant that the dedicated sessions for graphics work were only available during the evening and night.

Because of this, the CAD group were anxious to establish a communication link to a remote large computer which would allow their graphics programs to be time-shared with other programs,

- 17 -

thereby avoiding the requirement for the dedicated and inefficient use of an expensive general-purpose computer. This was obviously the sort of application that could eventually be supported by the multi-access operating system being developed for the 4-75, but as this project was still in its early stages, other alternatives had to be considered. The 360/50 was not particularly suitable since the software was oriented to high throughput of batch work, and although time-sharing was supported, the dynamic swapping in and out of programs performing interactive work was not, so the graphics program would have been permanently resident for long periods and making inefficient use of that portion of core store.

The other possibility was to use the 360/67 at Newcastle University which was running the interactive Michigan Terminal System (MTS) for most of the day. This system was certainly suitable for running interactive graphics programs, since it had been used in this way at the University of Michigan<sup>(6)</sup>. Furthermore, a communication link already existed between Newcastle and Edinburgh to support a Remote Job Entry service to ERCC. If appropriate communications support could be provided for both ends, the existing link could be made available to the PDP-7 for part of the day.

Although the existing link between the PDP-7 and the 4130 was equivalent to a data rate of 40 kilobaud, this was generally far in excess of requirements. It was found that a number of the graphics applications would still work satisfactorily with the link speed artificially slowed down to about 2 kilobauds, particularly if certain minor changes were made to the graphics software to minimise

- 18 -

the traffic across the link. It would have been prohibitively expensive to provide a link speed of 40 kilobaud between Edinburgh and Newcastle, but 2 kilobaud was perfectly feasible economically, and was the speed that had been used for remote interactive graphics at the University of Michigan.

The communication system requirements for this application were again quite clearly defined. The transmission of **k**ext messages was required in both directions to enable the operator of the graphics satellite to send commands to the graphics applications program and receive teletype messages back. Also, it was necessary to transmit the display file generated by the applications program to the small machine. This required the transmission of binary data between the two machines. Information about operator interaction with the display, such as the position of the light-pen at particular times, was also most conveniently transmitted as binary data.

#### 2.5 IBM 1130 in ABRO and Department of Statistics

Both these departments were using the standard IBM 1130 configuration comprising processor, store, card reader, line printer and cartridge disk. The computers were used for small-scale statistical and numerical analysis applications, using the extensive subroutine library and FORTRAN II compiler available for the 1130. They were restricted in the size of problems they could handle because of the small file store (1 megabyte), the slow speed of the 1130 as a computer ( $\delta\mu$ s core store), and the very slow (100 lpm) line printer. In order to handle larger problems, they needed access to a larger computer and this could be conveniently provided by means of a communications link. By writing the FORTRAN programs

- 19 -

carefully, they could be run on both the 1130 and the 360/50 without changes, so that program development could be carried out most conveniently on the 1130 before submitting the program for largescale processing to the remote machine.

This application was obviously a standard Remote Job Entry system where the communication link merely provided a faster turnaround of jobs. The data transmission requirements were for character data in both directions for job input and output.

A more sophisticated application was planned, however, which involved performing successive phases of a calculation on alternate machines. In other words, a preliminary phase would be conducted on the 1130, possibly being steered by interactive work on the 1130 operators console, at the end of which intermediate results would be stored on the disk. These intermediate results would then be transmitted as data for a program to be run on the 360/50, where the extra power of the larger machine was required. The output from this program might then contain information to be stored back on the 1130 disk for further local processing, and so on.

Although this procedure could be carried out by punching out intermediate results on punched cards for submission in a normal job to the other computer, this would be a very tedious business and would detract considerably from the convenience of carrying out certain phases of the calculation in the controlled, hands-on environment of the 1130. This was really an application which needed a communications link between the two machines.

- 20 -

Since the most convenient way of storing data on the 1130 disk was in the internal number representation format of the 1130, rather than in character format, the transmission of this information between the machines required a binary data transmission capability in addition to the character data transmission required for the normal job input and output.

# 2.6 Conclusions.

The conclusions that can be drawn from the above descriptions of specific applications about the requirements of a communication system are as follows:-

- a) the applications involve a number of completely different small computers, so the communication system should not use the special features of any one small computer, but rather should use only a minimum subset of features which are common to all small computers, and this applies to hardware and software.

- b) all the applications involve a completely different environment in respect of usage, supporting peripherals and executive, even when the same computer is used, so the communication system should use the executive to the absolute minimum, if at all, and should provide an interface to the rest of the software which makes no assumptions about the local source or destination of transmitted data.

- c) the transmission speed required is at least an order of magnitude greater than teletype speed, and since in some applications, speed is critical, it should be possible to buy more speed without affecting the communication system; it is also desirable to maximize effective throughput, since in some cases large volumes of data are involved.

- d) suitable communications hardware is available for some of the computers but not for others, so that although hardware will need to be developed as part of the communication system, the software component of the system should not be oriented to that particular hardware implementation, but should be capable of using any implementation available for the type of communication chosen.

- e) the system should be capable of being used to communicate with different main computers in order to accommodate future changes in the central computer system available.

- f) the system should be capable of handling two basic data types - text data, where the bit patterns are interpreted according to some universally agreed code such as ISO or EBCDIC and where conversion between different representations may be necessary in order to preserve the textual meaning of the data; binary data, where the bit patterns have no universal interpretation and have meaning only to the user program processing the data. In this latter case, the data must be transmitted by the system

- 24 -

# GENERAL COMMUNICATIONS HARDWARE CONSIDERATIONS

# 3.1 Main features of data communication hardware

Before going on to discuss the various communications facilities supported by the large computers, a brief description of the main features of serial data communication links is given here in order to support some of the technical arguments used later.

# Attachment of local peripherals

Information transfer between a computer and its local peripheral devices normally makes use of high-speed parallel data interfaces. These parallel interfaces provide lines for at least one character together with lines for error checking and control of the data transfer. A simple example is the British Standard Interface (BSI) for parallel data transfer. Electrical signals are propagated along these interfaces by fairly low DC voltages, e.g. 5 or 6 volts, that correspond with the low voltages used in the computer electronics. Also, signal duration is very short in order not to slow down the execution of input/output instructions in the computer.

The influence of electrical interference, resistance losses and propagation delays on these low-magnitude, short-duration signals means that expensive high-quality cables have to be used in order to guarantee reliable data transfer. These factors mean that this type of interface - high-speed parallel - is only feasible for peripherals which are close to the computer. In fact, a maximum cable length of up to 100 feet is common.

# Attachment of Remote Peripherals

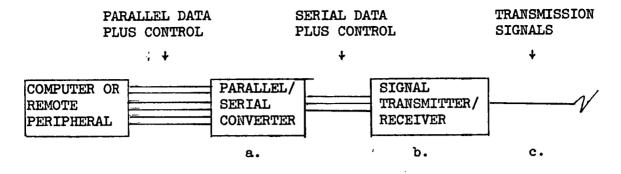

Remote peripherals may be situated several miles from the computer, so that even if the electrical transmission problems were solved by using special hardware, the cost of multi-way parallel cables would be very high. In fact, because of the costs involved, the simplest possible electrical interface is used for the connection of remote peripherals. This consists of one circuit for data into the computer and one circuit for data out of the computer. One circuit is sometimes used for both functions. The signals which are transmitted simultaneously in a parallel interface to a local peripheral are sent in serial form, one after the other at a fixed rate, along a single transmission line to a remote peripheral.

The electrical connection between the computer and the remote peripheral thus consists of the following components:-

- a) hardware to convert the parallel information from the computer into serial form for output and vice versa for input.

- b) hardware to convert the serial information at the low DC voltage levels into a form suitable for reliable transmission over several miles of cable.

- c) single or double circuit electrical cable for one way at a time (half-duplex) or both directions simultaneously (full-duplex) data transmission.

± 25 ±

It is the variations in the methods of implementing these three components that provide the different systems of serial data communications in use today.

There are basically two different implementations of item a. which are referred to as synchronous and asynchronous communications adapters. There are a number of implementations of items b. and c. which differ in the speed of reliable data transmission which they give, and these implementations are closely related to the choice of a synchronous or asynchronous transmission adapter. Economic considerations play a large part in deciding which type of system to use. The requirement for higher speed and/or higher reliability usually increases the cost of the system.

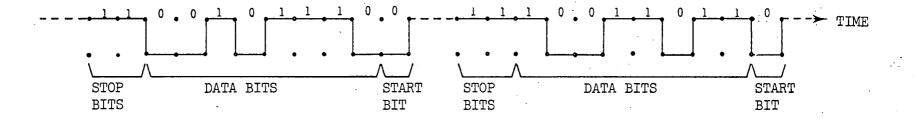

#### 3.2 Asynchronous communications adapter

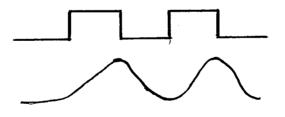

In asynchronous communications (Fig 3.1), each character of a message is identified by one start bit and one or more stop bits framing the character. Each character is therefore self-identifying and there is no fixed time relation between successive characters in a message. The start bit is always of opposite polarity to the quiescent state of the data link since its purpose is to signal the arrival of a new character. On recognising the start bit the

# FIG 3.1 TWO CHARACTERS TRANSMITTED ASYNCHRONOUSLY

FIG 3.2 SAME TWO CHARACTERS TRANSMITTED SYNCHRONOUSLY

receiving hardware has to start its bit clock, which runs at a fixed rate, and count in the requisite number of bits following to form the character, which can then be transferred in parallel form to the computer. The purpose of the stop bits, which are always of opposite polarity to the start bit, is to return the line to the quiescent state so that the start bit of the next character can be correctly recognised. Asynchronous communication is therefore essentially one-character-at-a- time message transmission, and is usually used to support the simplest kinds of data transmission system, such as typewriter terminals.

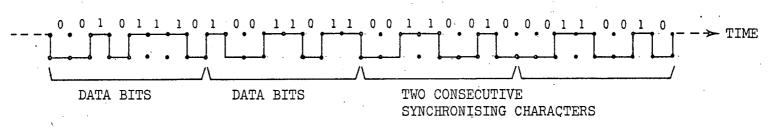

# 3.3 Synchronous communications adapter

In synchronous communications (Fig 3.2), a message is sent as a continuous stream of characters with no interval between the last bit of one character and the first bit of the following character. A message is therefore a contiguous series of bits, and in order to correctly identify the individual characters within this bit stream, the message is preceded by a number of characters of a particular non-repeating bit pattern. The receiving hardware has to recognise this bit pattern in order to lock in to the correct character frame. Once this character phase has been established, the receiving hardware has to count off the required number of bits to form each character using an appropriate clock. Because of the requirement to maintain accurate bit timing over a long message and the inherent difficulty of maintaining two independent clocks in synchronism with each other, the clocks used to provide bit timing in synchronous systems are more sophisticated than those used in asynchronous systems, where the bit clock only needs to be accurate enough to maintain bit

- 27 -

timing for one character. The synchronous receive clock has to be self-regulating in order to follow any variations in the transmit clock at the other end of the transmission link. Allowance also has to be made for apparent timing shifts caused by distortion of the bit stream by the dynamic electrical characteristics of the transmission link.

Synchronous communications is therefore essentially a blockoriented transmission system and all the characters in a message have to be present before message transmission can be started. Consequently, complete message buffering has to be provided in a terminal using synchronous communications, and, generally, sufficient levels of character buffering have to be provided to ensure that the input and output shift registers can be emptied or refreshed within the crisis time, which is always one bit time.

#### Comparison between asynchronous and synchronous communications adapters

The hardware necessary to implement synchronous communications is more complicated than that for asynchronous communications in the following ways:

- a) recognition of character synchronization pattern

- b) provision of self-regulating receive bit clock

- c) extra character and message buffering

Synchronous communications has the advantage that a given message can usually be transmitted more efficiently than with asynchronous communications. This is a consequence of the high redundancy involved in asynchronous communications with a minimum of 2 bits extra per character compared with the fixed overhead of the leading synchronization characters. All but the shortest messages will be transmitted more efficiently in synchronous mode.

# 3.4 Telegraphic signalling

A major factor affecting the economics is the equipment used for item b. This is the equipment which accepts the low voltage (about 6 volts) DC serial data and turns it into a form suitable for transmission over long distances.

The simplest implementation of this merely converts the low voltage into a much higher DC voltage (about 80 volts) which is then capable of being recognised correctly after a few miles of cable. This works on the simple principle of telegraphy and is only capable of supporting fairly low speeds (up to about 200 bauds) over a few miles of cable. The effect of the capacitance and resistance of a long length of cable is to convert the original well-shaped square waves into something like a saw-tooth shape as follows:-

If the original DC voltage is not maintained for a long enough period, the signal level at the receiving end does not reach a large enough value because of the long rise time of the pulse. Therefore, in order to ensure that the serial data can be properly reconstructed at the receiving end, the rate of change of the data being fed into the transmitted end is limited accordingly. This is the factor which limits the speed of operation with this type of signal transmission. The maximum speed is governed by the rise time of the circuit, which is dependent on its length. For circuits up to a few miles, this limits the speed to about 200 bauds. For longer circuits, signal repeaters have to be included in the circuit which re-shape the waveform before transmitting it further. To achieve higher speeds, the signal repeaters would have to be placed at shorter distances along the circuit, which would nullify the economic advantages of the very simple equipment (basically just electrical relays) needed to transmit data in this way. This type of equipment then is suitable only for the lowest data rates.

#### 3.5 Modems

All other equipments in use for signal transmission use some kind of AC transmission which uses the DC voltage levels to modulate a carrier signal of a particular frequency. AC signals are more easily transmitted over long distances because of the electrical impedance characteristics of long circuits. The increasing sophistication of the modulation techniques used is giving higher data rates from the same circuits. The equipment at the receiving end has to remove the basic carrier signal (demodulation) in order to reconstruct the original serial data streams. The equipment used at both ends to transmit and receive is therefore known as a modulator-demodulator or modem.

One of the techniques used to obtain higher speeds is to combine two or more data bits into a new multiple-value signal with which to

- 30 -

to modulate the carrier <sup>(7)</sup>. Thus, in a typical system (GPO Modem 7), one of four phase shifts is applied to the carrier in order to transmit two bits of data. The increased sophistication of the electronics required to accurately encode and decode these multiple value signals, allowing for the unavoidable distortion caused by the transmission line, means that higher data rates will cost more.

#### Distinction between synchronous and asynchronous modems

There is an important relation between modem technology and the use of synchronous or asynchronous transmission adapters.

As mentioned previously, asynchronous transmission adapters usually provide their own bit timing and can use a simple fixed rate oscillator which only needs to be accurate enough for a single character. The modem used for asynchronous transmission does not need to know the rate at which data is being transmitted or received. It is transparent to the actual bit stream and its function is merely to transmit or receive a two-valued DC signal which can change value at an unspecified rate, up to some maximum which is the limit for reliable transmission. The terminal equipment must be aware of the maximum reliable rate, but otherwise the speed can be varied by setting clocks in the customers equipment inboard of the modem at both ends. No timing information is exchanged between the equipment and the modem.

The bit timing used in synchronous transmission is more sophisticated since it must maintain correct bit synchronism over a whole message, which may be many thousand bits long. Although the bit timing circuitry may be in either the terminal equipment or the modem, it is normally included in the modem since the modem designer

- 31 -

is better able to assess the effects of particular types of line distortion on the bit stream and therefore compensate for them in the bit timing circuitry. When the bit timing is incorporated in the modem, timing information is passed from the modem to the communications adapter to tell it at what rate to transmit or receive data.

The distinction between asynchronous and synchronous communications, which is normally made at the character level, can then also be made at the bit level and modem level. Modems can be divided into asynchronous and synchronous classes, the latter class providing bit timing information to the user equipment and the former class not, in which case the user equipment provides its own timing. Because of this, asynchronous modems should be cheaper than synchronous ones.

The consequence of this distinction is that asynchronous modems are restricted to two-level modulation techniques and cannot take advantage of the multi-level modulation techniques which are being used to give increased transmission speeds. The multi-level coding can only be used where the modem controls the bit timing. Therefore, only synchronous modems can be used where higher transmission speeds are required. The maximum available speed for asynchronous modems in this country is 1200 baud (up to 1800 baud in the States), whereas speeds of 9600 baud can be obtained over equivalent circuits using synchronous modems.

It is, of course, possible to use asynchronous start/stop character framing with a synchronous modem since the modem is not aware of the character structure. This, however, would require modified or

- 32 -

completely new asynchronous communications adapters, able to accept an external timing signal from the modem, which is a feature not normally available with present asynchronous equipment.

# Modems available

Currently, modems offered by the GPO (who have a monopoly over modems using the dial-up transmission facilities) will support dialup operation at up to 1200 bauds (Modems 1 and 2) with bit timing provided by the customer equipment and private line operations at 2400 bauds (Modem 7) with bit timing provided by the modem. They have also recently announced a facility for dial-up operations at 2400 bauds (Moden 7C) provided the circuit conditions are favourable, i.e. they do not guarantee that the speed can be obtained from all exchanges and lines currently in service. Using the same private line that the GPO uses at 2400 bauds, it is possible to use more expensive proprietary modems which will operate at up to 9600 bauds, but this becomes very expensive. These speeds are adequate for all the applications considered in this report.

The cost of these modems are such that there is a steady increase in price from the Modem 1 to the Modem 7C, with the highspeed proprietary modems disproportionately more expensive.

#### <u>3.6 Electrical circuit facilities</u>

All variations of item c. in the diagram are provided by the GPO since they have a monopoly of public telecommunications facilities in this country. The situation of in-house communications which can make use of non-GPO facilities will not be considered in this report

- 33 -

since this can take advantage of specially-laid high-quality circuits, such as co-axial cables, which are not generally applicable to the telecommunications problems considered in this report.

The line facilities provided by the GPO fall into two categories dial-up facilities available through the normal voice network and private lines which use telephone circuits but which are permanently allocated and are effectively hard-wired between the two ends of the link. The former facility provides a data link of variable quality, since the circuit is routed through mechanical switching equipment and is likely to use different pairs of wires each time a call is made. The variability of the voice telephone network in terms of reliability and quality of connection, especially over long distances, is well known. A private line, because it always uses the same wires and is not routed through switching equipment will give a constant quality and the reliability is obviously very high, leaving aside accidental interference by GPO maintenance personnel. Because the circuit used for a private line is always the same, the GPO can guarantee the quality of the line in terms of its electrical transmission characteristics. The GPO offer a number of Tariffs, giving different guaranteed electrical characteristics to cover a range of possible transmission speeds. The simplest is Tariff J which is intended for use with slow-speed Telex-type terminals. The best is Tariff T which will support speeds from 2400 up to 9600 bauds using special transmission techniques. The GPO will provide special facilities for operation at 48k bauds but this is not a service normally available and will not be considered further since the speed range covered by the normal Tariffs is sufficient for all the applications considered in this report.

- 34 -

The economic considerations are as follows.

For dial-up connections, the normal STD charges apply which means that the cost depends on the distance, the time of the dos connection and the period of connection. For private lines, a fixed rental applies which is determined by the Tariff and the point-topoint distance and is independent of the amount of use made of the circuit.

The choice between the two facilities is determined by the speed required and the amount of connection time required. The latest GPO facilities provide for up to 2400 bauds using dial-up connections.

#### 3.7 Conclusions

The basic elements of data communications hardware have been described in this chapter and some general observations can be made.

The cheapest and simplest communication system for lower speed applications (up to 1200 baud) would use an asynchronous communications adapter and an asynchronous modem with a dial-up or private line of a suitable Tariff depending on the speed and the amount of connection time required.

This system, however, could not be used in an application requiring speeds higher than 1200 baud unless the asynchronous adapter was equipped with an external timing option, enabling use of the higher-speed synchronous modems. Note that this also requires that the other end of the link has the same capability, since compatible modems must be used at both ends of the link.

- 35 -

For these higher speed applications, the use of a synchronous communications adapter should be considered. This involves more complicated hardware (although the extra cost becomes less significant when compared with the increased cost of the higher-speed modems) but gives a higher useful data rate than asynchronous over the same speed line.

#### Chapter 4

# SYNCHRONOUS V. ASYNCHRONOUS FOR COMPUTER-COMPUTER COMMUNICATIONS

# 4.1 Introduction

All the major large computers support the use of serial data communication links for the attachment of remote peripherals. All of them support the use of both asynchronous and synchronous transmission so the first choice to be made in deciding how to communicate with them involves which of these two systems to use.

As mentioned in the previous chapter, asynchronous communications is suitable for applications involving the transmission of messages where there is no time relation between successive characters in the message. This makes it suitable for the connection of typewriter terminals, where the rate of data input by the human operator can be extremely variable.

Synchronous communications is inherently a block-oriented transmission system, where the successive characters in a message must be transmitted in a fixed time sequence. This necessitates the use of terminals with suitably-sized message buffers.

When the overall system implications of handling terminals are considered, the requirement for reliable and error-free transmission means that communication between computers must operate in a blockby-block mode. This distinguishes it from applications where human operators are the source and receptor of all transmitted messages. This distinction is demonstrated by the argument below.

# 4.2 Handling of transmission errors

In computer-to-computer communications, the responsibility for the correctness of the data transmission no longer lies with a human If a human operator is an inherent part of the data operator. transmission system, as is the case with typewriter terminals and alphanumeric video display terminals, this operator can monitor the correctness of the data being transmitted and can initiate intelligent action to recover from any transmission errors. The computer end of the link need perform very little recovery from any errors it detects, other than ignoring the last message and sending a message to the operator to inform him of the error. It is then up to the operator to send the message again if necessary. This aspect of human-operated terminals makes them particularly easy to handle from the point of view of the computer at the other end of the link.

When the data transmission is from one computer to another, then it is essential for the computers to monitor the correctness of the data transfer for themselves. Otherwise it would be necessary for the data to be displayed for vetting and approval by an operator, which would seriously reduce the effective data transmission rate. Furthermore, since some of the data transferred may be binary data rather than character data, it is not always p possible to display it in a form which can be intelligently checked by an operator.

- 38 -

It is also desirable if the computers can themselves initiate recovery action after detecting an error, since this gives much faster recovery response from transient error conditions, which are the usual source of errors on data transmission lines.

This again points out a difference between peripherals connected locally and those connected remotely. Any errors which occur during data transfer over a local high-speed parallel interface are considered to be fairly serious, and recovery usually requires in manual intervention. Errors during data transfer to a remote peripheral are to be expected and only merit investigation if their frequency noticiably degrades the link performance.

Automatic recovery from transmission errorscies therefore an important part of computer-to-computer communications. If automatic recovery is to be effective, then it is important to have very effective error detection. Errors are detected by adding redundant information, such as a parity bit, to a character or to a whole message, which is then checked on reception.

# 4.3 Error detection

The exact nature of data transmission link reliability in terms of susceptibility to corruption of the data is obviously highly dependent on the particular facilities used, e.g. dial-up or private line, transmission speed, the precise locality of the wires used and its routing, etc. However, a great deal of investigation has been done on this subject by a number of common carriers in different countries and it is possible to draw certain general conclusions. The most important conclusion is that while constant factors such as thermal noise cause signal distortion, suitable modem design can help to compensate for this and most data errors are caused by 'impulse noise' which results from the nature of the switching equipment used in most exchanges. Even if a private line is used, which does not involve and switching equipment, such lines are normally ordinary telephone circuits which have been specially wired point-to-point. As such they share the same cable runs as dialled circuits, and are liable to pick up impulse noise generated in adjacent circuits by dialling, etc.

Impulse noise produces a short burst of electrical interference sufficiently large to completely swamp the transmitted data signal and replace the effected bits by a random pattern. The duration of a noise pulse can be anything up to 1/100th of a second, so it is clear that several bits in a message at 2000 bauds would be affected. Experiments carried out on a long private line in Europe at 2000 bauds (9) showed that over 60% of messages in error had w 2 adjacent bits corrupted and 30% had up to 8 adjacent bits in error.

The simple conclusion to be drawn from this is that simple character parity does not give very good protection against burst errors, since two or more adjacent bits in error have an even chance of producing a bit pattern with the same parity as the corrupted bits. Therefore, message: transmission which relies on simple character parity is not well protected against localized errors, since the redundancy is also localized and the effect of an error is not propagated throughout the message.

# 4.4 Block-oriented error detection

To deal with burst errors effectively, a form of non-localized redundancy is required which is accumulated over a whole message and which will propagate the effect of a local error through to the end of the message. This type of redundancy is then a redundancy check on the message as a whole rather than on individual characters, and examples of this are longitudinal parity and cyclic redundancy check(10).

This consideration forces computer-tplcomputer communication to become message-oriented or block-oriented rather than characteroriented. Long messages have to be broken down into smaller blocks for transmission purposes, and the optimum block length is determined by the mean error rate and practical considerations of buffer size within the computers. Because of this requirement for block-oriented transmission between computers, with error detection and recovery being done on a block basis, computer-to-computer communications cannot take advantage of the inherent simplicity of using asynchronous mode as in character-oriented transmission.

For reliable and error-free transmission between computers, a rigorous scheme must be implemented to achieve automatic control of the transmission link, and the system complexity of an asynchronous link handler becomes equivalent to that for a synchronous link.

The choice between the two systems is then based on the economic and hardware complexity considerations described in the previous chapter.

- 41 -

# 4.5 Comparisons

The previous chapter indicated that the cheapest communication link was provided by a totally asynchronous system, i.e. asynchronous transmission adapter and asynchronous modem. This however had limitations if it was required to operate the link at speeds greater than 1200 baud.

This gives a maximum character rate of only 120 characters per second. This would not be adequate for a number of the applications considered in this report. To take some concrete examples, peripherals commonly used on the small computers have the following speeds:-

card reader - 300 cards per minute line printer - 300 lines per minute paper-tape reader - 300 characters per second.

Assuming that trailing blanks are not transmitted and that only about 40 leading characters per card or line are actually used for information, these peripherals generate a data rate of 200-300 characters per second. Other peripherals, such as DEC-tape or a disk, could generate an even higher rate.

Such applications are therefore not well matched to the cheapest facilities and it becomes necessary to use the higher speed synchronous modems. Assuming that the problem of interfacing an asynchronous transmission adapter to a synchronous modem at both ends of the link is amenable to a solution, which is not always so, the use of asynchronous transmission would produce a lower line utilisation than synchronous transmission by at least 25% with the minimum of 2 framing bits per character.

In these circumstances, it seems more appropriate to opt for a synchronous transmission scheme, which will make more efficient use of the higher speed modems.

Once the required data rates justify the extra cost of the higher speed modems, which can be considerable, it is important to take full advantage of the higher speeds provided. The extra cost and complexity of the synchronous communications hardware becomes less significant as the modem becomes the most expensive component in the system.

# 4.6 Conclusions

From the above arguments, the advantages of asynchronous communications are its low cost and relative simplicity when used with human-operated terminals. Since such terminals are used in large numbers, it is important to use the cheapest possible facilities, provided these are adequate. For higher-speed communications however, suitable for inter-computer working, the synchronous system has the advantage of making best use of the more expensive facilities needed.

#### Chapter 5

#### LARGE COMPUTER COMMUNICATIONS HARDWARE

# 5.1 Introduction

As has been stated previously, all the large computers considered supported the use of synchronous communications. Those considered were IBM 360, ICL System 4, Univac 1108, CDC 6600 and Burroughs B5500. The way in which these computers supported synchronous operation was then investigated in more detail to see if there was a compatible way of communicating with them all. The list above is in order of the amount of information available on detailed operation of synchronous hardware.

The first thing to become apparent was that the communications codes and protocols were implemented in very inflexible ways on most of the computers. The communications facilities were controlled very largely by hardware with very little software control. Details of control characters and their interpretation, message formats, error checking, etc., were implemented in such a way that they could not be changed by a user program.

# 5.2 Communications controllers

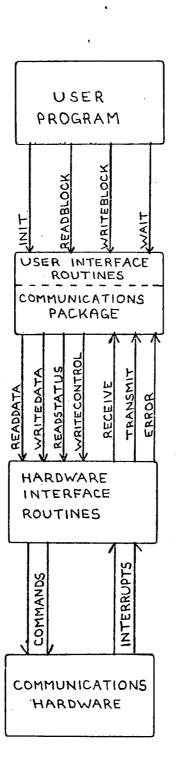

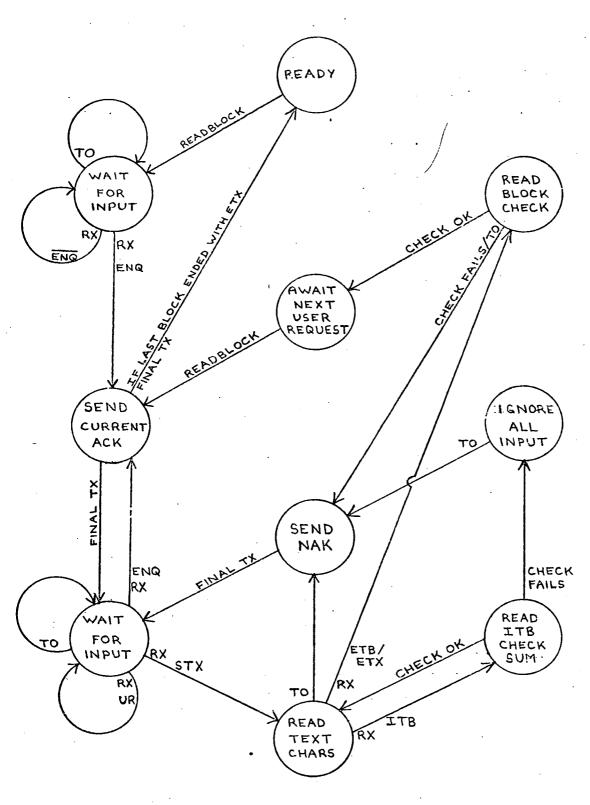

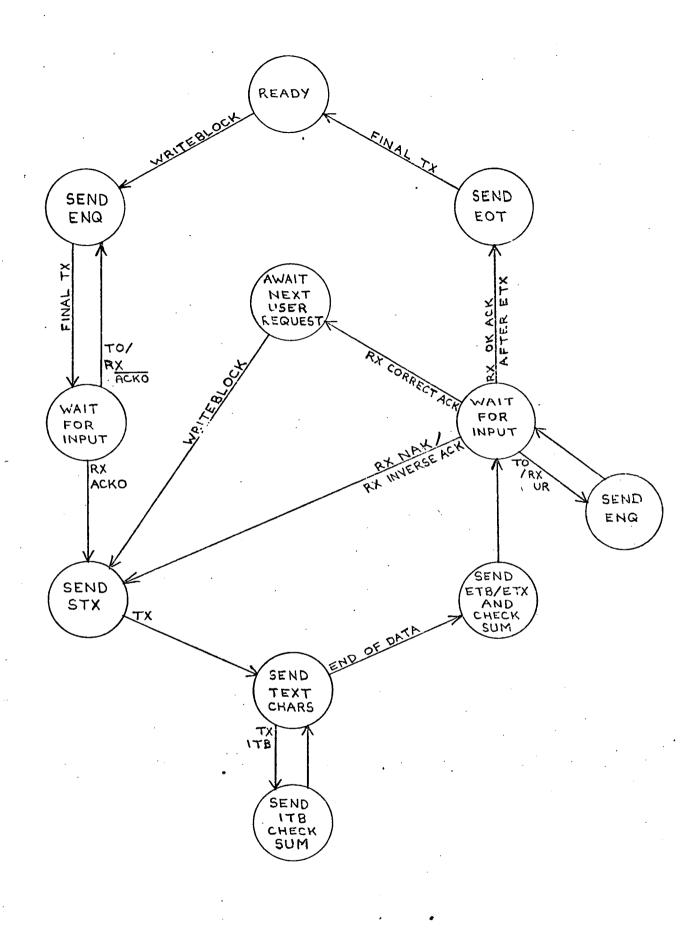

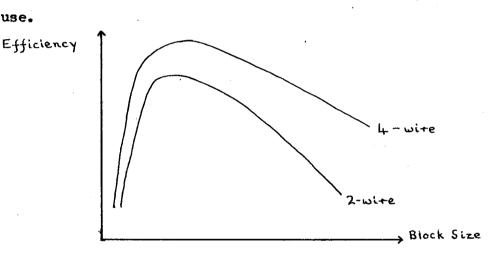

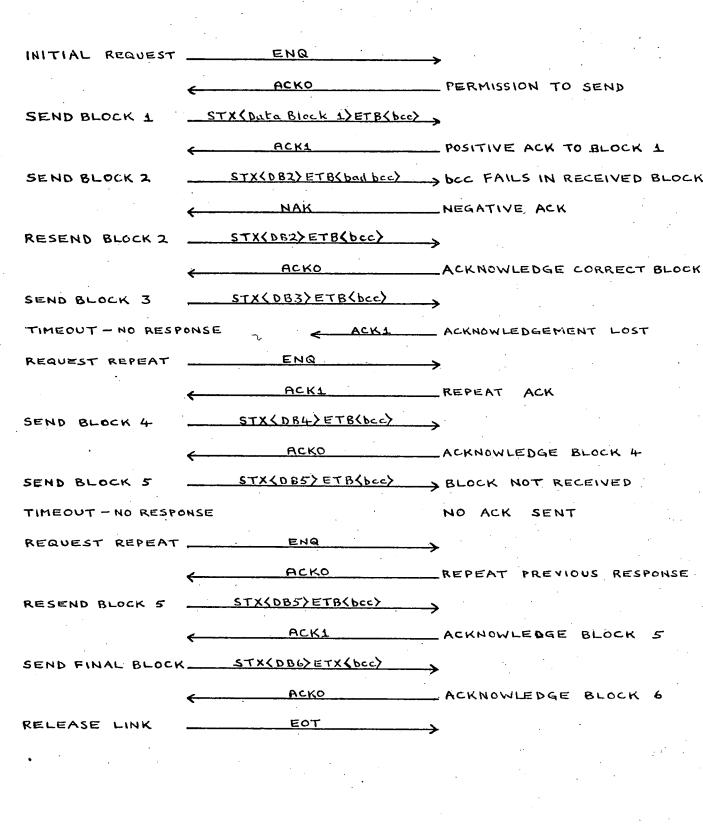

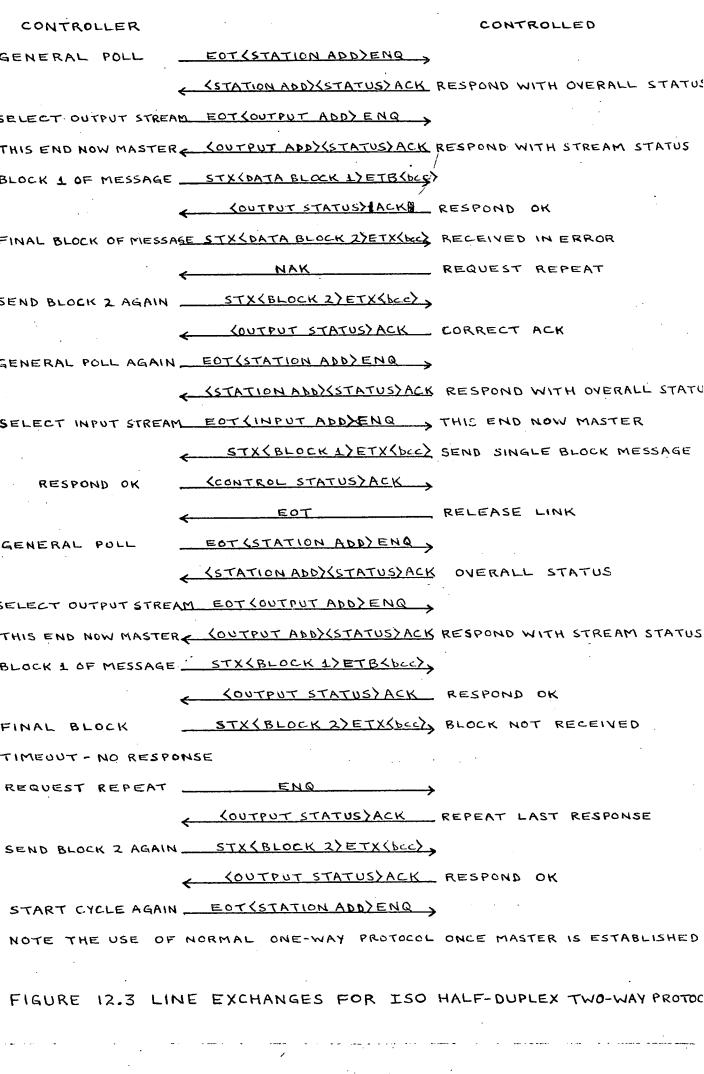

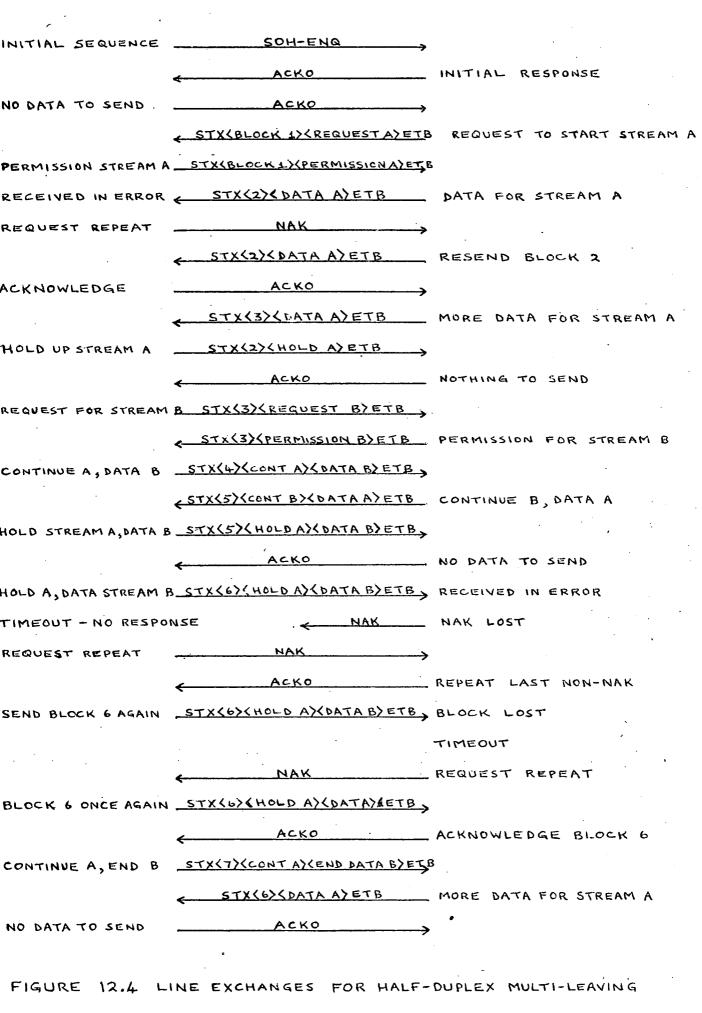

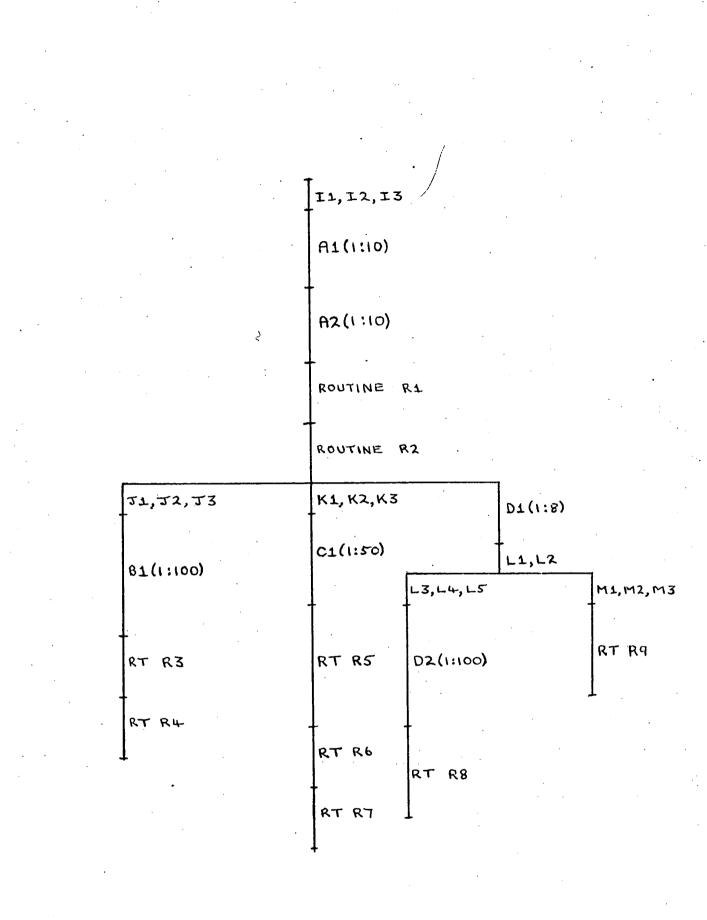

The implementations of the communications controllers varied from pure hardware on the IBM 360, through hard micro-program on the System 4 to small, special-purpose programmable processors on the CDC 6600 and Burroughs B5500. However, even on those systems which were genuinely programmable, it was not intended that the control programs should be accessible to the user for him to implement his own communications protocols. This meant that all communications controllers were effectively hard-wired to the manufacturer's defined codes and protocols.