# Burroughs

## AN INTRODUCTION TO THE BURROUGHS 5500

#### M. H. J. BAYLIS

## Contents

- 1. Summary

- 2. Introduction

- 3. System Description

- 4. Central processor

- 5. Word mode

- 6. Character mode

- 7. Interrupt handling

- 8. Finale

#### 1. Summary

The B5500 reference manual is 160 pages long with few redundant words. This description attempts to cover the same span in a shorter space by jumping over much of the detail.

## 2. Introduction

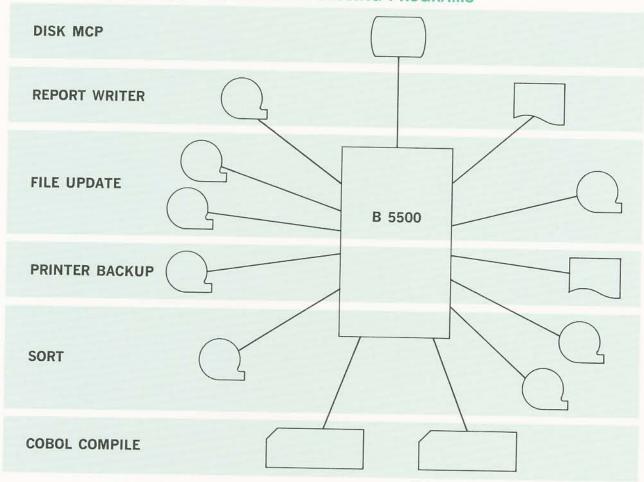

The B5500 is a problem language oriented machine. The hardware provided was designed with Algol, Fortran and Cobol in mind. Important features are that it is a 48 bit word machine with 12 bit instructions, and a complex CPU operating in word or character mode. In word mode there is a dynamic stack, the top two words of which are the arithmetic registers. The Master Control Program (MCP) is a general multiprogramming operating system; its interaction with a running program also provides automatic handling procedures to meet most processing conditions — to this extent it provides facilities which all the compilers use. Programming the machine in basic code is strongly discouraged; although the description here is necessarily at this level.

## 3. System description

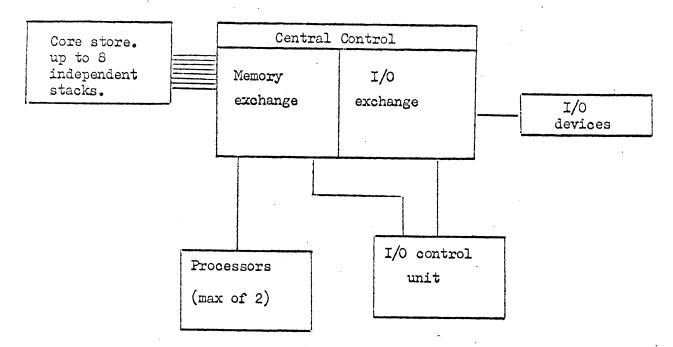

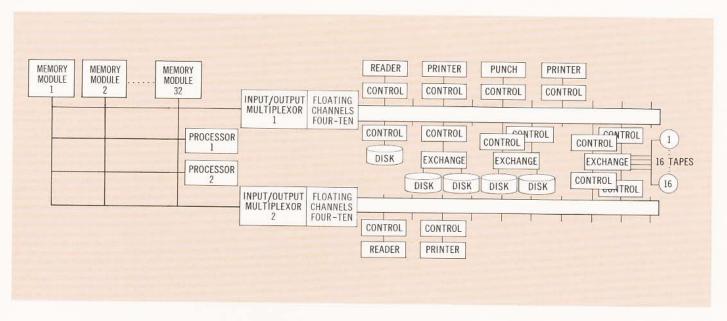

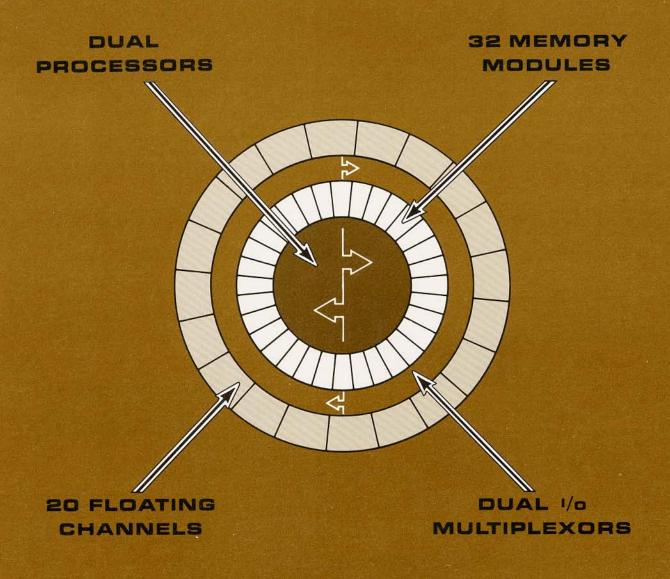

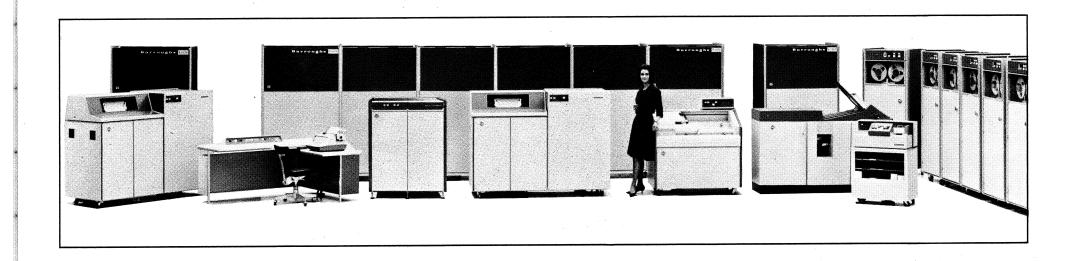

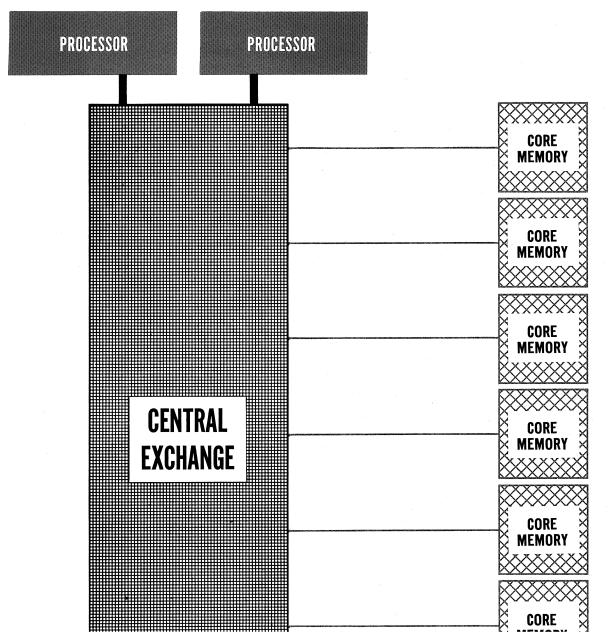

## 3.1 Major units

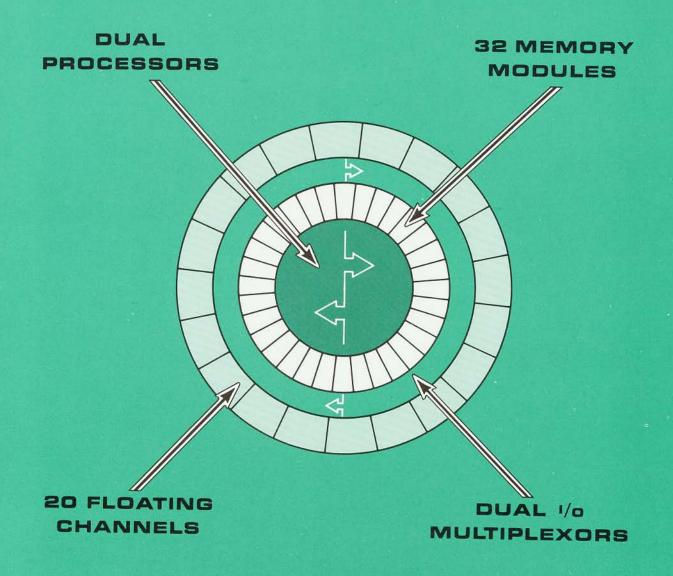

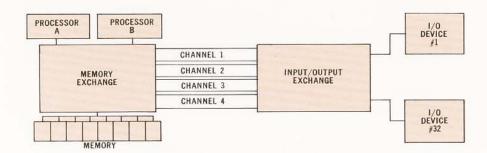

Central control unit, consisting of store access controller, input/output controller and system controller. The latter includes the master timing clock, real time clock and an interrupt system.

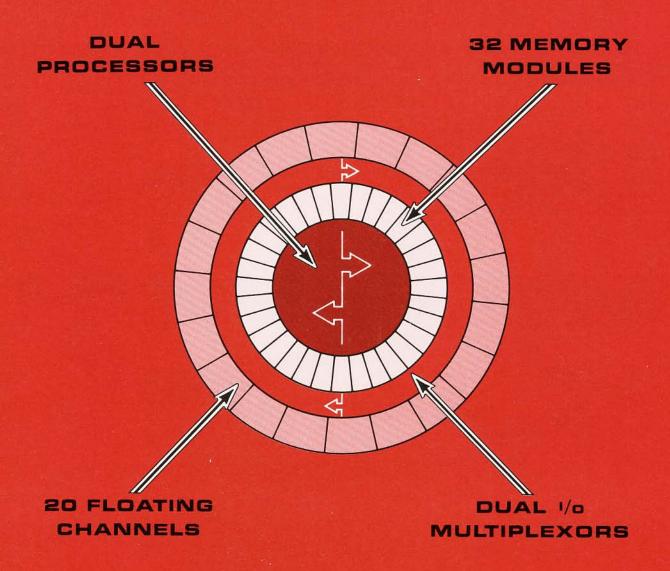

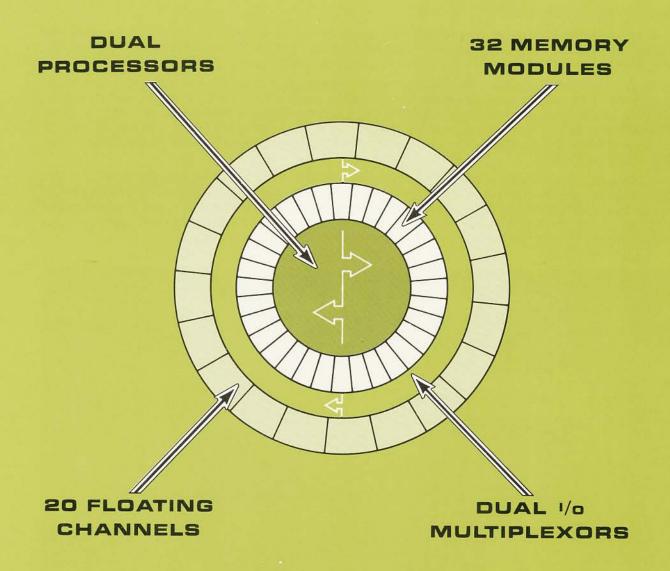

Processors. Maximum of two. If one, it will be operating in normal state or control state (interrupts inhibited, some extra functions and addressing structures active). If two, one will always be in normal state, so all interrupts go to the designated processor.

Memory modules. Up to 8 modules of 4K by 48 bits, either 6 us or 4 us cycle time.

Display and distribution unit.

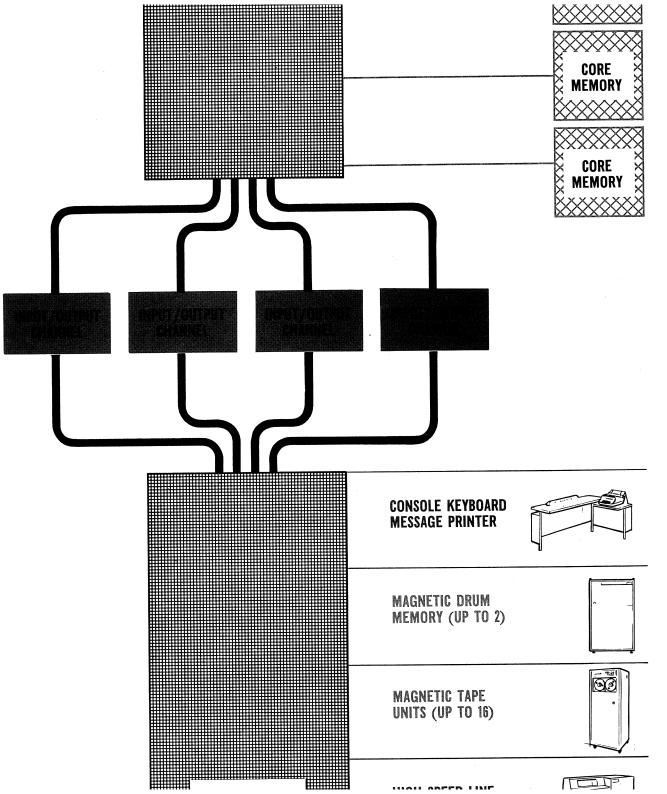

## 3.2 Peripherals

| 3.2 Peripherals       |      |                                |

|-----------------------|------|--------------------------------|

| type                  | max. | capacity/speed.                |

| drum                  | 2    | 32K                            |

| I/O channels          | 4    |                                |

| mag tape              | 16   | up to 72 Kc/s                  |

| line printers         | 2    | up to 1040 cpm, 132 char/line. |

| card readers          | 2    | up to 1400 cpm,                |

| card punch            | 1    | 300 cpm,                       |

| tape readers          | 3    |                                |

| tape punches )        | 2    |                                |

| disc file controllers | 4    |                                |

various discs

various communications equipment, multiplexors, teletypewriters etc.

## 4. Central processor outline description

Instructions (syllables) are 12 bits long, 4 to a word. In word mode, operands are 48 bit floating point numbers, on which arithmetic is performed in a parallel unit. In character mode, a word is regarded as eight 6-bit BCD characters. Operators work with single characters or one to six bits of a characters, using a serial 6-bit arithmetic unit.

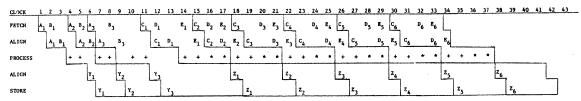

The machine is clocked at lMc/s and there is a degree of instruction overlap both in the store accessing and execution stages. In word mode, average times are add 3 /us, multiply 30/us. There is a parity bit with every 48 bit word.

There are up to four I/O control units which are independent, each able to drive any channel to a peripheral. Each control unit has a 48 bit buffer, 6-bit characters are parity checked, code translation is automatic and store access is by cycle stealing.

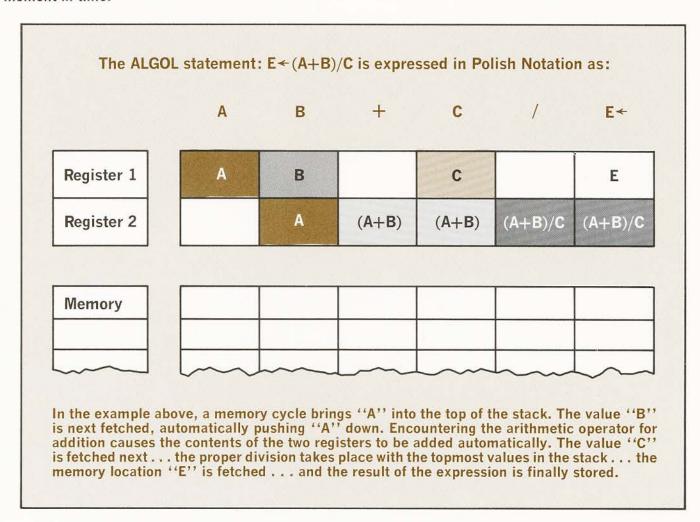

Three areas are associated with the computation part of a program. These are the Program Reference Table (PRT) which contain constants and variables, the stack and the program segment string. In word mode, all arithmetic is done at the top of the stack and it is necessary to think in Polish notation. Relative addressing is used to access all these three areas. Operands in general are numbers or descriptors. The latter describe information; for scalars they simply give an address (and type), for vectors they give address and length etc. They are discussed later. Some of the central registers are explained below; their functions are elaborated on here and later.

| Register. | Width. | Function.                                                             |

|-----------|--------|-----------------------------------------------------------------------|

| P         | 48     | current word in program segment string, containing 4 syllables.       |

| T         | 12     | the syllable from P being executed                                    |

| C         | 15     | the address of P                                                      |

| L         | 2      | address of T within P                                                 |

| NSCF      | l      | normal state ff                                                       |

| SALF      | 1      | sub-program level ff:, indicates the program has entered at least one |

| CWMF | 1  | character word mode ff. Set by a basic instruction.                                                |

|------|----|----------------------------------------------------------------------------------------------------|

| I    | 7  | Interrupt register. Switches to control state after execution of current syllable if any bits set. |

| F    | 15 | Used to record the current stack base, which alters on subroutine entry and exit.                  |

These registers operate differently in word and character mode.

|          |       | -                                                                                                                                                                                                                                                                                                                | ·                                                            |

|----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Register | Width | Word Mode                                                                                                                                                                                                                                                                                                        | Character mode.                                              |

| A        | 48    | top word of stack                                                                                                                                                                                                                                                                                                | 8 chars. of source string.                                   |

| В        | 48    | second word of stack A and B are the arithmetic registers. Most operations leave the result in B, with A invalid.                                                                                                                                                                                                | 8 chars. of destination string.                              |

| S        | 15    | address of top word of<br>the stack area in core<br>store. Ideally the<br>stack runs A,B,(S),<br>(S-1) but after<br>various operations<br>A or B or both may<br>be invalid; before<br>the next operation<br>A, B or both may<br>be reloaded from<br>the core part of the<br>stack and S adjusted<br>accordingly. | address of the destination string.                           |

| AROF     | 1     | A valid/invalid.                                                                                                                                                                                                                                                                                                 |                                                              |

| BRO F    | 1     | B valid/invalid. These two flip flops control the top of the stack logic.                                                                                                                                                                                                                                        |                                                              |

| Х        | 39    | extension of B in some arithmetic operations.                                                                                                                                                                                                                                                                    | contains a "loop control" word.                              |

| М        | 15    | <ul><li>(i) for relative address developments.</li><li>(ii) during arithmetic, for overflow bits and special counts.</li></ul>                                                                                                                                                                                   | address of source string.                                    |

| R        | 9     | address of base of PRT (m.s. 9 bits of 15 bit address)                                                                                                                                                                                                                                                           | bits 4-9 form the "tally" register.                          |

| Q12F     | 1     | Mark stack ff (MSFF)<br>see later                                                                                                                                                                                                                                                                                | True/False ff. (TFFF) gives result of last conditional test. |

These registers are for character and bit manipulation, and are also used in both modes.

| Register | Width | Function                                                          |

|----------|-------|-------------------------------------------------------------------|

| Y        | 6     | contains one char. from A                                         |

| Z        | 6     | contains one char. from B                                         |

|          |       | Y and Z are the inputs for the character serial adder.            |

| G ·      | 3     | address of char. position in A                                    |

| K        | 3     | address of char. position in B                                    |

| H        | 3     | bit address of character addressed by G                           |

| ٧        | 3     | bit address of character addressed by K H and $\forall$ count 0-5 |

| N        | 4     | records octal shifts on B                                         |

#### 5. Word mode

Syllables are grouped into four categories, recognised by the two l.s bits. (digits 10,11)

- (i) Literal call. bits 0-9 contain an integer in the range 0-1023. Thus the instruction "LITC (literal call syllable) 16" would have the effect of setting A = 16. If A was previously valid then A→B first. If B was also previously valid then S+l→S and B→(S), i.e. the stack is pushed down.

- (ii) Operator syllables. bits 0-9 define the type of operation. For single length arithmetic, the operands are A and B, the result goes to B and leaves A clear, and AROF is set so B is the new stack top. For double length arithmetic, one operand is A and B, the other is the top two words in the core part of the stack i.e. (S) and (S-1). The result is left in A and B, with S-2 -> S.

- (iii) Operand call. To place an operand on the stack.

- (iv) Descriptor call. To place an address on the stack.

These two use bits 0-9 as indices for relative addressing and to give the base address to be used. Both need rather full descriptions, which are given later.

Relative addressing. In program level (SALF=0) the base addressis always the PRT base, held in the R register. The index is then either the 10 bits in the syllable or the 1.s 10 bits in A, depending on the function. The absolute address is formed in M by addressing R and A (preloading A from the syllable where necessary). In sub-program level (SALF=1) the base can be R (for the PRT), F (for within the stack) or C (the current program word address). If R or C, the index can be positive or negative. These bits to decide base and sign are taken from the 10 available, leaving correspondingly fewer for the indexing.

Normal word mode addressing. S is always valid and controls the stack in core store, In general, B is always loaded and stored to and from the

address in S. M is used to access any other operand needed, either by it containing a developed relative address or by transferring to it an address from A.

There are three types of word that occur in the PRT and hence in the stack. These are operands, descriptors and control words.

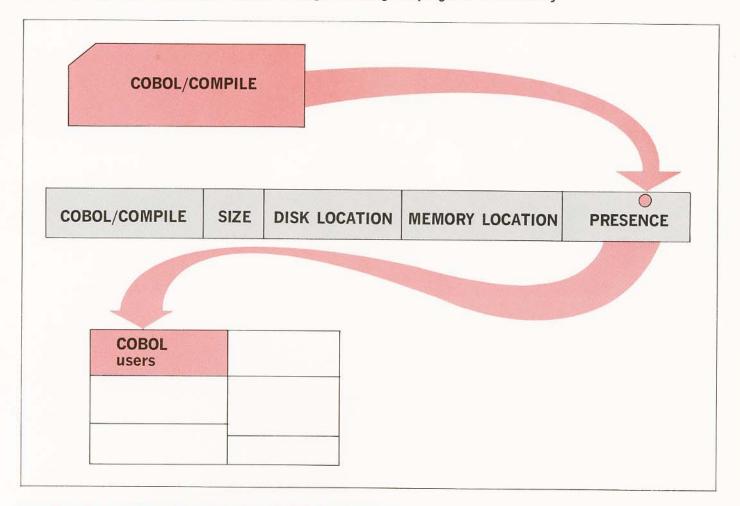

Descriptors describe some data, a program or an operation. They only occur in word mode, and there are four types, data descriptors, program descriptors, I/O descriptors and I/O result descriptors, all of 48 bits. The bits are used as follows (except for I/O results)

| bit   | use                                                                                   |

|-------|---------------------------------------------------------------------------------------|

| 0     | ⇒l if descriptor or control word                                                      |

| 1     | =0 if descriptor                                                                      |

| 2     | presence bit. If = 1 the information is present in core store.                        |

| 8-17  | word count field. (=0 if only 1 word)                                                 |

| 19    | =1 if data is type integer.                                                           |

| 20    | <pre>=l if more than one descriptor referencing multiple areas (continuity bit)</pre> |

| 33-47 | absolute address of information.                                                      |

Data areas are referenced indirectly through descriptors in the PRT. If the area is one word, the descriptor contains its address, if a vector it contains the base address and word count. For higher dimensioned arrays, there is a "Mother" descriptor giving the base address of a table of descriptors (dope vectors). These point on to more descriptors if there are more dimensions and eventually to the array elements, the word count at each level being equal to the size of the following level dimension. Any number of dimensions is allowed.

A subroutine is entered by a program descriptor (placed in the PRT during compilation). This descriptor contains a mode bit (to show whether word or character mode), and argument bit (set if arguments are needed) and the starting address of the subroutine. There is also a presence bit; if not present the MCP will be interrupted to load the relevant information.

Because subroutines also have to use the stack, and may be recursive, various facilities are provided. We have already mentioned SALF, which signifies sub-program level and allows additional relative addressing. Before entering a subroutine, the top of the stack is marked with a Mark Stack Control Word (MSCW). The parameters for the subroutine are then placed on the stack. A return Control Word (RCW) is automatically placed on top of these on entry.

The MSCW causes the A and B registers to be pushed into store, if necessary, and it contains the current values of R, MSFF, SALF and F. F was initially pointing at the base of the stack. Now it is set to the address of the word in which the MSCW is stored ready to be the stack base for the current subroutine. The RCW contains the return address and various registers (H,V,G,K,F,C). Return is automatic (via a return mormal or exit operator) and the registers are restored from the RCW and MSCW.

We can now finish the description of the operand call and descriptor call syllables.

Operand call (OPDC). After accessing the operand address, the following actions can occur, depending on the type of object fetched.

- (i) if an operand it goes to the stack top.

- (ii) if a control word it is treated as an operand.

- (iii) if a data descriptor, the word addressed by the descriptor will be placed on the stack.

- (iv) if a program descriptor, the program will branch to a subroutine, placing a RCW on the stack.

Descriptor call (DESC).

- (i) if an operand, causes a data descriptor to be generated that contains the absolute address and placed on the stack.

- (ii) if a data descriptor, it is placed on the stack.

- (iii) if a program descriptor, the action is as if the instruction was OPDC.

During these calls, rather a lot of logic is involved, which takes four pages of flow diagrams in the manual's explanation.

Without going into detail, rigorous hardware checks are made at each step on the validity of the information. For example, on accessing a data descriptor with a positive field count, the top of the stack (which is at B or (S) at this stage) is taken to contain the modifier. If this is not in integer form it is made so by forcing the exponent to zero. If this does not cause overflowand the resultant integer is less than the field count then the descriptor is altered so that the base address it contains is modified (and its field count may be set to zero). The resultant descriptor may then be either the end result or the address of the required operand.

The operators in word mode are as follows:-

#### Arithmetic

Add, subtract, multiply, divide, integer divide and remainder divide.

The first four can be single or double length.

#### Logical:-

And, or, equivalence (which is unusual I suppose) and logical negate.

#### Relational:-

These also use A and B as operands, but the result is a single bit in B, set to a one if the relationship is true. The instructions are of the form B (relationship) A, and are:-

#### Branch:

These may branch absolutely or relatively. Conditional branches test the bit in B left by the relation operators. Branch unconditionally forward/backward. Branch conditionally forward/backward. Branch return - for sub-program exit. Non zero field branches - there are four instructions of this type which test any specified field of B (1 to 15 bits in length) for zero.

#### Store:

These orders exist in two forms. Both expect the top stack word to be an address and the next to be the operand. The 'destructive' form removes both from the stack, the other removes only the address. The address may be absolute or relative. Store, Convert to int ker and store.

#### Bit Operators:

Dial A, dial B. These orders select a bit position within a character in A and B. Transfer bits. A field from A (up to the full word) is transferred to B, starting and going to the bit addresses previously dialed. Compare fields equal, low. These two comparisons are again over a specified field starting from the dialed bit addresses in A and B. Set/reset A flag bit. This flag bit is concerned with addressing technique. Set/reset/change A sign bit. Variable field isolate. This extracts a field from A and leaves it as a right justified number on the stack. Transfer fields. There are three orders which transfer fixed fields from A to B.

#### Subroutine:

Mark stack. Constructs a MSCW on the stack and sets F to its address. Exit, return normal, special return. These are all concerned with subprogram exits.

Enter character mode.

#### Stack.

Exchange. Swaps A and B - frequently needed to reposition a variable and its address in preparation for storing.

Duplicate. The top word is duplicated.

Delete top of stack.

#### Miscellaneous

Load operator, index, construct operand call, construct descriptor call, communication operator, program release, store for interrupt operator, conditional halt, set variant, etc. Most of these are too involved for this description.

#### 6. Character mode

Character mode operation is always at sub-program level. The functions of various registers are different and them is a completely different list of operators. The primary areas of memory used are the source string and the destination, both of which can be regarded as continuous strings of characters or character positions. It is possible to skip characters in either string, compare fields, add fields, place results etc.

As listed earlier, the source string is associated with A, the destination with B. All processing between the two strings uses a 6-bit adder and the Y and Z registers. Character mode addressing uses G,H,K and V along with S and M.

Character mode syllables use the l.s. 6 bits determine the operation, and the m.s 6 bits as a repeat field. This repeat field defines the number of characters or bits with which the syllable will act on, up to a maximum of 63.

When a group of syllables is to be repeated more than once, a loop is formed using two syllables - the begin loop and end loop syllables. (BNS and ENS). BNS has the effect of setting up a loop control words (LCW) in X, and ENS uses this to cycle back round the loop. The LCW is stored in X, its previous contents being stacked as loops can be nested to any depth, and contains the current value of control (L and C), the repeat count and the address of the previous control word.

#### Character operators

To recap first:

M selects the word from the source string to be placed in A.

G points at the character within the word.

H points at the bit within the character.

MGH can be regarded as a single register in so far as overflow from H (which counts 0-5) causes G to be counted up 1, and overflow from G counts M up one.

Similarly for the destination string we have SKV associated with B.

At no time is it possible to have M=S.

Transfer: these transfers may occur from any character position.

Transfer source characters, transfer program characters, transfer zone part of characters, transfer numeric part of characters, transfer blanks for non-numerics. This last operator operates on the destination string and, up to the limit of the repeat field, replaces non-numeric characters by 00's until the first numeric one is encountered.

Transfer words is the final transfer operation, this one starts on word boundaries.

#### Tests:

Test operators test a character or bit in the source stream against a predetermined character or bit held in the syllable repeat field. The tests are > , > , = , < , < , ≠ and, 'test for alphanumeric' for characters and 'test bit', which sets the true/false flip flop for bits.

#### Comparisons:

For comparing fields, which can start at any bit position. Word boundaries are ignored. The address registers are always advanced by the field length although the comparison result may have been determined earlier.

The tests are  $\rangle$ , ,  $\sim$ ,  $\langle$  and  $\neq$

#### Jumps:

Jump forward/backward, conditionally on the TFFF or unconditionally. Here the C,L registers are modified by the contents of the repeat field. Begin loop, and loop have been explained. Jump out-of-loop conditionally or unconditionally is self explanatory.

#### Skips:

There are six orders - skip forward/backwards on source/destination strings in terms of characters/bits. The skip amount is given by the syllable repeat field.

#### Address:

There are ten orders to store and call addresses in and from the stack, and to set addresses from character strings.

#### Arithmetic:

Field add/subtract. These orders operate on character strings of length given by the repeat field (i.e up to 63 characters in width), placing the result in the destination field.

#### Conversion:

Input convert converts up to eight decimal characters to a binary integer, output convert does the reverse.

#### Miscellaneous:

'set/reset' bit' sets up to 63 bits to 1/0 in the destination string starting at the selected bit address, 'set/increase/store tally' manipulates the 1.s 6 bits of the R register. 'Exit character mode'.

#### 7. Interrupt handling

Interrupts switch the machine from normal state to control state, in which state all the normal operations are still available, plus a few additional ones. In control state, interrupts are recorded but do not interfere with computing until the current interrupt has been processed.

There are two classes of interrupt, processor independent and processor dependent.

The independent ones are:-

- (a) time interval for logging and checking program running time.

- (b) other processor busy to detect errors in the other processor, if present.

- (c) line printer end-of-line signal.

- (d) I/O channel busy

- (e) I/O channel operation complete

- (f) keyboard interrupt for operators input

- (g) disc file check complete

The dependent ones are:-

- (a) core store parity

- (b) invalid address

- (c) request for program to enter control state

- (d) flag bit construct obtained instead of an operand

- (e) continuity bit multiple descriptors

- (f) invalid index i.e. exceeds field count

- (g) exponent underflow

- (h) exponent overflow

- (i) integer overflow, detected on the automatic conversion of floating point to integer form in preparation for modifying.

- (j) division by zero

- (k) program release indicates an I/O area of store is available.

- (1) stack overflow the stack is positioned below the PRT and S is checked against R, the PRT base, whenever numbers are added to the stack.

- (m) presence bit program has referred to information legally which happens to not be in core store at the time.

## The I and IAR registers

The 7 bit I register is split into two halves. The top 3 bits are set by core store parity, invalid address and stack overflow; these are the three highest priority interrupts and more than one might occur at the same time. The other 4 bits are coded, and the number set indicates one of the other interrupts classes described above — only one of which can occur at a time. A hardware register IAR (interrupt address register) is automatically set to a predetermined value for each detected interrupt, or to the highest priority one if more than one interrupt occurs. When IAR has been accessed by the control routine, it resets itself to the next priority interrupt address and so on until there are none left. These are reserved words in the core where these interrupt addresses are kept. As well as setting IAR, the control logic forces the instruction "store for interrupt" (SFI) to be executed as the next syllable. There is often a set of interrupts within a class, each with its own entry address (e.g. 4 for the 4 I/O channels).

SFI causes all the relevant registers (different in the two modes) to be recorded in control words which are placed on the stack. It then generates an interrupt control word and return word on the stack and initiates the interrupt processing routine. This exits by an instruction which restores the central registers and allows the object program to continue correctly.

I/O processing is not discussed here; the peripherals are driven by the use of control words in a way consistent with the philosophy already described.

#### 8. Finale

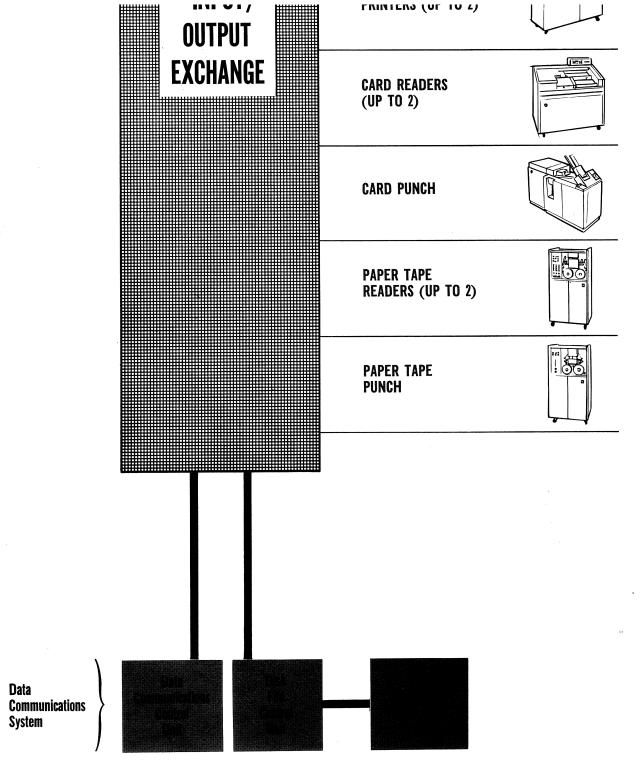

The B6500, 7500 and 8500's are elaborations of the 5500, each extending the power and flexibility and keepting the emphasis on data structures. Thus the 8500 removes I/O to separate processors, for example, and has 52 bit words so that each 48 bit word has a 3 bit descriptive tag and parity check. It also has a more generalised addressing system so a large core store can be utilised, and instructions which are multiples of 6-bits in length.

I have not been able to write and run programs for this machine and I would like to inspect the generated code from high level languages. My impressions are of elegance stemming from an aesthetically pleasing machine structure, and I would expect the underlaying philosophy to survive for many years. In my view a range of machines with the same philosophy is a better proposition than a range which is aimed to be bit compatible.

I summarise below some of the interesting features of the system:

- (i) a powerful instruction code, particularly for character and bit manipulation.

- (ii) high bit utilisation leading to compact well organised programs.

- (iii) the addressing techniques and store control system make pure procedures easy to write.

- (iv) the segmented program structure gives many desirable multi-access features, for example in allowing shared routines and data.

- (v) the protection and verification given by the descriptor logic detects diagnoses and avoids a large class of program errors.

- (vi) the store management system could be extended to cover multi-level stores, and paging or some other automatic technique could replace the present MCP software without disrupting user programs.

- (vii) because the design is based on high level language requirements, these languages should produce efficient programs.

- (viii) the operating system itself has been implemented naturally in a higher level language, and the evidence is that this has been done cheaply, efficiently and quickly.

It is hoped that this introduction provides enough information to give a general impression and to make the reference manual more readable.

## M. H. J. Baylis

## The Burroughs Scientific Processor (BSP)

DAVID J. KUCK, MEMBER, IEEE, AND RICHARD A. STOKES

Abstract—The Burroughs Scientific Processor (BSP), a high-performance computer system, performed the Department of Energy LLL loops at roughly the speed of the CRAY-1. The BSP combined parallelism and pipelining, performing memory-to-memory operations. Seventeen memory units and two crossbar switch data alignment networks provided conflict-free access to most indexed arrays. Fast linear recurrence algorithms provided good performance on constructs that some machines execute serially. A system manager computer ran the operating system and a vectorizing Fortran compiler. An MOS file memory system served as a high bandwidth secondary memory.

Index Terms—Conflict-free array access, high-speed computer, parallel computer, pipeline computer, scientific computing, vectorizing compiler.

#### I. INTRODUCTION

ROM the beginning of the Burroughs Scientific Processor (BSP) design activity, we attempted to develop a system with high performance and reliability that is practical to manufacture, easy to use, and produces high quality numerical results. It is not possible to substantiate the success or failure in achieving these goals because the product was cancelled before user installations were realized. However, a full prototype system was operational for several months on customer benchmarks and demonstrated the practicality of the architecture. A number of points of technical merit have surfaced and are presented herein.

Because of the market place for which the BSP was intended, we chose Fortran as the main programming language for the machine. This choice leads to a need for array-oriented memory and processor schemes. It also leads to various control mechanisms that are required for Fortran program execution. To design a cost-effective and user-oriented system, more than programming languages must be considered; characteristics of the types of programs to be run on the machine must be carefully considered. We have throughout the design effort paid attention to the syntax of Fortran and also the details of "typical" scientific Fortran programs.

In the past 10 years several high performance systems have been built, including the pipelined CDC STAR (CYBER-205) [12], CRAY-1 [22], MU5 [24], and TI ASC [29], as well as Burroughs Illiac IV (BBKK68) and PEPE [9], the Goodyear Aerospace STARAN [21], and the ICL DAP [10], all parallel

machines. While parallelism and pipelining are effective ways of improving system speed for a given technology (circuit and memory family, etc.), they both have shortcomings. Some pipelines perform better, the longer the vectors are that they have to process. The performance of other pipeline systems depends on vector lengths matching high-speed register set sizes. Parallel systems perform best on vectors whose length is a multiple of the number of processors available. Either type of system performs adequately if vector sizes are very large relative to the machine, but as these systems are used in wider application areas, short vector performance becomes more important. Other limitations of most pipeline processors have been that the arithmetic operations to be pipelined can reasonably be broken into only a limited number of segments and that overlapping of several instructions in one pipeline leads to unreasonable control problems.

Another important characteristic of high performance machines is the level of the language they execute. The CDC STAR and TI ASC, for example, have in their machine languages scalar and very high-level vector instructions, while ILLIAC IV, on the other hand, has a traditionally very low level machine language. A high-level machine language that is well matched to source programs can make compilation and control unit design easier and also helps ensure high system performance. A difficulty of array instructions can be that the setup time for instructions effectively stretches the pipeline length out intolerably.

#### System Overview

In the BSP we have combined parallelism and pipelining, and have provided array instructions that seem well matched to user programs. The machine has a five segment, memory-to-memory data pipeline, plus earlier instruction-setup pipeline segments. The data pipeline executes instructions that represent whole array assignment statements, recurrence system evaluations, etc., in contrast to most machines in which one or two arithmetic operations may be pipelined together. The BSP has 17 parallel memories, 16 parallel processors, and two data alignment networks. Since most instructions can be set up in the control pipeline preceding the data pipeline, instruction setup overhead should be insignificant in most cases. Thus, we have attempted to balance those architectural features that can provide good speedups with various overheads that can degrade or ruin system performance.

Another important factor in most supercomputers is I/O speed. If a very high speed processor is connected to standard disks, system performance may collapse because of I/O bound computations. The BSP has a high performance semiconductor

Manuscript received June 5, 1978; revised December 3, 1981. This work was supported in part by the National Science Foundation under Grant US NSF MCS77-27910 and the Burroughs Corporation, Paoli, PA.

D. J. Kuck is with the Department of Computer Science, University of Illinois, Urbana, IL 61801.

R. A. Stokes is with the Burroughs Corporation, Paoli, PA 19301.

file memory. This is used as a backup memory and to provide a smooth flow of jobs to and from the BSP.

Certain technological decisions were dictated by a Burroughs parallel development of a standard circuit and packaging design called Burroughs Current Mode Logic (BCML). A relatively long clock period was established in order to reduce the number of pipeline segments (for both data flow and instruction setup), avoid the complexities of high frequency clock distribution, and to facilitate manufacturing and testing the machine. The memory cycle time, the time to align 16 words between memories and processors (in either direction), and the time for many processor operations are all one 160 ns clock period; two clocks are required for floating-point addition and multiplication. In terms of these major events per clock, we attempted to lay out an array instruction set whose performance in the final system could be easily estimated during the design period.

A very important point in predicting system performance, and hence rationally choosing between design alternatives, is the determinacy of the system's behavior. We attempted to remove as much uncertainty as possible by several design choices. First, a parallel memory system was designed that provides conflict-free access to multidimensional arrays for most of the standard access patterns observed in programs. For cost reasons a parallel memory is required to achieve adequate bandwidth, and our design guarantees that for most instructions the effective bandwidth will be exactly at its maximum capacity. Since array elements are accessed in a different order from that in which they are processed, data alignment networks are needed along the path from memory to the processors and from the processors back to memory. These alignment networks also operate in a conflict-free way for most common operations. Finally, to guarantee that the memory-to-memory data pipeline is seldom broken, an array instruction set was designed. For example, a single BSP instruction can handle a whole assignment statement (with up to five right-hand side arguments) nested in one or two loops. The instruction can represent a number of 16 element slices of the operands, as long vector operations are automatically sliced and the slices overlapped in the memory-to-memory pipeline. Furthermore, as one vector assignment statement instruction ends, the next one can be overlapped with it in the pipeline. So for short vector operations there is usually no problem in keeping the pipeline full, since several different Fortran level instructions may be in operation at once.

Thus, for a wide class of instructions it was possible to predict the system performance (up to the clock speed) very early in the design process (1973). Furthermore, it has been possible during the later stages of design to make tradeoffs in these terms. Array instructions have also been very beneficial in allowing logic designers and compiler writers to communicate with each other about their own design efforts and to make tradeoffs in concrete performance terms.

A Fortran compiler has been implemented that vectorizes ANS Fortran programs, thus allowing old programs to be run without expensive reprogramming efforts. Vector extensions to Fortran are also provided to allow users to "improve" certain parts of old programs, if desired, or to write new programs in efficient ways. The vectorizer not only handles array operations, it also substantially speeds up linear recurrences—as found, for example, in processes that reduce vectors to scalars (e.g., inner product, polynomial evaluation, etc.)—and effectively handles many conditional branches within loops.

For some applications, numerical stability is a serious problem. The BSP does high quality (approximate R\*) rounding of its 36-bit mantissas and also provides double precision hardware operations. Furthermore, interrupts are generated for standard floating-point faults. Error detection and correction are provided throughout the system and automatic instruction retry is provided to ease the burden on the user in some cases.

The BSP and its file memory form a high-speed computing system that may be viewed as standing inside a computational envelope. This envelope is serviced by a system manager that can be a Burroughs B6700, B6800, B7700, or B7800. This front-end general-purpose system provides the following:

- compilation of BSP programs,

- archival storage for the BSP,

- data communication and time-sharing services to a user community,

- other languages and computation facilities.

Thus, a typical user will interactively generate compiled program and data files on the system manager, pass them to the BSP for execution, and have results returned via the system manager with permanent files maintained on the system manager's disks. Most job scheduling and operating system activities for the BSP are carried out on the system manager, so the BSP is dedicated to high-speed execution of user application programs.

#### II. SYSTEM OVERVIEW

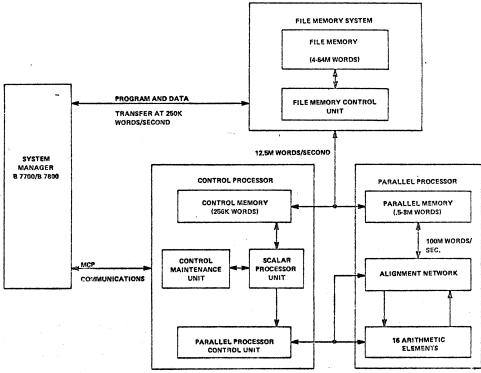

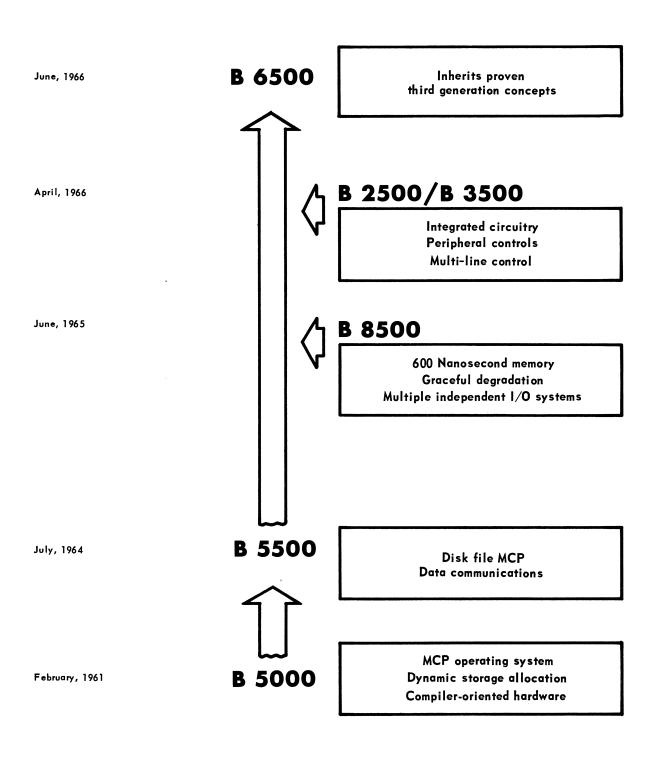

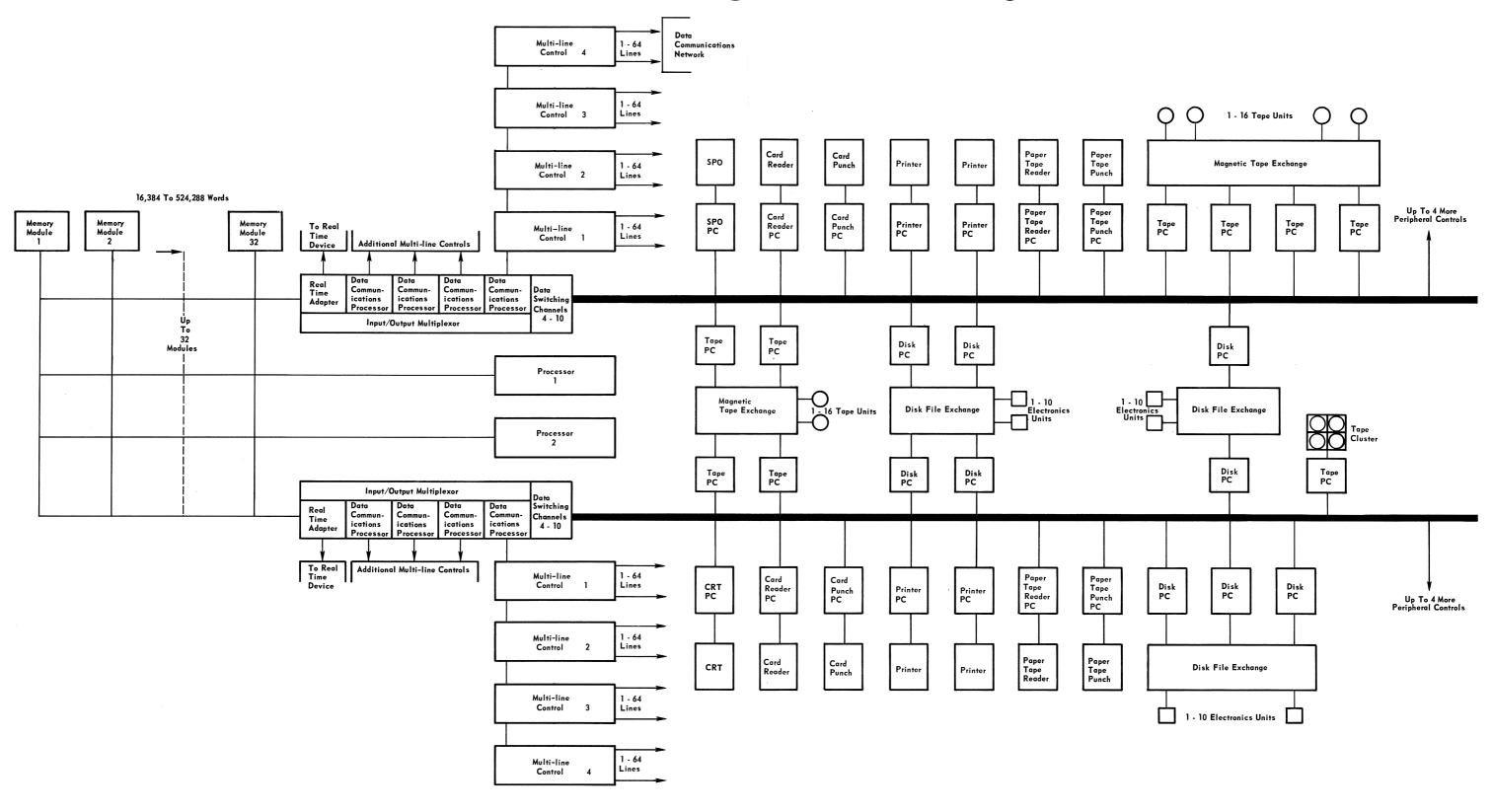

Fig. 1 shows a block diagram of the BSP and the system manager. The BSP itself consists of three major parts: the control processor, the parallel processor, and the file memory. In this section some characteristics of these parts of the BSP will be presented. In subsequent sections we will give more details about how they operate.

#### A. Control Processor (CP)

The control processor is a high-speed element of the BSP that provides the supervisory interface to the system manager in addition to controlling the parallel processor and the file memory. The CP consists of a scalar processor unit, a parallel processor control unit, a control memory, and a control and maintenance unit.

The CP executes some serial or scalar portions of user programs utilizing an arithmetic element (similar to one of the 16 arithmetic elements in the parallel processor) that contains additional capabilities to perform integer arithmetic and indexing operations. The CP also performs task scheduling, file memory allocation, and I/O management under control of the BSP operating system.

Fig. 1. BSP system diagram.

Scalar Processor Unit (SPU): The scalar processor unit processes all operating system and user program instructions that are stored in control memory. It has a clock frequency of 12.5 MHz and is able to perform up to 1.5 million floating-point operations/s. All array instructions and certain scalar operations are passed to the parallel processor control unit, which queues them for execution on the parallel processor.

Parallel Processor Control Unit (PPCU): The PPCU receives array instructions from the scalar processor unit. The instructions are validated and transformed into microsequences that control the operation of all 16 arithmetic elements in the parallel processor. Vectors of any length are handled automatically by the PPCU hardware, relieving the programmer and compiler of this burden.

Control Memory (CM): The control memory is used to store portions of the operating system and all user programs as they are being executed. It is also used to store data values that are operands for those instructions executed by the scalar processor unit. The control memory is a 4K bit/chip NMOS memory with a 160 ns cycle time. Capacity of the memory is 256K words; each word consists of 48 data bits and 8 bits for error detection and correction. Four words are accessed simultaneously, giving a minimum effective 40 ns access time per 48 bit word.

Control and Maintenance Unit (CMU): The control and maintenance unit serves as the direct interface between the system manager and the rest of the control processor for initialization, communication of supervisory commands, and maintenance. It communicates with the input/output processor of the system manager. The CMU has access to critical data paths and registers of the BSP, so that it can perform state

analysis and circuit diagnostics under control of maintenance software running on the system manager.

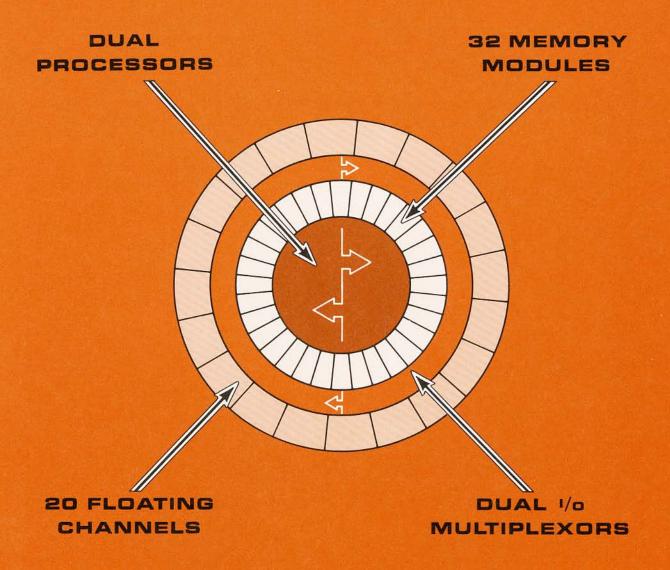

#### B. Parallel Processor (PP)

The parallel processor performs array-oriented computations at high speeds by executing 16 identical operations simultaneously in its 16 arithmetic elements. Data for the array operations are stored in a parallel memory (PM) consisting of 17 memory modules. Parallel memory is accessed by the arithmetic elements through input and output alignment networks. A memory-to-memory data pipeline is formed by the five steps (fetch, align, process, align, store) and overlap in the pipeline provides significant performance benefits.

Parallel Memory (PM): The parallel memory is used only to hold data arrays for the parallel processor and consists of 17 memory units, each of which may contain from 32K to 512K words, making a total of from 0.5 to 8 million words. It is a 4K bit/chip NMOS memory with a 160 ns cycle time as in the control processor memory. Each word contains 48 data bits and 8 bits for error detection and correction. The maximum rate of data transfer between the PM and the arithmetic elements is 108 words/s. The organization of the PM permits simultaneous access to most commonly referenced components of an indexed array, such as rows, columns, or diagonals. For some operands the compiler must choose between allocating storage in PM or CM, and performance can suffer if this is not done properly.

The Alignment Networks (AN): The BSP has two alignment networks: the input alignment network for data fetching and the output alignment network for data stores. Both units contain full crossbar switching networks as well as hardware

for broadcasting data to several destinations and for resolving conflicts if several sources seek the same destination. This permits general-purpose interconnectivity between the arithmetic array and the memory storage modules. It is the combined function of the memory storage scheme and the alignment networks that supports the conflict-free capabilities of the parallel memory. The output alignment network is also used for interarithmetic element switching to support special functions such as the data compress and expand operations and the fast Fourier transform algorithm.

Arithmetic Elements (AE): At any time all of the arithmetic elements are executing the same instruction on different data values. The arithmetic elements operate at a clock frequency of 6.25 MHz and are able to complete the most common arithmetic operations in two clock periods. Each arithmetic element can perform a floating-point add, subtract, or multiply in 320 ns, so the BSP is capable of executing up to 50 million floating-point operations/s. Each arithmetic element can perform a floating-point divide in 1280 ns and extract a square root in 2080 ns.

#### C. File Memory (FM)

The file memory is a high-speed secondary storage device that is loaded by the system manager with BSP tasks and task files. These tasks are then queued for execution by the control processor. The FM is also used to store scratch files and output files produced during execution of a BSP program. It is the only peripheral device under the direct control of the BSP; all other peripheral devices are controlled by the system manager.

The FM utilizes high-speed semiconductor memory as its storage medium; it combines a 1 ms access time with a 12.5M word/s transfer rate. Since it is entirely semiconductor, the reliability of the file memory is much greater than that of conventional rotating storage devices.

#### III. LANGUAGES AND THEIR TRANSLATION

The BSP can be regarded as a high performance Fortran machine, although many of the ideas in the design are useful for various languages. In this section we present some details of the vector form language seen by the PPCU and discuss how vector forms can be obtained from Fortran programs by a vectorizing compiler. The essential elements of many numerical algorithms are represented by these vector forms and numerical programs in most languages could be reduced to the same set of vector forms. However, the large collection of Fortran programs existing in the numerical computation community has dictated that the primary language of the BSP be Fortran. Nevertheless, vector extensions to Fortran are provided so that users may write new programs in a more convenient language than Fortran, and also to allow faster translation and possibly faster executable BSP code. We conclude this section with a sketch of the BSP vector Fortran extensions.

#### A. Vector Forms

The parallel processor control unit sequences the five stages of the data pipeline: fetch, align, process, align, store (FAPAS). In this pipeline several instructions corresponding to Fortran statements may be in execution at one time. To clarify this process, several definitions are required; these will lead to an understanding of the parallel processor control unit and compiler.

The BSP has a total of 64 vector forms that may be grouped in the following four types:

- 1) array expression statements,

- 2) recurrence and reduction statements,

- 3) expand, compress, random store, and fetch, and

- 4) parallel memory transmissions to and from control memory and file memory.

Array expression statements include indexing and evaluating right-hand side array expressions ranging from monad to pentad (five right-hand side operands), plus the assignment of the resulting values to parallel memory. A separate vector form exists for each possible parse of each right-hand side expression. The array operations are performed in an element by element fashion and allow scalars and array variables of one or two dimensions to be mixed on the right-hand side. For example,

DO 5

$$I = 1, 30$$

DO 5  $J = 7, 25$

5  $X(I, J) = (A(I, J + 1) * 0.5 + B(I + 1, J))$

$*X(I, J + 1) + C(J)$

would be compiled as a single vector form. This vector form can be regarded as a six-address instruction that contains the four array arithmetic operation specifications and the assignment operation.

Recurrence vector forms correspond to assignment statements with data dependence loops. For example,

DO

$$3I = 1, 25$$

$Y(I) = F(I) * Y(I - 1) + G(I)$

has a right-hand side that uses a result computed on the previous iteration. This recurrence produces an array of results, while others lead to a scalar result and are called *reductions*. For example, a polynomial evaluation by Horner's rule leads to the reduction

$$P = C(O)$$

DO 5  $I = 1, 25$

$P = C(I) + Y * P$ .

Both of these are recurrences that can be represented by a linear system of the form x = Ax + b, where A is a lower triangular matrix with a single band, one diagonal below the main diagonal, and x is an unknown vector. We will refer to a linear recurrence of dimension n and order m as an R(n, m) recurrence, where n is the dimension of the matrix A and m + 1 is the bandwidth of matrix A. Thus, the above program leads to an R(25, 1) system. Fast efficient algorithms exist for solving such systems and the R(n, 1) solver of [7] and [23] for small n and the R(n, 1) solver of [6] for large n have been built into the BSP. For wider bandwidth recurrences the column sweep

algorithm [15] is more efficient and it is used in the BSP. However, the user is not concerned with any of these considerations, since the vector forms described have array control unit hardware for their direct execution, as we shall see shortly.

Note that all recurrences would have to be executed serially without these algorithms. With them, R(n, m) systems (1 <  $m \le 16$  will obtain speedups proportional to m. For m = 1 and n of moderate size (say, 50 to 100), a speedup of 5 to 6 can be obtained, with greater speedups for large n. By speedup we mean time reduction compared to a hypothetical BSP with just

The third type of vector forms involves various sparse array operations. For example, in the case of a Fortran variable with subscripted subscripts, e.g., A(B(I)), no guarantee can be made concerning conflict-free access to the array A. In this case the indexing hardware generates a sequence of addresses that allows access to one operand per clock and these are then processed in parallel in the arithmetic elements. These are called random store and random fetch vector forms. Sparse arrays may be stored in memory in a compressed form and then expanded to their natural array positions using the input alignment network. After processing, the results may be compressed for storage by the output alignment network. These are called *compressed vector operand* and *compressed* vector result vector forms and they use control bit vectors that are packed, such that one 48 bit word is used for accesses to three 16 element vector slices.

A list illustrating the above three classes of vector forms is found in Table I. The mnemonics and comments should give an idea of what these vector forms do.

The fourth class of vector forms is used for I/O. Scalar and array assignments are made to control memory and parallel memory depending on whether they are to be processed in the scalar processor unit or the parallel processor, respectively; however, it is occasionally necessary to transmit data back and fourth between these memories. Transmissions to file memory are standard I/O types of operations.

These four types of vector forms comprise the entire set of array functions performed by the BSP. At the vector form level, the array processor may be regarded as arbitrarily large; thus, vector code generation is simplified in the compiler because it can transform Fortran programs into objects that map. easily into vector forms, as we shall see shortly. However, in most Fortran programs some parameters are not defined at compile time (e.g., loop limits), so some run-time source language processing remains. This is carried out by the scalar processing unit of the control processor, and when it is finished the parallel processor is controlled by a template sequencing mechanism (see Section IV-D).

Vector forms are very high-level instructions with many parameters. For example, an array expression statement vector form corresponds to an assignment statement parse tree and leads to the execution of up to four operations on operands that may be combinations of scalars and one- or two-dimensional arrays. The following is a sketch of how the scalar processing unit (SPU) initiates the execution of a vector form in the parallel processor control unit (PPCU).

Consider a triad vector form

$RBV, Z = (A op_1 B)op_2 C, OBV$

where Z, A, B, and C are vector descriptors,  $op_1$  and  $op_2$  are operators, and RBV and OBV are optional result and bit-vector descriptors, respectively. Bit vectors may be used to specify the elements of an array to be operated on or stored; they are optional (but not shown) for a number of the entries in Table I. In executing the triad, the SPU issues the following sequence of instructions that describe the vector form to the PPCU:

VFORM TRIAD, op1, op2

OBVRBVVOPERAND A VOPERAND B

VOPERAND C

VRESULT Z.

The VFORM instruction contains bits that name the first template (see Section IV-D) to be executed, specify actual operator names, indicate the presence of bit-vectors, and specify the program countercontents; it also contains other synchronization and condition bits. The OBV and RBV descriptors give the bit-vector starting addresses and lengths. The VOPERAND and VRESULT instructions give the start of the vector relative to an array location, the location of the array, the volume of the array, the skip distance between vector elements to be accessed, and optionally the skip distance between the start of subsequent vectors in a nested pair of loops. The VFORM instruction is preceded by a VLEN instruction that specifies the level of loop nesting and array dimensions. At this point, all source language parameters have been bound and run-time source language processing ends. The remaining processing done by the PPCU, e.g., array bounds checking, is the same for all operations. We shall return to a discussion of template sequencing in Section IV.

#### B. Fortran Vectorizer

In ordinary Fortran programs it is possible to detect many array operations that easily can be mapped into BSP vector forms. This is accomplished in the BSP compiler by a program called the Fortran vectorizer. We will not attempt a complete description of the vectorizer here, but we will sketch its organization, emphasizing a few key steps. For more discussion of these ideas, see [15], [17], and [4].

First, consider the generation of a program graph based on data dependences. Each assignment statement is represented by a graph node, and directed arcs are drawn between nodes to indicate that one node is to be executed before another. Algorithms for data dependence graph construction are well known [1], [4] and will not be discussed here. It should be observed that some compilers have used naive algorithms, for example, checking only variable names. The BSP algorithm does a detailed subscript analysis and thus builds a high quality graph with few redundant arcs, thereby leading to more array operations and fewer recurrences.

#### TABLE I

#### Vector Forms

|                       | Vector Forms                                                                                                                                                                                  |                                                                                                                    |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

|                       |                                                                                                                                                                                               |                                                                                                                    |

| MONAD                 | It accepts one vector set operand, does one monadic operation on it and produces one vector set result.                                                                                       | Z + op A                                                                                                           |

| DYAD                  | It accepts two vector set operands, does one operation on them and produces one vector set result.                                                                                            | Z + A op B                                                                                                         |

| VSDYAD                | It is similar to the DYAD except that operand B is a scalar.                                                                                                                                  | Z + A op B                                                                                                         |

| EXTENDED DYAD         | It accepts two vector set operands, does one operation and produces two vector set results.                                                                                                   | (Z1,Z2) + A op B                                                                                                   |

| DOUBLE PRECISION DYAD | It accepts four vector set operands (i.e., two double precision operands), performs one operation and produces two vector set results.                                                        | (Z1,Z2) + (A1,A?)<br>op (B1,B2)                                                                                    |

| DUAL-DYAD             | It accepts four vector set operands, does two operations and produces two vector set results.                                                                                                 | Z + A op <sub>1</sub> B<br>Y + C op <sub>2</sub> D                                                                 |

| TRIAD                 | It accepts three vector set operands, does two operations and produces one vector set result.                                                                                                 | Z + (A op <sub>1</sub> B) op <sub>2</sub> C                                                                        |

| TETRAD1               | It accepts four set operands, does three operations and produces one vector set result.                                                                                                       | $z \leftarrow ((A \text{ op}_1 B) \text{op}_2 C)$ $\text{op}_3 D$                                                  |

| TETRAD2               | It is similar to the TETRAD1 except for the order of operations.                                                                                                                              | Z + (A op <sub>1</sub> B)op <sub>2</sub> (C op <sub>3</sub> D)                                                     |

| PENTAD1               | It accepts five vector set operands, does four operations and produces one vector set result.                                                                                                 | $Z \leftarrow (((A \text{ op}_1 \text{ B}) \text{ op}_2 \text{ C})$ $\text{op}_3 \text{ D}) \text{op}_A \text{ E}$ |

| PENTAD2               | It is similar to the PENTAD1 except for the order of operations.                                                                                                                              | $z + ((A \text{ op}_1 \text{ B})\text{op}_2$ $(C \text{ op}_3 \text{ D}))\text{op}_4 \text{ F}$                    |

| PENTAD3               | It is similar to the PENTAD1 except for the order of operations.                                                                                                                              | z + ((A op <sub>1</sub> B)op <sub>2</sub> C)                                                                       |

|                       |                                                                                                                                                                                               | op <sub>3</sub> (D op <sub>4</sub> E)                                                                              |

| AMTM                  | It is similar to the MONAD and is used to transmit from parallel memory to control memory.                                                                                                    | Z + op A                                                                                                           |

| TMAM                  | It accepts 6 vector set operands from control memory to transmit to parallel memory.                                                                                                          | $Z \leftarrow A1(0,0), A2(0,0)$<br>A3(0,0), A4(0,0),<br>A5(0,0), A6(0,0)                                           |

| COMPRESS              | It accepts a vector set operand, com-<br>presses it under a bit vector operand<br>control and produces a vector set result.                                                                   | X + A, BVO                                                                                                         |

| EXPAND                | It accepts a vector operand, expands it under a bit vector control and produces a vector set result.                                                                                          | x + v, bvo                                                                                                         |

| MERGE                 | It is the same as the EXPAND except that the vector set result elements corresponding to a zero bit in BV are not changed in the parallel memory.                                             | X + V, BVO                                                                                                         |

| RANDOM FETCH          | It performs the following operation $Z(j,k) \leftarrow U(I(j,k))$ , where U is a vector and I is an index vector set.                                                                         |                                                                                                                    |

| RANDOM STORE          | It performs the following operation $X(I(j,k)) + A(j,k)$ , where X is a vector and I is an index vector set.                                                                                  | -                                                                                                                  |

| REDUCTION             | It accepts one vector set operand and produces one vector result given by $X(i) \leftarrow A(i,0)$ op $A(i,1)$ op $A(i,2)$ op $A(i,$ where op must be a commutative and associative operator. | 3) A(i,L),                                                                                                         |

#### TABLE I (CONTINUED)

| DOUBLE-PRECISION<br>REDUCTION | It accepts two vector set operands (one double-precision vector set) and produces two vector results (one d.p. vector) given by $(X_1(i),X_2(i)) + (A_1(i,0),A_2(i,0))$ op $(A_1(i,1),A_2(i,1))$ op $(A_1(i,L),A_2(i,1))$ op |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                             | where op must be a commutative and associative operator. $^{A_{2}(\text{i},L)),}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GENERALIZED DOT<br>PRODUCT    | It accepts two vector set operands and produces one vector result given by X(i) + {A(i,0) op <sub>2</sub> B(i,0)} op <sub>1</sub> {A(i,1) op <sub>2</sub> B(i,1)} op <sub>1</sub> {A(i,L) op <sub>2</sub> B(i,L)},                                                                                                                                                                                                                                                                                                                                                |

|                               | where op <sub>1</sub> must be a commutative and associative operator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RECURRENCE-1L                 | It accepts two vector set operands and produces one vector result given by X(1) + ({{(B(1,0) op <sub>1</sub> A(1,1)) op <sub>2</sub> B(1,1)} op <sub>1</sub> } op <sub>1</sub> A(1,L))                                                                                                                                                                                                                                                                                                                                                                            |

|                               | where $op_2$ can be ADD or IOR and $op_1$ can $op_2$ $B(i,L)$ be MULT or AND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PARTIAL REDUCTION             | It accepts one vector set operand and produces one vector set result given by $Z(1,j) + Z(i,j-1)$ op $A(i,j)$ , where op must be a commutative and associative operator.                                                                                                                                                                                                                                                                                                                                                                                          |

| RECURRENCE-1A                 | It accepts two vector set operands and produces one vector set result given by $Z(i,j) + \{Z(i,j-1) \text{ op}_1 A(i,j)\} \text{ op}_2 B(i,j),$                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                               | where op <sub>1</sub> can be MULT or AND and op <sub>2</sub> can be ADD or IOR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

As an example, consider the following program:

DO 5

$$I = 1, 25$$

1  $A(I) = 3 * B(I)$

DO 3  $J = 1, 35$

3  $X(I, J) = A(I) * X(I, J - 1) + C(J)$

5  $B(I) = 2 * B(I + 1)$ .

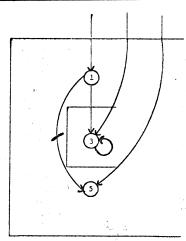

A dependence graph for this program is shown in Fig. 2, where nodes are numbered according to the statement label numbers of the program. Node 1 has an arc to node 3 because of the A(I) dependence and node 3 has a self-loop because X(I, J-1) is used one J iteration after it is generated. The crossed arc from node 1 to node 5 is an antidependence arc [16] indicating that statement 1 must be executed before statement 5 to ensure that B(I) on the right-hand side of statement 1 is an initial value and not one computed by statement 5. Arcs from above denote initial values being supplied to each of the three statements: array B to statements 1 and 5, and array C to statement 3. The square brackets denote the scope of loop control for each of the DO statements.

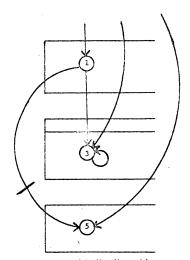

Given a data dependence graph, loop control can be distributed down to individual assignment statements or collections of statements with internal loops of data dependences. In our example there is one loop (containing just one statement) and two individual assignment statements. After the distribution of loop control, the graph of Fig. 2 may be redrawn as shown in Fig. 3.

The graph of Fig. 3 can easily be mapped into BSP vector forms. Statements 1 and 5 go into array expression statement vector forms directly since they are both dyads. Had they had more than five right-hand side variables, their parse trees would have been broken into two or more array expression statement vector forms and joined by a temporary array assignment. Statement 3 can be split into 25 independent re-

Fig. 2. Data dependence graph.

Fig. 3. Graph with distributed loop control.

currence systems, each with a bandwidth of 1 caused by the J-1 to J dependence, resulting in 25 independent R(35,1) systems, each of which maps into a recurrence vector form. Alternatively, it can be computed as a series of 35 array expression statement vector forms (triads). The maximum speed choice is made based on the loop limits.

The above cases are rather simple constructs, but they are typical of those found in existing Fortran programs. Several kinds of more complex cases are possible. If arrays with subscripted subscripts occur, they are compiled using the random fetch or store vector forms mentioned earlier. If recurrences with nonlinear right-hand sides occur, e.g., X(I) = A(I) \* X(I-1) \* X(I-2) + B(I), then serial code is compiled. To this point we have ignored conditional statements inside loops, another problem that in the past has caused serial code to be compiled.

A number of IF statements can in fact be handled in parallel in the BSP. For a theoretical discussion of various types of IF's, see [14], where examples and measurements of the frequency of various types of IF's are presented. It turns out that many of the commonly found IF's can be handled in the BSP by using standard vector forms which include bit vectors. In this way, certain IF statements can be combined with assignment statements in a single vector form. For example, consider the following program:

DO 1

$$I = 1, 92, 2$$

DO  $J = 1, 46$

1 IF  $(A(I, J).LT.0) B(I, J) = A(I, J) * 3.5$ .

This loop can be mapped into a single array expression statement vector form with bit-vector control that performs the parallel tests and makes the appropriate assignments to B(I, J). By using loop distribution, many of the IF's found in ordinary Fortran programs can be transformed into such vector operations that allow substantial speedups on the BSP. Of course, there is also a residual set of IF's that must be compiled as serial code.

A traditional objection to array computers was that too many of the statements found in ordinary programs could not be vectorized and would have to be executed in a traditional sequential manner. In the BSP a combination of software and hardware innovations has led to a system that avoids most of these traditional objections. Of primary software importance are the distribution of loop control, fast algorithms to solve linear recurrences, and the vectorization of 1F statements. Also of key importance is a good test for data dependence between subscripted variables, the appropriate introduction of additional subscripts to variables of lower dimension than their depth of loop nesting, and the transformation of scalar expressions inside loops as well as their substitution into subscripts. After a source program has been mapped into vector forms it is ready for execution.

#### C. Fortran Language Extensions

To provide users with language conveniences for writing new programs and to allow rewriting old programs that are difficult to vectorize automatically, several language extensions are being provided in the BSP software. Some of these extensions are also part of the proposed new ANS Fortran. The extensions may be categorized in four cases as array description, array operation, control, and I/O statements; we shall deal with them in that order, providing only a quick sketch of the ideas.

Arrays may be declared with the colon notation, using positive and negative subscripts, e.g., REAL A(0:3, 0:3, -3:3) declares a  $4 \times 4 \times 7$  array. Portions of declared arrays may be renamed for easy reference using an ARRAY statement as the following example shows:

REAL

$$A(100, 100)$$

ARRAY ROW  $2(J = 1:100) = A(2, J)$ ,

DIAG $(I = 1:100) = A(I, I)$

identifies ROW 2 as a vector consisting of the second row of A and DIAG as the main diagonal of A. No storage is allocated or data are moved by an ARRAY statement, only additional array descriptors are created.

Array operations can be specified in various ways. If A and B are declared arrays, then A=0 sets all elements of A to zero and B=B+1 adds 1 to all elements of B. If A is two-dimensional, then A(\*,0)=2 sets column zero of A to 2. Arithmetic, relational, and logical operators may be applied to pairs of arrays that are congruent, in which case element by element operations are performed. Furthermore, bit-vectors may be used to control array operations by use of the WHERE statement as follows. Assume that A and B are 500 element vectors, then

WHERE(

$$A.GE.0$$

)  $B = B + A$

is equivalent to

DO

$$10 I = 1,500$$

$10 \text{IF } (A(I).GE.0) B(I) = B(I) + A(I).$

This is generalized to a block-structured WHERE DO that contains a sequence of OTHERWISE statements and ends with an END WHERE. PACK and UNPACK statements are provided to allow sparse arrays to be compressed and expanded, respectively; multidimensional arrays may be packed into vectors based on logical tests. There is also an IF-THEN-ELSE construct and an END DO that does not require a label in its DO statement. For scalars or congruent arrays, the exchange statement

$$A = B$$

exchanges A and B in memory.

A collection of intrinsic functions is also provided, one set generalizes the standard scalar intrinsics to arrays (e.g., transcendental functions of the elements of an array) and the other set provides some standard array operations (e.g., dot product, matrix product, max of an array, etc.).

User programs can control I/O without supervisor intervention and without buffering by using the DIRECT statement which names an array that appears in a following READ statement. Execution of statements after the READ continues simultaneously with the input until the DIRECT named variable is encountered on the right-hand side of an assignment statement, at which point execution is suspended until the READ is completed.

#### IV. SYSTEM OPERATION