# Intel

#### For People Who Take Computing Seriously

Feedback Write to Byte

Newsletter Sign Up Now

BYTE Categories Previous Weeks Columns Features Audio

Search: Byte Research Center

Print Archives

By Issue By Topic

Resources Downloads

Java: Columns & Resources Books More Books Java One Audio Report

History Of Byte: Part I Part II Part III

BYTE Humor Ian Shoales' Page

About Us Byte Editorial Staff Feedback Sales Staff Privacy Policy

Sponsored by:

#### TechWeb Sites

Byte.com

CMPmetrics

Data Communications

File Mine

InformationWeek

InternetWeek

ARTICLES

BYTEMARKS FACTS

### **Beyond Pentium II**

December 1997 / Cover Story / Beyond Pentium II

Here's the first detailed look at the new breakthrough microprocessor architecture from Intel and Hewlett-Packard -- and what it will mean for developers and users.

Tom R. Halfhill

For Intel and Hewlett-Packard, the year 2000 isn't a problem — it's an opportunity. In late 1999, Intel plans to ship Merced, the first microprocessor based on a next-generation architecture jointly conceived by the two companies. Although this 64-bit architecture builds on years of research at Intel, HP, other companies, and universities, it is radically different from anything ever attempted on a mass-market scale. Whether it succeeds or fails, one thing is certain: It will change the computer industry forever.

Known as Intel Architecture-64 (IA-64), the new definition breaks clean with the past in a startling fashion. IA-64 is emphatically not a 64-bit extension of Intel's 32-bit x86 architecture. Nor is it an adaptation of HP's 64-bit PA-RISC architecture. IA-64 is something completely different -- a forward-looking architecture that uses long instruction words (LIW), instruction predication, branch elimination, speculative loading, and other advanced techniques to extract more parallelism from program code.

Although Intel and HP promise backward compatibility with today's x86 and PA-RISC software, they're still withholding those details. Compatibility will not be trivial because IA-64 goes far beyond the 32-bit extensions that Intel added to the x86 in 1985, as well

Network Computing Planet IT TechShopper TechWeb News Tele.com WebTools Winmag.com as the 64-bit extensions that HP added to PA-RISC in 1996. It's worth remembering that the x86's much less radical transition from 16 to 32 bits has so far taken 12 years and still is not complete.

The migration to IA-64 won't concern most users in the short term, however, because Intel says it's designing Merced for high-end servers and workstations. Merced is not for mainstream PCs. In fact, Intel says IA-64 won't replace the x86 "for the foreseeable future." It's likely that Intel (and other x86 vendors) will continue to introduce new generations of x86 chips for years to come.

#### Superwide CPUs

Before plunging neck-deep into the technical innards of IA-64, it is critical to understand why Intel and HP are gambling their futures on such sweeping changes. It comes down to this: Intel and HP think CISC and RISC are running out of gas.

Intel's x86 is an ancient CISC architecture that dates back to 1978. In those days, CPUs were scalar devices (able to execute only one instruction at a time) with little or no pipelining. Chips had tens of thousands of transistors. HP's PA-RISC architecture dates back to 1986, when superscalar (multiple-instruction) pipelines were just starting to sprout and chips had hundreds of thousands of transistors. In the late 1990s, leading-edge processors have millions of transistors.

By the time Merced makes its debut, Intel will be rolling out the next generation of process technology beyond today's latest 0.25-micron process -- 0.18-micron. Even the first IA-64 chips will have tens of millions of transistors. Future generations will have hundreds of millions.

CPU architects are eager to put those transistors to work. They want to design chips with many more functional units -- that execute more instructions in parallel -- but they're hitting a wall of complexity. As they add more units to make the CPU "wider," they must also add more control circuitry to dispatch those instructions to the units. Today's best CPUs can't retire more than four instructions per clock and already waste too much silicon on this purely bookkeeping logic.

At the same time, the sequential nature of program code and the frequency of branches make it increasingly difficult to dispatch instructions in parallel. Today's CPUs devote enormous amounts of logic to minimizing branch penalties and to extracting as much hidden parallelism as possible from the code. CPUs reorder instructions on the fly, predict where branches will jump, and speculatively execute instructions beyond the branches. If the CPU guesses wrong, it must discard the speculative results, flush the pipelines, and reload the correct instructions — paying a heavy penalty in lost cycles. CPUs that theoretically can retire four instructions per clock actually average less than two per clock.

To compound these problems, memory chips haven't come close to matching the s oaring clock speeds of CPUs. When Intel designed the first x86 chip, CPUs could fetch data from memory as fast as they could process the data. Today, CPUs spend hundreds of clock cycles waiting for data to arrive from memory, despite having large, fast caches.

Intel and HP are addressing all these problems. Here's what they divulged in two lengthy interviews with BYTE:

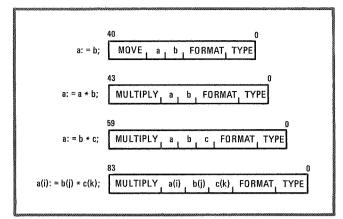

● The new IA-64 format packs three instructions into a single 128-bit-long bundle for faster processing. Usually this is called LIW encoding, but Intel shuns that label, saying LIW has "negative connotations." For the same reason, Intel does not like to describe the individual instructions as "RISC-like," even though they are fixed-length and presumably optimized for single-cycle execution in a core that doesn't need microcode. Intel calls its new LIW technology Explicitly Parallel Instruction Computing, or EPIC.

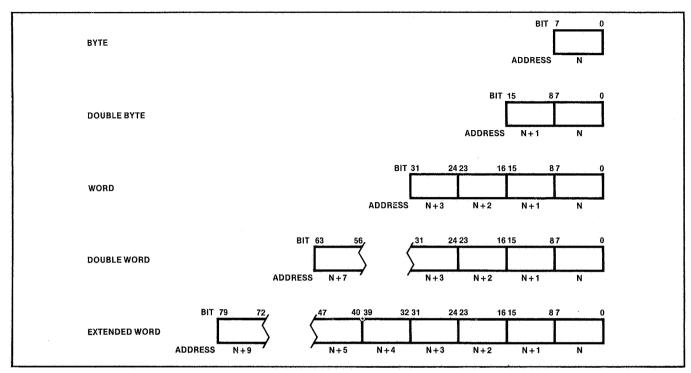

At any rate, IA-64 is nothing like the x86. An x86 instruction is a single unit that can vary from 8 to 108 bits long, and the CPU must tediously decode each instruction while scanning for the instruction boundaries. (See the figure "IA-64 Instruction Format" .)

Each 128-bit IA-64 bundle contains a template of several bits -- placed there by the compiler -- that explicitly tells the CPU which instructions it can execute in parallel. No longer must the CPU hurriedly analyze the instruction stream at run time to uncover hidden parallelism. Instead, the compiler identifies the parallelism and binds this information into the machine code.

Each instruction contains three 7-bit general-purpose register (GPR) fields, and the fields are specific to integer and floating-point (FP) instructions. That means IA-64 processors will have 128 integer-type GPRs and 128 FP registers. All are programmer-visible, random-access registers. Compare that to the constipated x86, which has eight integer GPRs and an eight-entry FP stack. IA-64 processors can be much wider and will stall less often due to false dependencies (e.g., shortages of registers).

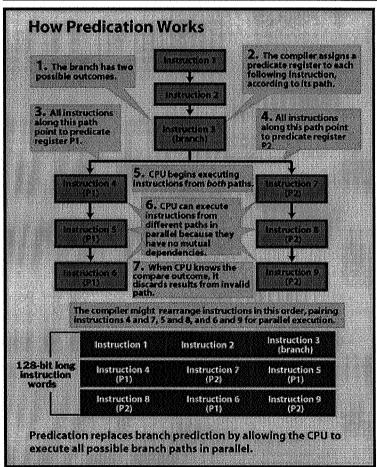

- IA-64 compilers will use a technique called *predication* to remove the penalties caused by mispredicted branches and the need to jump over blocks of code beyond branches. When the CPU encounters a predicated branch at run time, it will begin executing the code along all destinations of the branch, exploiting as much parallelism as possible. When the CPU discovers the actual branch outcome, it stores the valid results and discards the others.

- IA-64 compilers will scan the source code to find upcoming loads from memory, then will add a speculative load instruction and a speculative check instruction. At run time, the first instruction loads the data from memory before the program needs it. The second instruction verifies the load before letting the program use the data. Speculative loading helps hide the long latencies of memory accesses and helps increase parallelism.

One implication of IA-64 is that compilers will have to be a lot smarter about the microarchitectures of the CPUs they target. Existing chips -- even RISC chips with optimized compilers -- do much more optimizing at run time than IA-64 chips will. IA-64 transfers the job of optimizing the instruction stream to the compiler. Successive generations of IA-64 processors will run older IA-64 software, but the software might not run at top speed until it's recompiled. In the IA-64 age, developers might have to ship multiple binaries to get the best performance on a broad installed base of IA-64 systems.

Another impact will be code expansion. IA-64 instructions are longer than 32-bit RISC instructions -- about 40 bits each. Just by recompiling existing code,

developers will almost certainly see their programs grow larger. And those programs will probably take longer to compile because IA-64 demands a lot more work from the compiler, as we'll see in a moment. Intel and HP say they're already working with tool vendors to help them revise their products.

#### Dis appearing Branches

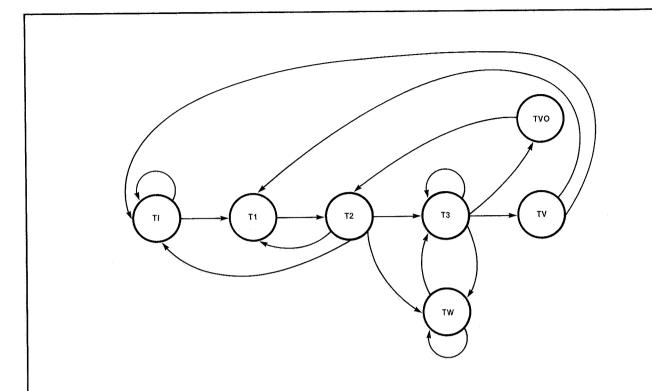

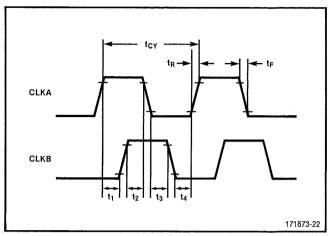

Predication is a prime example of the new burden shifted onto compilers. This technique is central to IA-64's branch elimination and parallel instruction scheduling.

Normally, a compiler turns a source-code branch statement (such as IF-THEN-ELSE) into alternate blocks of machine code arranged in a sequential stream. Depending on the outcome of the branch, the CPU will execute one of those *basic blocks* by jumping over the others. Modern CPUs try to predict the outcome and speculatively execute the target block, paying a heavy penalty in lost cycles if they mispredict. The basic blocks are small, often two or three instructions, and branches occur about every six instructions. The sequential, choppy nature of this code makes parallel execution difficult.

When an IA-64 compiler finds a branch statement in the source code, it analyzes the branch to see if it's a candidate for predication. Compilers can't predicate every branch: Dynamic method calls that the CPU won't discover until run time are one obvious exception. In other cases, predication might cost more cycles than it saves. Compilers will have to be clever about this.

If the compiler determines that predication makes sense, it marks all the instructions that represent each path of the branch with a unique identifier called a *predicate*. For example, the compiler might tag each instruction that follows the TRUE condition with the predicate P1; and it might tag each instruction that follows the FALSE condition with the predicate P2. IA-64 defines a 6-bit field in each instruction to store this predicate. Thus, there are 64 unique predicates available at one time. Any number of instructions that share a particular branch path will share the same predicate.

After tagging the instructions with predicates, the compiler determines which instructions the CPU can

execute in parallel. Again, this requires the compiler to know a lot about the CPU's microarchitecture, because different IA-64 chips will have different numbers and types of functional units. Also, of course, the compiler must watch out for data dependencies — an operation that needs the result of a previous operation cannot execute in parallel with that operation. But the compiler will almost always find some parallelism by pairing instructions from different branch outcomes because they represent independent paths through the program.

Now the compiler can start assembling the machine-code instructions into 128-bit bundles of three instructions each. The bundle's template field not only identifies which instructions in the bundle can execute independently but also which instructions in the following bundles are independent. So if the compiler finds 16 instructions that have no mutual dependencies, it could package them into six different bundles (three in each of the first five bundles, and one in the sixth) and flag them in the templates.

The bundled instructions don't have to be in their original program order, and they can represent entirely different paths of a branch. Also, the compiler can mix dependent and independent instructions together in a bundle, because the template keeps track of which is which. Unlike some previous very-long instruction word (VLIW) architectures, IA-64 does not insert null-operation instructions (NOPS) to fill slots in the bundles.

At run time, the CPU scans the templates, picks out the instructions that do not have mutual dependencies, and then dispatches them in parallel to the functional units. The CPU then schedules instructions that are dependent according to their requirements.

When the CPU finds a predicated branch, it doesn't try to predict which way the branch will fork, and it doesn't jump over blocks of code to speculatively execute a predicted path. Instead, the CPU begins executing the code for every possible branch outcome. In effect, there is no branch at the machine level. There is just one unbroken stream of code that the compiler has rearranged in the most parallel order.

At some point, of course, the CPU will eventually evaluate the compare operation that corresponds to the IF-THEN statement. Now the CPU knows the outcome. Let's say the condition is TRUE, so the valid path is

predicate P1, not P2. The 6-bit predicate field in each IA-64 instruction refers to a set of 64 predicate registers (P0-P63), and each register is 1 bit wide. The CPU will store a 1 in predicate register P1 to represent TRUE, and it will store a 0 in predicate register P2 to represent FALSE.

By this time, the CPU has probably executed some instructions from both possible paths. But it hasn't stored the results yet. Before taking that final step, the CPU checks each instruction's predicate register. If the register contains a 1, the instruction is valid, so the CPU retires the instruction and stores the result. If the register contains a 0, the instruction is invalid, so the CPU discards the result. (See the figure "How Predication Works".)

Predication effectively remove s the negative impact of a branch at the machine level while preserving branch behavior. Again, it can't remove every branch. However, if the compiler cannot predicate a branch, or chooses not to, an IA-64 processor will behave much like a conventional processor: It will try to predict which way the branch will turn, and it may speculatively execute some instructions along the predicted path. Simulations of this strategy indicate that predication can eliminate more than half of the branches in a typical program -- and therefore reduce by half the number of potential mispredictions.

This has several benefits. It reduces code fragmentation at the machine level because the compiler can merge small basic blocks into larger blocks that branches don't chop up. Larger blocks give the compiler more freedom to rearrange instructions for parallel execution. It also drastically reduces the hazard of mispredicted branches because every branch doesn't require the CPU to play fortune-teller. And it keeps the function al units busy because the CPU can dispatch more instructions in parallel.

The downside of predication is that the CPU always executes instructions it's going to throw away. Whether the predicated condition evaluates TRUE or FALSE, the CPU does perform redundant work. The trick, of course, is to make sure the CPU saves more clock cycles than it wastes. Clearly, predication assumes that IA-64 compilers will be smart and that IA-64 processors will be very wide superscalar chips with lots of resources to spare. When you're rich, you can afford to spend lavishly.

#### He Ain't Heavy, He's My Data

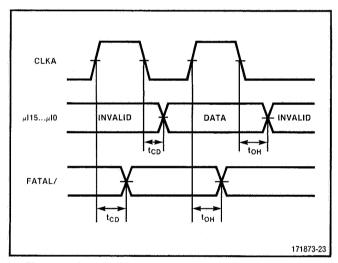

Another key feature of IA-64 is speculative loading. Not only will this allow IA-64 processors to load data from memory before the program needs it, it will also postpone the reporting of exceptions if the load is not legal. In geekspeak, this technique allows the CPU to *hoist* the load operation higher in the instruction stream -- in some cases, even above a branch.

The goal is to separate the loading of data from the use of that data. By paying attention to this, the CPU won't have to twiddle its thumbs while waiting for data in slow memory to show up. Like predication, it's a combination of compile-time and run-time optimizations.

First, the compiler analyzes the program, looking for any operations that will need data from memory. Whenever possible, the compiler inserts a speculative load instruction at an earlier point in the instruction stream, well ahead of the operation that will actually use the data. The compiler also inserts a matching speculative check instruction immediately before the particular operation that will use the data. At the same time, of course, the compiler rearranges the surrounding instructions so that the CPU can dispatch them in parallel.

At run time, the CPU encounters the speculative load instruction first and tries to retrieve the data from memory. Here's where an IA-64 processor differs from a regular processor. Sometimes the load will be invalid -- it might belong to a block of code beyond a branch that has not executed yet. A traditional CPU would immediately trigger an exception. If the program could not handle the exception, it would likely crash.

But an IA-64 processor won't immediately report an exception if the load is invalid. Instead, the CPU postpones the exception until it encounters the speculative check instruction that matches the speculative load. Only then does the CPU report the exception. By then, however, the CPU has resolved the branch that led to the exception in the first place. If the path to which the load belongs turns out to be invalid, then the load is also invalid, so the CPU goes ahead and reports the exception. But if the load is valid, it's as if the exception never happened. (See the figure "How Speculative Loading Works".)

Speculative loading is similar to the TRY-CATCH structures in some programming languages, except that it works at the machine level. In Java, for instance, a TRY statement will attempt a risky operation, such as opening a file. If TRY succeeds, the program continues normally. If the system can't open the file and throws an exception, CATCH grabs it and stops the program from crashing. IA-64's speculative check is a safety valve for exceptions, like CATCH.

This technique, combined with predication, gives the compiler much more flexibility to reorder instructions and increase parallelism. The ability to hoist loads above branches is particularly powerful. Since branches typically occur about every six instructions, they would severely inhibit IA-64's ability to load data from memory long before it's needed. It would be almost impossible to retrofit an existing architecture with these features because the compiler and the CPU must collaborate to make it happen.

#### **Beyond RISC**

In the heady days of the 1980s, some RISC engineers ridiculed CISC and foretold the doom of the x86 family. Unfortunately for them, the penalty for underestimating Intel is even greater than the penalty for mispredicting branches. Business and technology are two different things. RISC might be technically superior to CISC, but Intel's vast resources and the momentum of DOS and Windows have kept the x86 competitive.

Now, Intel says RISC is running out of gas. Could it be that Intel might be making the same mistake that RISC fans made in the 1980s? Will RISC stave off the IA-64 challenge?

It's too early to tell. However, it's doubtful that RISC vendors can tap the same depth of resources that keeps the x86 alive. The most popular RISC architecture (not counting embedded applications) is the PowerPC. And the only high-volume PowerPC vendor is Apple, a company struggling for survival. Without more business, how long can RISC vendors justify the expensive research and development it takes to battle Intel?

IA-64 chips are still two years away. Intel's competitors -- from both the RISC and the CISC camps -- have that much time to take the offensive.

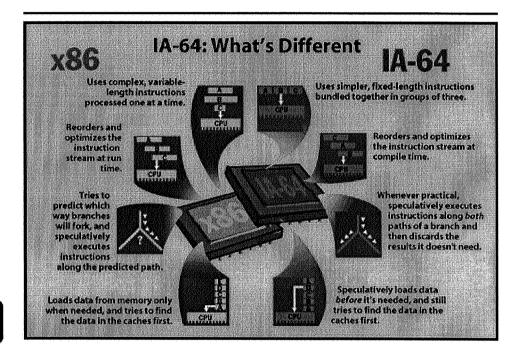

#### IA-64: What's Different

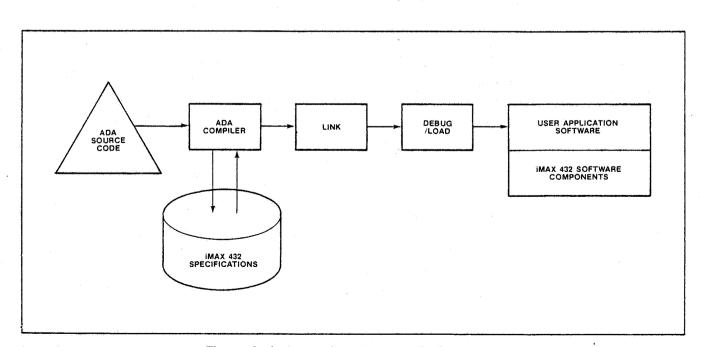

illustration\_link (53 Kbytes)

#### **IA-64 Instruction Format**

illustration\_link (39 Kbytes)

#### **How Predication Works**

illustration\_link (37 Kbytes)

#### **How Speculative Loading Works**

illustration\_link (39 Kbytes)

Tom R. Halfhill is a BYTE senior editor based in San Mateo, California. You can reach him at thalfhill@byte.com.

Making an educated network purchasing decision has just gotten easier

# Do you want Integrated Products?

Byte

Feedback Write to Byte

Newsletter Sign Up Now

BYTE Categories Previous Weeks Columns Features Audio

Search: Byte Research Center

Print Archives

By Issue By Topic

Resources Downloads

Java: Columns & Resources Books More Books Java One Audio Report

History Of By Part I Part II

BYTE HumorSearch Ian Shoales' Page

About Us

Byte Editorial Staff

Feedback

Sales Staff

Privacy Policy

#### TechWeb Sites

Byte.com CMPmetrics Data Communications File Mine InformationWeek InternetWeek

# ARTICLES BYTEMARKS FACTS HOTBYTES VPR TALK

#### IA-64: What's Different

#### Byte

Feedback Write to Byte

Newsletter Sign Up Now

BYTE Categories Previous Weeks Columns Features Audio

#### Search:

Byte Research Center

Print Archives

By Issue By Topic

#### Resources Downloads

Java: Columns & Resources Books More Books Java One Audio Report

History Of Byte: Part I Part II Part III

#### BYTE Humor Ian Shoales' Page

#### About Us Byte Editorial Staff

Feedback Sales Staff Privacy Policy

#### TechWeb Sites

Byte.com

CMPmetrics

Data Communications

File Mine

InformationWeek

InternetWeek

# BYTE

#### ARTICLES BYTEMARKS FACTS HOTBYTES VPR

#### TAIK

#### **How Predication Works**

### Performance Characterization of the Pentium® Pro Processor

## Dileep Bhandarkar and Jason Ding Intel Corporation

Santa Clara, California, USA

#### **Abstract**

In this paper, we characterize the performance of several business and technical benchmarks on a Pentium® Pro processor based system. Various architectural data are collected using a performance monitoring counter tool. Results show that the Pentium Pro processor achieves significantly lower cycles per instruction than the Pentium processor due to its out of order and speculative execution, and non-blocking cache and memory system. Its higher clock frequency also contributes to even higher performance.

Keywords: Pentium® Pro processor, computer architecture, performance evaluation, workload characterization, out of order execution, speculative execution, SPEC CPU95, SYSmark/NT.

#### 1. Introduction

The Intel Pentium® Pro processor was disclosed in February 1995 at ISSCC [1] and began shipping later that year. The micro-architecture implements several new features that are not found in previous implementations of the Intel Architecture. This paper analyzes the major performance characteristics of several business and technical benchmarks on a Pentium Pro processor based system. Measurements were performed using the built-in performance counters of the processor. Results are presented for cycles per instruction, cache miss statistics, branch prediction statistics, speculative execution, stall cycles, and other micro-architecture features.

Current literature contains numerous papers that present simulations of various machine structures. Often these simulations do not model the entire machine accurately or only use traces of parts of popular benchmarks. We present measured characteristics of a recent microprocessor to allow researchers to calibrate their theoretical results. The paper presents a lot of raw data and some analysis wherever possible. In a modern superscalar out-of-order processor, it is not always possible to derive precise cause-effect relationships.

Some of the results presented here are consistent with the behavior of SPEC benchmarks on other architectures, e.g., the FP benchmarks have lower Icache misses and higher Dcache misses than the integer benchmarks. Other measurements (branch mispredicts, micro-op statistics, and speculative execution) provide insight into the inner workings of the Pentium Pro processor.

## 2. Architectural Features of the Pentium® Pro Processor

The Intel Pentium Pro processor implements dynamic execution using an out-of-order, speculative execution engine, with register renaming of integer, floating point and flags variables, multiprocessing bus support, and carefully controlled memory access reordering. The flow of Intel IA-32 Architecture instructions is predicted and these instructions are decoded into micro-operations (uops), or series of uops. These uops are registerrenamed, placed into an out-of-order speculative pool of pending operations, executed in dataflow order (when operands are ready), and retired to permanent machine state in source program order. This is accomplished with mechanism to handle unexpected general asynchronous events such as mispredicted branches, instruction faults and traps, and external interrupts. Dynamic execution, or the combination of branch prediction, speculation and micro-dataflow, is the key to its high performance.

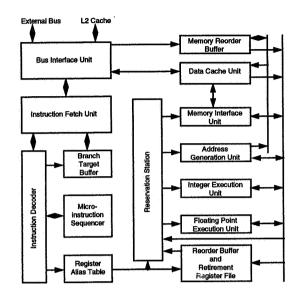

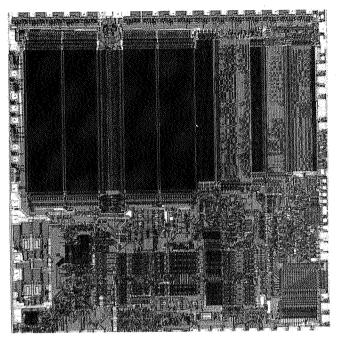

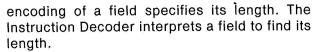

Figure 1 shows a block diagram of the processor. The basic operation of the microarchitecture is as described in the ISSCC paper [1]:

- The 512 entry Branch Target Buffer (BTB) helps the Instruction Fetch Unit (IFU) choose an instruction cache line for the next instruction fetch. Icache line fetches are pipelined with a new instruction line fetch commencing on every CPU clock cycle.

- Three parallel decoders (ID) convert multiple Intel Architecture instructions into multiple sets of uops each clock cycle. Instructions that require more than 4 uops are handled by the microinstruction sequencer.

- 3. The sources and destinations of up to 3 uops are renamed every cycle to a set of 40 physical registers by the Register Alias Table (RAT), which eliminates register re-use artifacts, and are forwarded to the 20-entry Reservation Station (RS) and to the 40-entry ReOrder Buffer (ROB).

- 4. The renamed uops are queued in the RS where they wait for their source data this can come from several places, including immediates, data bypassed from just-executed uops, data present in a ROB entry, and data residing in architectural registers (such as EAX).

- 5. The queued uops are dynamically executed according to their true data dependencies and execution unit availability (integer, FP, address generation, etc.). The order in which uops execute in time has no particular relationship to the order implied by the source program.

- Memory operations are dispatched from the RS to the Address Generation Unit (AGU) and to the Memory Ordering Buffer (MOB). The MOB ensures that the proper memory access ordering rules are observed.

- 7. Once a uop has executed, and its destination data has been produced, that result data is forwarded to subsequent uops that need it, and the uop becomes a candidate for "retirement".

- 8. Retirement hardware in the ROB uses uop timestamps to reimpose the original program order on the uops as their results are committed to permanent architectural machine state in the Retirement Register File (RRF). This retirement process must observe not only the original program order, it must correctly handle interrupts and faults, and flush all or part of its state on detection of a mispredicted branch. When a uop is retired, the ROB writes that uop's result into the appropriate RRF entry and notifies the RAT of that retirement so that subsequent register renaming can be activated. Up to 3 uops can be retired per clock cycle.

The Pentium Pro processor implements a 14-stage pipeline capable of decoding 3 instructions per clock cycle. The in-order front end has 8 stages. The out-of-order core has 3 stages, and the in-order retirement logic has 3 stages. For an integer op, say a register-to-register add, the execute phase is just one cycle. Floating point adds have a latency of 3 cycles, and a throughput of 1 per cycle. FP multiply has a latency of 5 cycles and a repetition rate of 1 every 2 cycles. Integer multiply has a latency of 4 cycles and a throughput of 1 every cycle. Loads have a latency of 3 cycles on a Dcache hit. FDIV is not pipelined; it takes 17 cycles for single, 32 cycles for

double, and 37 cycles for extended precision. The processor includes separate data and instruction L1 caches (each of which is 8KB). The instruction cache is 4-way set associative, and the data cache is dual ported, non-blocking, 2-way set associative supporting one load and one store operation per cycle. Both instruction and data cache line sizes are 32 byte wide. More details of the microarchitecture can be found elsewhere [2].

Figure 1 Pentium® Pro Processor Block Diagram

The secondary cache (L2 cache), which can be either 256KB or 512KB in size, is located on a separate die (but within the same package). The L2 cache is 4-way set associative unified non-blocking cache for storage of both instructions and data. It is closely coupled with a dedicated 64-bit full clock-speed backside cache bus. The L2 cache line is also 32 bytes wide. The L2 cache fills the L1 cache in a full frequency 4-1-1-1 cycle transfer burst transaction. The processor connects to I/O and memory via a separate 64-bit bus that operates at either 60 or 66 MHz. The bus implements a pipelined demultiplexed design with up to 8 outstanding bus transactions.

#### 3. Performance Monitoring Facility

The Pentium® Pro processor implements two performance counters[3]. Each performance counter has an associated event select register that controls what is counted. The counters are accessed via the RDMSR and WRMSR instructions. Table 1 shows a partial list of performance metrics that can be measured by selecting the two events to be monitored.

Table 1. Pentium® Pro Processor Counter based Performance Metrics

| Performance Metric                  | Numerator Event      | Denominator Event |  |

|-------------------------------------|----------------------|-------------------|--|

|                                     |                      |                   |  |

| Data references per instruction     | DATA_MEM_REFS        | INST_RETIRED      |  |

| L1 Deache misses per instruction    | DCU_LINES_IN         | INST_RETIRED      |  |

| L1 Icache misses per instruction    | L2_IFETCH            | INST_RETIRED      |  |

| ITLB misses per instruction         | ITLB_MISS            | INST_RETIRED      |  |

| Istalls cycles per instruction      | IFU_MEM_STALL        | INST_RETIRED      |  |

| L1 cache misses per instruction     | L2_RQSTS             | INST_RETIRED      |  |

| L2 cache misses per instruction     | L2_LINES_IN          | INST_RETIRED      |  |

| L2 Miss ratio                       | L2_LINES_IN          | L2_RQSTS          |  |

| Memory transactions per instruction | BUS_TRAN_MEM         | INST_RETIRED      |  |

| FLOPS per instruction               | FLOPS                | INST_RETIRED      |  |

| UOPS per instruction                | UOPS_RETIRED         | INST_RETIRED      |  |

| Speculative execution factor        | INST_DECODED         | INST_RETIRED      |  |

| Branch frequency                    | BR_INST_RETIRED      | INST_RETIRED      |  |

| Branch mispredict ratio             | BR_MISS_PRED_RETIRED | BR_INST_RETIRED   |  |

| Branch taken ratio                  | BR_TAKEN_RETIRED     | BR_INST_RETIRED   |  |

| BTB miss ratio                      | BTB_MISSES           | BR_INST_DECODED   |  |

| Branch Speculation factor           | BR_INST_DECODED      | BR_INST_RETIRED   |  |

| Resource stalls per instruction     | RESOURCE_STALLS      | INST_RETIRED      |  |

| Cycles per instruction              | CPU_CLK_UNHALTED     | INST_RETIRED      |  |

Table 2. Basic Characteristics of Systems

| Processor              | Intel Pentium <sup>®</sup> Pro Processor | Intel Pentium <sup>®</sup> Processor |

|------------------------|------------------------------------------|--------------------------------------|

| CPU Core Frequency     | 150 MHz                                  | 120 MHz                              |

| Bus Frequency          | 60 MHz                                   | 60 MHz                               |

| Data bus               | 64-bit                                   | 64-bit                               |

| Address bus            | 36-bit                                   | 32-bit                               |

| On-chip L1 cache       | 8 KB data, 8 KB instruction              | 8 KB data, 8 KB instruction          |

| Off-chip L2 cache      | 4-way 256 KB                             | 512 KB (Dell), 256 KB (Gateway)      |

| L2 cache timing        | 4-1-1-1 @ 150 MHz CPU freq.              | 3-1-1-1 @ 60 MHz bus frequency       |

| System Chip Set        | 82450GX/KX                               | 82430FX                              |

| Memory timing          | 14-1-1-1 (4-way interleaving)            | 13-3-3-3 (Fast Page Mode DRAM)       |

| (bus cycles)           | 14-2-2-2 (2-way interleaving)            | 13-2-2-2 (EDO DRAM)                  |

| (                      | 14-4-4 (no interleaving)                 |                                      |

| Basic Pipeline         | 14 stages                                | 5 stages                             |

| Superscalar            | 3-way                                    | 2-way                                |

| <b>Execution units</b> | 5                                        | 3                                    |

| Branch prediction      | 4-way 512 entry BTB,                     | 4-way 256 entry BTB,                 |

|                        | 4-bit history, 2 level adaptive          | 2-bit history                        |

| Execution model        | Out of order                             | In order                             |

| Speculative Execution  | Yes                                      | No                                   |

| McCalpin Streams       | 140 MB/sec (4-way interleaving)          | 82 MB/sec (Gateway 2000 P120)        |

| Memory Bandwidth       | 128 MB/sec (2-way interleaving)          |                                      |

|                        | 97 MB/sec (no interleaving)              |                                      |

| SYSmark/NT rating      | 497 (Digital Celebris* XL6150)           | 294 (Gateway 2000 P120)              |

| SPECint95              | 6.08 (Intel Alder System)                | 3.53 (Dell Dimension XPS P120)       |

| SPECfp95               | 5.42 (Intel Alder System)                | 2.92 (Dell Dimension XPS P120)       |

# 4. Comparing the Pentium<sup>®</sup> and Pentium<sup>®</sup> Pro Processors

This section compares the basic performance characteristics of the Pentium [4] and Pentium Pro processors. Table 2 compares the basic characteristics of these two processors. We chose the 120 MHz Pentium and the 150 MHz Pentium Pro processors because both are fabricated in the same 0.6µ technology and use a 60 MHz external bus. For the SPEC benchmarks, the Pentium system was a Dell Dimension XPS P120 with a 512KB pipelined burst L2 cache, and the Pentium Pro system was an Intel Alder system with a 150MHz Pentium Pro CPU with 256KB L2 cache and a 4-way interleaved memory.

Figure 2 Performance Comparison of Pentium<sup>®</sup> and Pentium<sup>®</sup> Pro Processors on SPEC95

Figure 2 shows the SPECratios and the cycles per instruction of the Pentium Pro processor relative to the Pentium processor for the SPEC95 benchmark suite for the two systems. The SPEC results were obtained using Intel Reference Compiler 2.3 Beta on UnixWare v2.0 on an Intel Alder system. The Pentium Pro processor achieves CPIs 15% to 50% lower than the Pentium processor, in spite of the fact that it uses a design style that emphasizes a fast clock frequency. Designs that emphasize clock frequency generally result in deeper pipelines and longer CPI. The Pentium Pro processor design attempts to increase frequency while reducing CPI, without being overly focused on optimal CPI or fastest clock [5].

The Pentium Pro processor runs at 1.6 to 2.4 times the performance of the Pentium processor on the SPEC95 suite[6], achieving 70% higher SPECint95 and 85% higher SPECfp95. This performance comes from a 25% faster clock frequency and a 15 to 50% reduction in CPI compared to the Pentium processor. The Pentium Pro processor can issue up to 3 instructions every clock cycle, while the Pentium processor can issue only two. The out of order execution model of the Pentium Pro processor also allows useful work to proceed while prior operations are stalled, thereby lowering the CPI.

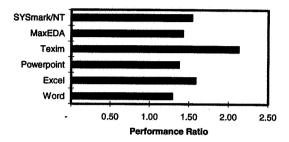

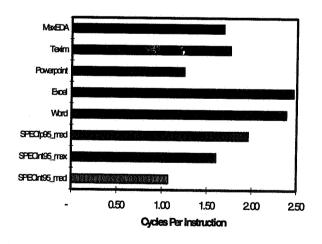

Figure 3 Performance Comparison of Pentium<sup>®</sup> and Pentium<sup>®</sup> Pro Processors on SYSmark/NT

Figure 3 shows the performance of a 150 MHz Pentium Pro processor based Digital Celebris 6150 compared to a 120 MHz Pentium processor based Gateway 2000 P120 system on the SYSmark for Windows NT suite from BAPCO[7], which contains project management software (Welcom Software Technology Texim Project 2.0e), computer-aided PCB design tool (Orcad MaxEDA 6.0) and Microsoft Office applications for word processing (Word 6.0), presentation graphics (PowerPoint 4.0), and spreadsheets (Excel 5.0). Both system had a 256KB L2 cache, but the Pentium Pro processor had a faster L2 cache (4-1-1-1 timing at full CPU clock frequency) on its dedicated L2 cache bus. The Pentium Pro processor runs 29% to 113% faster than the Pentium processor, with an overall 54% higher SYSmark score.

These results are slightly lower than the SPEC95 results because the desktop applications in the SYSmark benchmark perform some I/O operations that include wait times that do not scale with CPU performance. The SPEC benchmarks used compilers that generate binaries that are optimized for each target machine. The SYSmark/NT benchmarks use old binaries that are not optimized for the Pentium Pro processor. These benchmarks have large working set sizes for code and data and also contain many context switches. The SYSmark/NT benchmarks also result in higher L2 cache misses as shown in a later section.

#### 5. Detailed Characterization of SPEC CPU95 Benchmarks

This section presents a detailed characterization of Pentium® Pro processor running the SPEC CPU95 suite. The performance counter measurements presented in the rest of this paper were done on a Digital Celebris XL6200 running Microsoft Windows® NT Workstation Version 3.51. The central processor in the Digital Celebris XL6200 is a 200MHz Pentium Pro processor with 256KB L2 cache. The Celebris XL6200 system that we used in our test was configured with 128MB DRAM with 2-way interleaving and 14-2-2-2 memory timing at 66 MHz bus frequency. The SPEC benchmarks were compiled with Intel FORTRAN and C Reference Compilers Version 2.3.

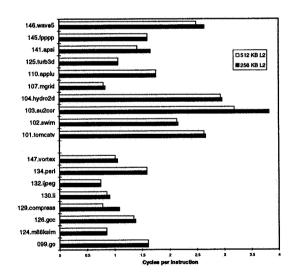

#### 5.1 Cycles per Instruction

Figure 4 shows the cycles per instruction (CPI) for the SPEC95 benchmark suite. Several integer benchmarks achieve less than one cycle per instruction. The CPIs are remarkably low for a processor that implements a 14-stage pipeline. The 'ow CPI is due to the overlapped out-of-order execution that mitigates the effect of the latency of individual operations, fast L2 cache, and adaptive two level branch prediction scheme. The FP benchmarks have higher CPI due to longer execution latencies and higher L2 cache misses.

Figure 4 Cycles per Instruction

We measured the CPI for the processor with 512 KB L2 cache too, by replacing the CPU in the Digital Celebris system. Only compress (28%), li (5%) su2cor (17%), apsi (15%), and wave5 (6%) showed more than 5% improvement in CPI with the larger cache. The L2 miss ratio reduction was 85%, 89%, 40%, 48%, and 19%

respectively. Simulations show that the CPI would decrease further for su2cor (25%), apsi (14%), and wave5 (5%) if the 4-way L2 cache is doubled again to 1 MB.

#### 5.2 Instruction Decode

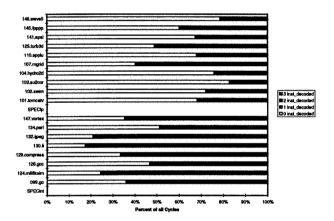

The Pentium Pro processor has 3 decoders that can handle up to 3 instructions every cycle (one instruction with up to 4 uops, and two single uop instructions)[5]. The decoder has a 6 uop queue at its output. Only 3 uops can be renamed per cycle, so the decoder has to stall if the queue is too full. Figure 5 shows the percentage of cycles in which 0, 1, 2, or 3 instructions were decoded. Benchmarks with high Icache or L2 misses show many cycles (35% to 51% for integer, 67% to 83% for FP) in which no instructions are decoded. During L2 misses, the CPU can run out of other machine resources causing back pressure on earlier pipe stages. On the integer benchmarks 33% to 54% of the instructions are decoded in cycles in which 3 instructions are decoded; 25% to 64% for FP benchmarks.

**Figure 5 Instruction Decode Profile**

#### 5.3 Cache Misses

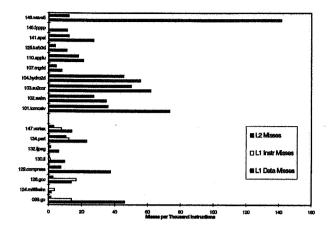

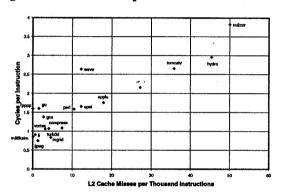

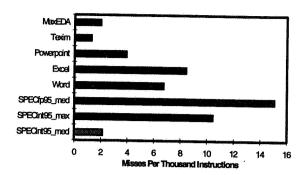

The L1 data cache can accept a new load or store every cycle and has a latency of three cycles for loads. It can handle as many as four simultaneously outstanding misses. Figure 6 shows the L1 data and instruction cache misses, and L2 cache misses. Except for gcc and m88ksim, the L1 data misses are always higher than the L1 instruction misses. In most cases the L1 instruction misses are so small that they don't even show on the scale used in Figure 6. The integer benchmarks, in general, show much lower L1 data cache and L2 misses than the floating point ones (larger data sets); but higher L1 instruction cache misses (larger code size and fewer loops). The benchmark (wave5) with the highest L1 misses does not have the highest L2 misses. Figure 7 shows a fairly strong

correlation between L2 misses and CPI, indicating that the L2 miss latency (about 50 CPU cycles) is not completely overlapped.

Figure 6 Cache Misses per Thousand Instructions

Figure 7 CPI versus L2 Cache Misses

#### 5.4 TLB Misses

Figure 8 ITLB Statistics

The Pentium® Pro processor has separate TLBs for instructions and data. The processor also has separate TLBs for 4-Kbyte and 4-Mbyte page sizes. The ITLB for 4KB pages has 32 entries. The DTLB for 4KB pages has 64 entries. Both are 4 way set associative. The ITLB for large pages has 4 entries, while the DTLB has 8 entries; both are 4-way set associative. As shown in Figure 8, the ITLB misses are well below 0.1 per thousand instructions, except for a couple of integer benchmarks. The DTLB misses are generally higher than ITLB misses, but they could not be measured accurately. TLB misses do not contribute much to the CPI, as shown later.

#### 5.5 Memory References

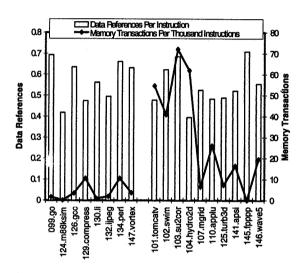

Figure 9 Memory Reference Statistics

Figure 9 shows the number of data references per instruction and the number of memory transactions per thousand instructions. On the average, both the integer and FP benchmarks generate about 1 data reference every two instructions. The IA-32 architecture results in more data references than most RISC architectures because it has fewer registers (8 vs. 32). As might be expected, there is a strong correlation between L2 cache misses and memory transactions. The memory transactions per instruction are higher for the FP benchmarks due to a higher L2 cache miss rate. Note that there can be more than one memory transaction per L2 cache miss if a dirty cache block has to be written back to memory.

#### 5.6 Branch Prediction

The Pentium® Pro processor implements a novel branch prediction scheme, derived from the two-level adaptive scheme of Yeh and Patt[8]. The branch target buffer (BTB) retains both branch history information and the

predicted branch target address. The BTB contains 512 entries. If a branch is not found in the BTB, a static prediction (backwards taken, forward not taken) is used. There is no penalty for correctly predicted not-taken branches. Correctly predicted taken branches incur a 1 cycle penalty. Mispredicted branches incur a penalty of about 10-15 cycles, plus additional cycles required to retire the mispredicted branch.

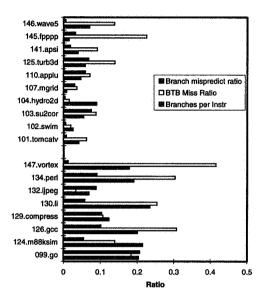

#### Figure 10 Branch Statistics

Figure 10 shows the frequency of branches, fraction of branches that hit in the BTB, and the accuracy of branch prediction. Even though the BTB miss ratio is fairly high, the branch mispredict ratio is less than 10% for all but one benchmark. The BTB miss ratio is high partly due to the fact that unconditional branches are not stored in the BTB, but are included in the total branch instruction count. As might be expected, the integer benchmarks contain more branches than the FP benchmarks, and they incur a higher branch mispredict ratio (fewer loop branches). The number of mispredicted branches range from about 2 to 40 per thousand instructions for the integer benchmarks, and about 0.1 to 4 for the FP benchmarks. For most of the benchmarks, branch mispredict stalls are not a major contributor to overall CPI.

#### 5.7 Speculative Execution

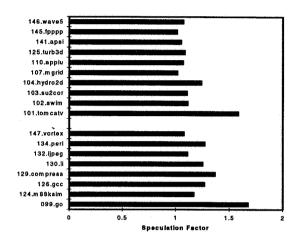

The Pentium® Pro processor fetches instructions along the predicted path and executes them until the branch is resolved. If a branch is incorrectly predicted, the speculated instructions down the mispredicted path are flushed. Note that there can be other mispredicted branches down a mispredicted branch. Figure 11 shows the average number of instructions issued per retired instruction for the SPEC benchmarks. There are about 13

to 37 speculated instructions per mispredicted branch. Mispredicted branches are not recognized for about 10 to 15 cycles, and the processor can issue up to 3 instructions per cycle. Benchmarks with higher mispredicted branches per instruction have higher speculated instructions.

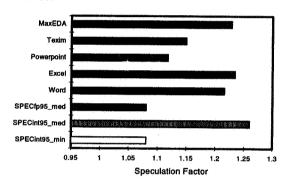

**Figure 11 Speculation Factor**

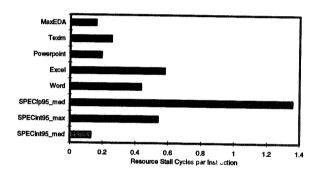

#### 5.8 Resource Stalls

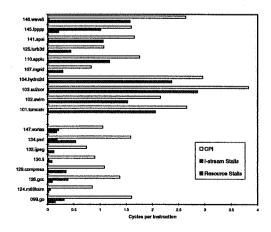

Figure 12 shows the I-stream stalls and resource stalls, measured in terms of the cycles in which the stall conditions occur. I-stream stalls are caused mainly by I-cache misses and ITLB misses. Resource stalls show the number of cycles in which resource, like register renaming or reorder buffer entries, memory buffer entries, and execution units are full; but these stalls may be overlapped with the execution latency of previously executing instructions. The FP benchmarks, except for fpppp (long basic blocks), incur negligible I-stream stalls. They do incur significantly more resource stalls than integer benchmarks, probably due to long dependency chains.

Figure 12 Stall Cycles

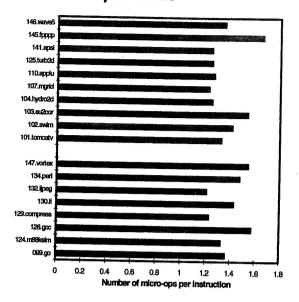

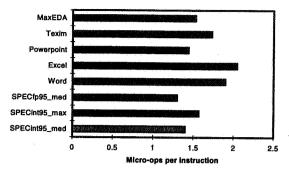

#### 5.9 Micro-Operations

Figure 13 Micro-operations per Instruction

The instruction fetch unit fetches 16 bytes every clock cycle from the I-cache and delivers them to the instruction decoder. Three parallel decoders decode this stream of bytes and convert them into triadic uops. Most instructions are converted directly into single uops, some are decoded into one-to-four uops, and the complex instructions require microcode (sequence of uops). Up to 5 uops can be issued every clock cycle to the various execution units, and up to 3 uops can be retired every cycle. Figure 13 shows the average number of uops executed per instruction for each of the SPEC95 benchmarks. The range is from 1.2 to 1.7, with an average around 1.35.

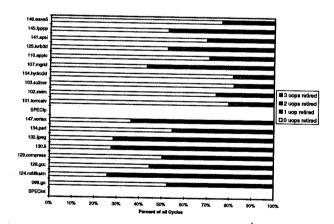

Figure 14 Micro-operations retirement profile

Figure 14 shows that no uops are retired in 25% to 55% of the cycles on the integer benchmarks, and 43% to 82% of the cycles for FP. Benchmarks with low CPI have fewer cycles with no uops retired. Furthermore, about 65% and

80% of the uops are retired in cycles in which 3 uops are retired for the average integer and FP benchmark respectively. This indicates that executed uops often have to wait for uops from previous instructions to be ready for retirement, thereby confirming the value of out of order execution. These younger uops build up more for FP benchmarks because of higher cache misses and longer latencies of FP operations.

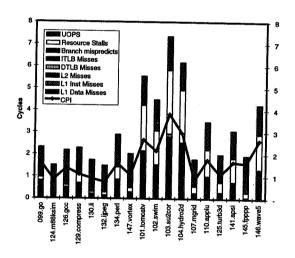

#### 5.10 Adding Up the Cycles

Accounting for cycles in an out-of-order machine like the Pentium® Pro processor is difficult due to all the overlapped execution. It is still useful to examine the various components of execution and stalls and compare them to the actual cycles per instruction as shown in Figure 15. The CPI is about 20 to 50% lower than the individual components due to overlapped execution. The figure also shows resource stall cycles in which some resource such as execution unit or buffer entry is not available. Execution can proceed during a resource stall cycle in some other part of the machine. Since more than one uop can be dispatched in a cycle, the figure does not account for execution parallelism, Micro-ops seem to dominate in most integer benchmarks. Resource stalls, and L2 misses contribute the most to the CPI in the FP benchmarks. Branch mispredicts are not a major factor.

Figure 15 CPI vs. Latency Components

# **6. Characteristics Across Different Workloads**

SPEC95 is a popular CPU intensive benchmark suite. It is widely used to characterize CPU performance. However,

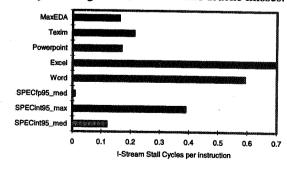

the behavior of other workloads can be quite different. This section presents the characteristics of desktop applications running on a Pentium® Pro processor. In particular, we present results for the SYSmark/NT benchmark. These benchmarks are not floating point intensive; Excel contains about 9% FP instructions, MaxEDA has 4%, and the rest less than 0.5%. While the SPEC95 benchmarks were optimized for the Pentium Pro processor using the latest compilers, the SYSmark/NT benchmarks are based on old binaries that have been shipping for many years and were probably not generated with all optimizations turned on.

In this section, we compare the SYSmark/NT benchmark statistics with the minimum, median, or maximum for the SPECint95 and SPECfp95 suites. The data presented here shows that the SPEC integer benchmarks should not be used to predict the performance of real business applications

Figure 16 shows the CPI across different workloads. The business applications (using old binaries with non-optimal code) incur higher CPIs than the median for the SPECint95 benchmarks. Two of the five SYSmark/NT benchmarks incur higher CPI than the median observed for the SPECfp95 suite. The CPI is higher due to higher L2 miss rates, Istream stalls, and resource stalls.

Figure 16 CPI for SYSmark/NT

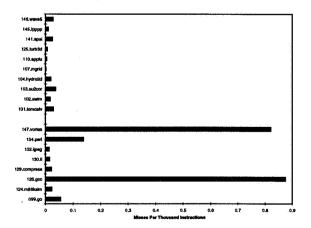

Figure 17 shows the L2 cache misses. The three Microsoft Office benchmarks incur much higher L2 misses than the SPECint95 median, but well below the SPECfp95 median. The code and data sizes of these business applications are much larger than the SPEC integer benchmarks. Once again, there is fairly strong correlation between L2 misses and CPI. Overall, Word and Excel exhibit the highest L2 misses and stall cycles among the SYSmark/NT benchmarks.

Figure 17 SYSmark/NT L2 Cache Misses

Figure 18 shows the resource stalls. The SYSmark/NT benchmarks incur higher resource stalls than the SPECint95 median, but are well below the SPECfp95 median. The higher resource stalls can be attributed to higher L2 misses during which the internal resources can be consumed by instructions waiting to be retired.

Figure 18 SYSmark/NT Resource Stalls

Figure 19 shows the instruction stalls. They are higher than the SPECint95 median. Once again, this is due to higher occurrence of string instructions in Word and Excel that invoke the microsequencer and require the decoders to stall. These workloads also have high context switch activity resulting in ITLB flushes and Icache misses.

Figure 19 SYSmark/NT Instruction Stalls

Figure 20 shows the uops per instruction. All the SYSmark/NT benchmarks execute more uops than most

of the SPEC95 benchmarks. This is probably due to the higher use of character string instructions. There is a strong correlation between uops/instruction and CPI, a trend not observed in the SPEC95 suite.

Figure 20 SYSmark/NT Micro-ops Per Instruction

Figure 21 shows the speculation factor. It is in the bottom half of the distribution for SPECint95. The speculation factor is lower because there are fewer mispredicted branches.

Figure 21 SYSmark/NT Speculation Factor

#### 7. Concluding Remarks

The Pentium® Pro processor was designed to achieve significantly higher performance than the Pentium processor in the same process technology. It achieves this performance through a superpipelined design that yields a 25% faster clock, and with an out of order dynamic execution engine that reduces the CPI. The data presented here shows that the Pentium Pro processor achieves a 15 to 45% reduction in CPI compared to the previous generation design (Pentium processor) in the same process technology, while running at a 25% faster clock frequency. The processor's out-of-order, speculative execution engine does manage to overlap useful work with pending memory accesses to reduce the impact of cache misses. The impact of resource stalls is also reduced by out of order execution. The branch prediction scheme

reduces branch mispredictions so as not to make them a significant performance limiter. It performs well even on old binaries that were not optimized for its microarchitecture. Performance counter based measurements show that the overall CPI achieved by the Pentium Pro processor is about 20 to 50% lower than the individual latency components due to overlapped execution.

A detailed comparison of the Pentium Pro processor and Digital's Alpha 21164 RISC processor is reported in another study [9].

#### 8. Acknowledgments

The authors would like to thank the Pentium® Pro processor designers for producing such an interesting microprocessor and for incorporating the performance counting mechanisms that enabled this study. Special thanks to Bob Colwell for his extensive review and valuable comments.

#### 9. References

- [1] Robert P. Colwell and Randy L. Steck, "A 0.6um BiCMOS Processor with Dynamic Execution", ISSCC Proceedings, February 1995, pp. 176-177.

- [2] Linley Gwennap, "Intel's P6 Uses Decoupled Superscalar Design", Microprocessor Report, Vol. 9, No. 2, 16 February 1995, pp. 9-15.

- [3] Intel Corporation, "Pentium Pro Family Developer's Manual, Volume 3: Operating System Writer's Manual", Intel Corporation, Order Number 242692, 1996.

- [4] Donald Alpert and Dror Avnon, "Architecture of the Pentium Microprocessor," IEEE Micro, June 1993, pp. 11-21.

- [5] David Papworth, "Tuning The Pentium Pro Microarchitecture," IEEE Micro, April 1996, pp. 8-15.

- [6] Jeff Reilly, "A Brief Introduction to the SPEC CPU95 Benchmark," IEEE-CS TCCA Newsletter, June 1996. Also, see http://www.specbench.org/osg/cpu95/.

- [7] http://www.bapco.com/nt1.htm

- [8] Tse-Yu Yeh and Yale Patt, "Two-Level Adaptive Training Branch Prediction," Proc. IEEE Micro-24, Nov 1991, pp. 51-61.

- [9] Dileep Bhandarkar, "RISC versus CISC: A Tale of Two Chips," submitted for publication.

<sup>&#</sup>x27;Intel® and Pentium® are registered trademarks of Intel Corporation. Other brands and names are the property of their respective owners.

Received: from nsf.ac.uk by dcs.ed.ac.uk id aa20677; 14 Apr 92 13:14 BST

Received: from hermes.intel.com by sun2.nsfnet-relay.ac.uk with SMTP inbound id <9319-0@sun2.nsfnet-relay.ac.uk>; Tue, 14 Apr 1992 13:11:56 +0100 Received: from ssduk.intel.com by hermes.intel.com (5.65/10.0i);

Tue, 14 Apr 92 05:06:24 -0700

Received: from imussd.intel.com by ssduk.intel.com (4.1/SMI-4.1) id AA01282; Tue, 14 Apr 92 13:07:45-010

Received: by imussd.intel.com (4.1/SMI-4.1) id AA01254;

Tue, 14 Apr 92 14:07:21 +0200

From: Thomas Bemmerl <thomas@com.intel.imussd> Message-Id: <9204141207.AA01254@imussd.intel.com>

Subject: European Supercomputer Development Center (ESDC)

To: stew@ca.utoronto.hub, dmirpt0@es.uib.ps, reijns@nl.tudelft.hdetudll Date: Tue, 14 Apr 92 14:07:21 MET DST

Cc: rni@uk.ac.ed.dcs, sanders@ch.ethz.inf, NPT@uk.ac.ed.ecsvax

X-Mailer: ELM [version 2.3 PL11] Sender: thomas@com.intel.imussd

Status: RO

Hi,

on March 31st 1992 I have left the Department of Computer Science of Munich University of Technology (TUM). After having finished "Habilitation" last December, I was searching for a new challenging career opportunity, which I received at Intel Corporation. Starting April 1st I took over at Intel Corporation the position to direct the newly founded European Supercomputer Development Center (ESDC). ESDC is a European research and development department of Intel's Supercomputer Systems Division, associated to Intel GmbH Germany located close to Munich in Feldkirchen. Enclosed you find for more detailed information parts of the press release for the announcement of ESDC at Supercomputing Europe '92. Therefore my new address is:

> Intel GmbH European Supercomputer Development Center (ESDC) Dornacher Str. 1, W-8016 Feldkirchen b. Muenchen, FRG Tel.: +49-89-90992-0, Fax.: +49-89-9039-142 e-mail: thomas@esdc.intel.com

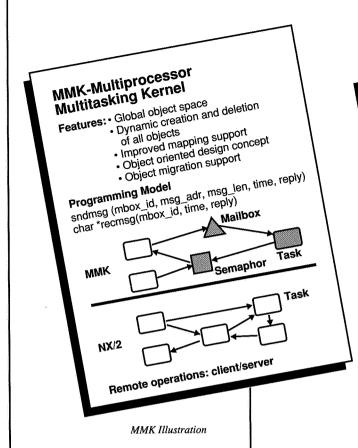

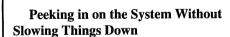

You see, I will continue to work in the research field known to me, concentrating initially on programming tools and distributed operating systems for parallel supercomputer technology. Intel ESDC will initially start with the following two charters:

- 1. Active participation in Intel's research and development programs (Touchstone, TriStar, Paragon, iWarp) to achieve affordable TeraFLOPS supercomputer technology by the middle of the decade. Within these R&D programs ESDC initially takes over work in the field of parallel programming tools (performance analysis) and distributed operating systems (dynamic loadbalancing). In the long term ESDC will also become active on research and development projects in the field of parallel applications for TeraFLOPS computers.

- 2. Enhancement of the Touchstone and TriStar programs by collaborative projects with European research and development groups from industry, government and academia. In cooperation with Intel users and other interested research groups, ESDC is going to be involved in European R&D projects (e.g. ESPRIT) and other European activities on High Performance Computing (HPC).

A challenging long term vision may be a partly combination of HPC activities in Europe and the US, due to the fact that problems addressed by HPC (the so called grand challenges, as global climate modeling and weather

forecasting, the human genome project, computational fluid simulation, QCD effects, etc.) are relevant for the US as well as for Europe. Global and international solutions are most appropriate to solve these grand challenges.

For this reason I am very interested to stay in touch with your organization and you personally. Do not hesitate to contact me under my new address, if you have any questions, in particular on opportunities for further scientific collaborations.

Looking forward to fruitful future cooperations, I remain,

with best regards,

Dr. habil. Thomas Bemmerl

Director, European Supercomputer

Development Center (ESDC)

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

#### News Release

Intel Establishes European Supercomputer Development Centre

Extends Lead in Race to Deliver World's First TeraFLOPS Supercomputer

PARIS, 13. February 1992 -- Intel Corporation, the worlds leading supplier of parallel supercomputers, today announced the establishment of a European Supercomputer Development Centre to be located in Munich, Germany.

Dr. Thomas Bemmerl of the Technical University Munich is moving to Intel to direct the operations of the Centre. Under Bemmerl's direction, Intel's European Supercomputer Development Centre (ESDC) will be collaborating with European Users and European research labs to develop software technologies in support of TeraFLOPS computing.

"The establishment of our European Supercomputer Development Centre is evidence of our commitment to be more actively involved in the High Performance Computing initiatives being discussed in the European Community, such as those being considered by ESPRIT programes, the Rubbia working group and the Euorpean Industry Initiative", said Joseph Mazzarella, international are director for Intel's Supercomputer Systems Division.

According to Justin Rattner, Intel Fellow and director of technology for Intel's Supercomputer Systems Division, ....

Intel's new European Supercomputer Development Centre will initially focus on software tools, environments and operating systems, and their impact on user applications for TeraFLOPS.

According to Steve Nachtsheim, vice president, Intel Products Group - Europe, "Intel's aggressive TeraFLOPS programme, the launch of our powerfull new Paragon XP/S supercomputer and our overall success in Europe has enabled Intel to dramatically extend our worldwide leadership position in supercomputing. Integrating technologies, sofware and applications from Intel, our European partners and customers, is another step in Intel's goal of ensuring the practical usability of TeraFLOPS computers".

. . . .

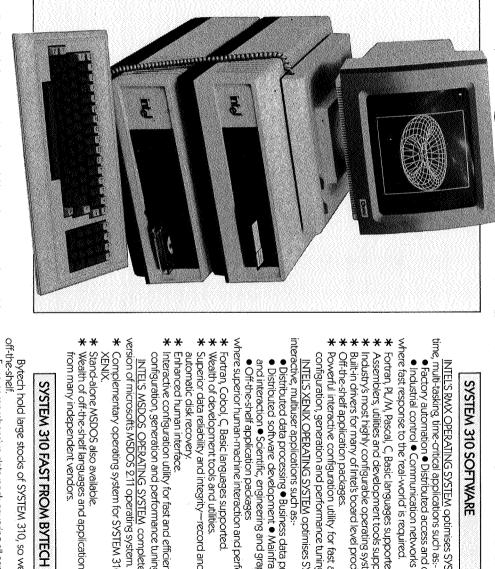

#### 80286 EDUCATIONAL FOCUS

To enable Bona-Fide Educational Establishments to take advantage of Intel's 80286 "Supermicro" technology, Bytech are offering a selected range of Intel's 80286 based products and development kits at a fraction of the normal price.

FOR A VERY LIMITED PERIOD BYTECH WILL GIVE AN EDUCATIONAL DISCOUNT OF UP TO 60% ON THESE "TECHNOLOGY-LEADING" PRODUCTS.

|                                               |                                                                                                    | List(£)                      | Educational(£)               |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------|------------------------------|

| SBC286/10<br>SBC012CX<br>SBC010CX<br>SBC020CX | - 80286 based CPU board<br>- 512KB LBX RAM board<br>- 1.0MB LBX RAM board<br>- 2.0MB LBX RAM board | 3057<br>2259<br>4769<br>8283 | 1832<br>1807<br>2861<br>6626 |

| SBC286/10 KIT                                 | - System SBC286/10 + SBC012B + System Debug Monitor                                                | 7530                         | 3012                         |

| SYS310-17MR KIT<br>+ SBC286/10 KIT            | - RMX 310 Starter Kit                                                                              | 25028                        | 14016                        |

| SYS310-17MX KIT<br>+ SBC286/10 KIT            | - XENIX 310 Starter Kit                                                                            | 24216                        | 13559                        |

| SYS310-4<br>+ SYS310-17MR KIT                 | - 310 Microsystem Hardware Unit                                                                    | 25932                        | 17635                        |

| SYS310-4<br>+ SYS310-17MX KIT                 | - 310 Microsystem Hardware Unit                                                                    | 25120                        | 17083                        |

| MDX431B<br>+ 111286<br>+ SBC286/10 KIT        | - 8 & 16 bit Development System<br>- In-Circuit Emulation for 80286                                | 44050                        | 34603                        |

DON'T DELAY - PHONE 0344-482211 TODAY FOR FURTHER INFORMATION ON THESE SUPER DEALS.

N.B. Offer expires 31st March 1985.

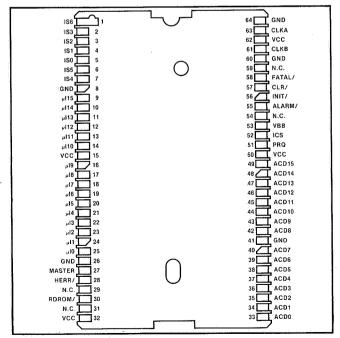

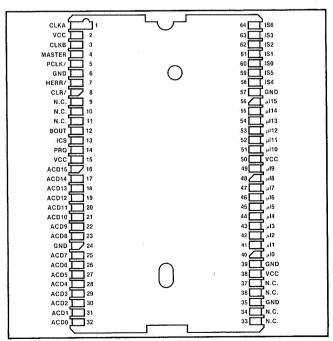

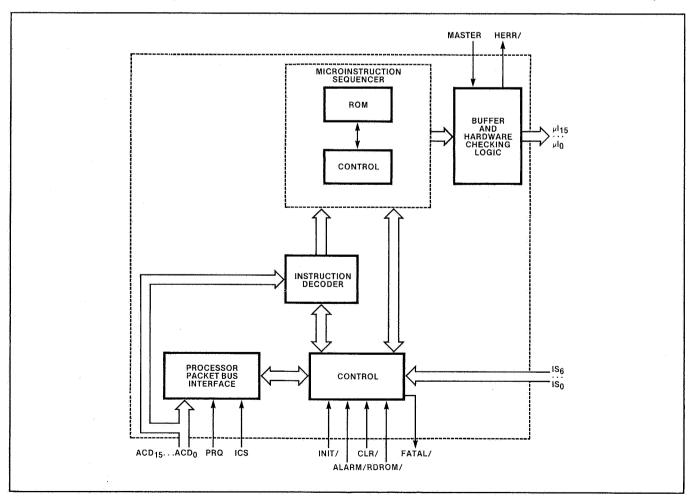

# DESIGN NEWS

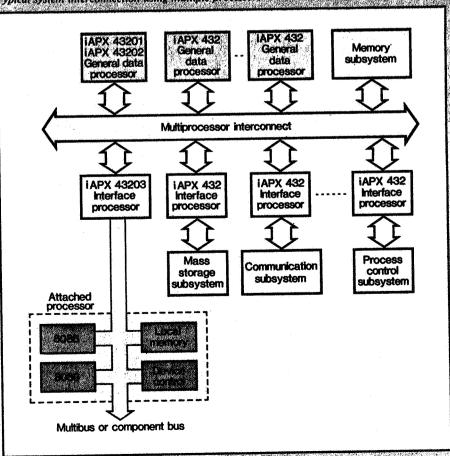

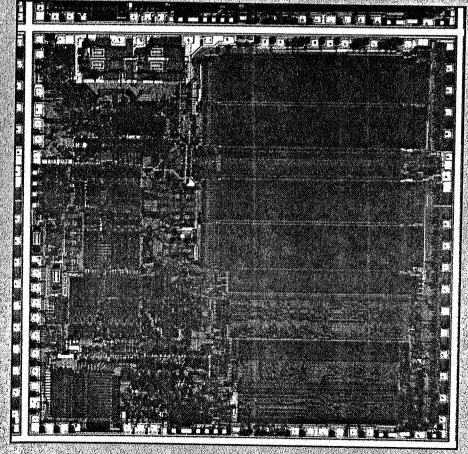

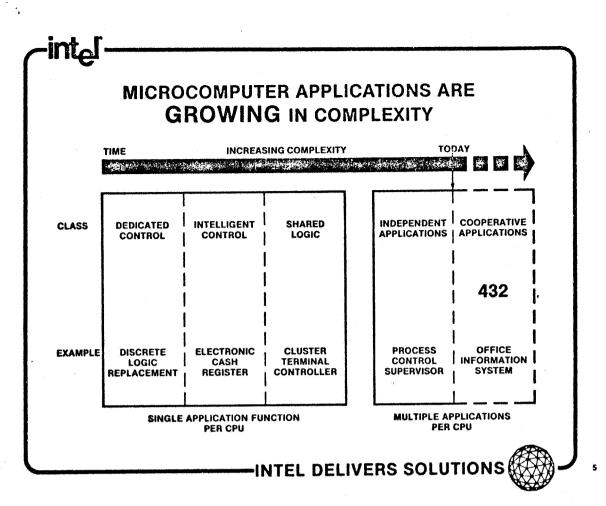

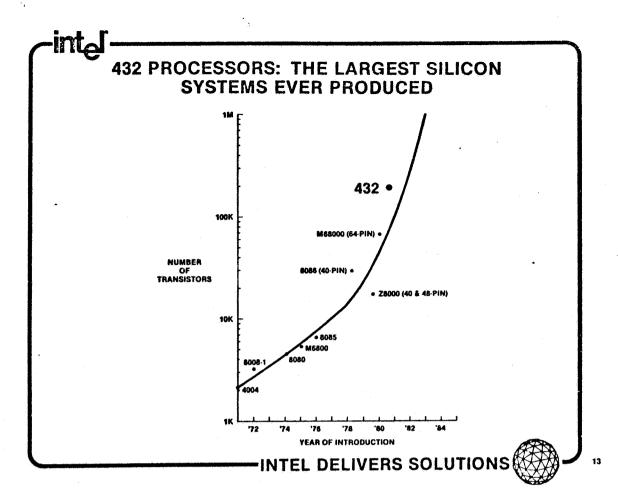

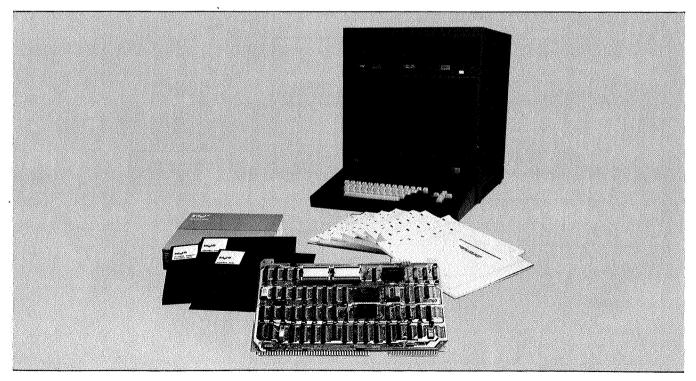

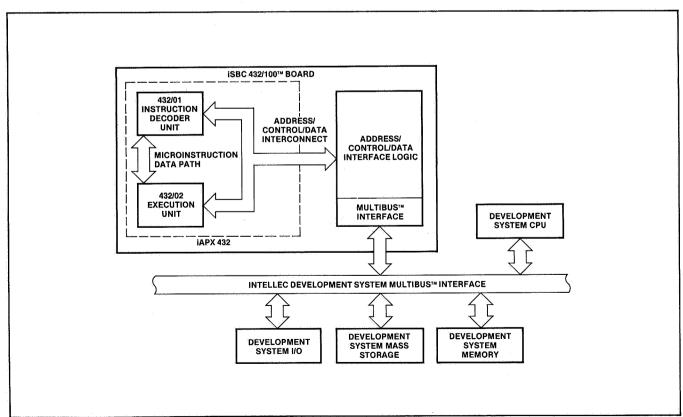

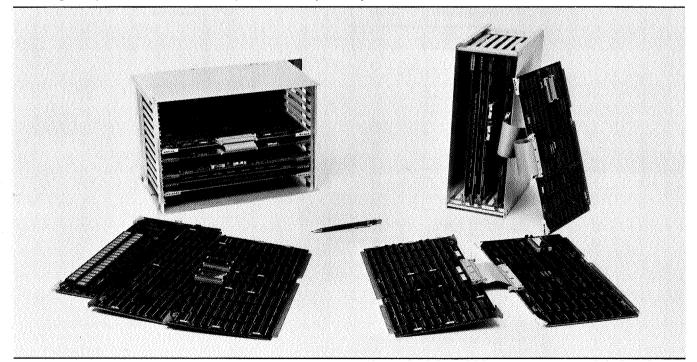

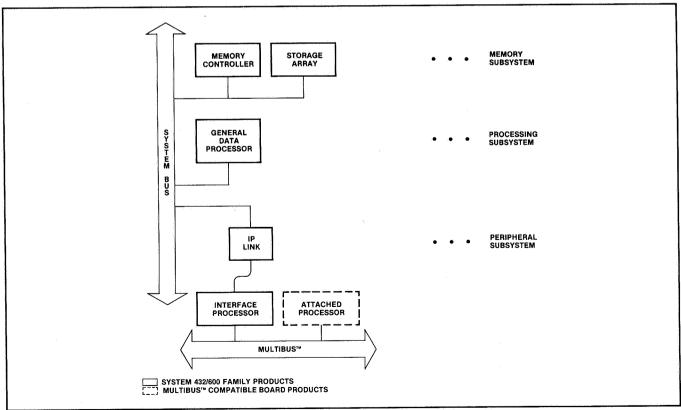

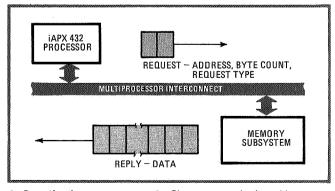

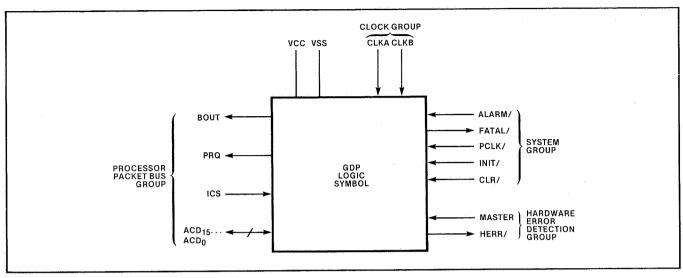

O ne of the highlights of the recent ISSCC event was the official unveiling by Intel of its 32-bit microprocessor. Called the iAPX 432, this is a set of three devices which together deliver the kind of computing resources associated with mid-range mainframes. In fact, Intel's designation of 'micromainframe' is a more accurate term than microprocessor—the iAPX 432 bears little relation to any of the microprocessors that have been available to date.

The system is based on a new architecture designed to significantly reduce the cost and time for developing large-scale applications by improving programmer productivity. In addition, the micromainframe includes hardware and software facilities for design of fault-tolerant systems.

The iAPX 432 has been designed to employ Intel's current line of peripheral controller chips, memories, and microprocessors. Thus, designers have a wide variety of field-proven devices available for use in micromainframe-based systems.

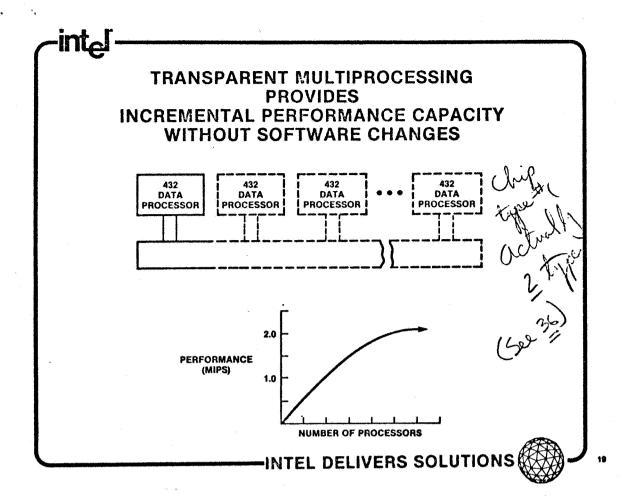

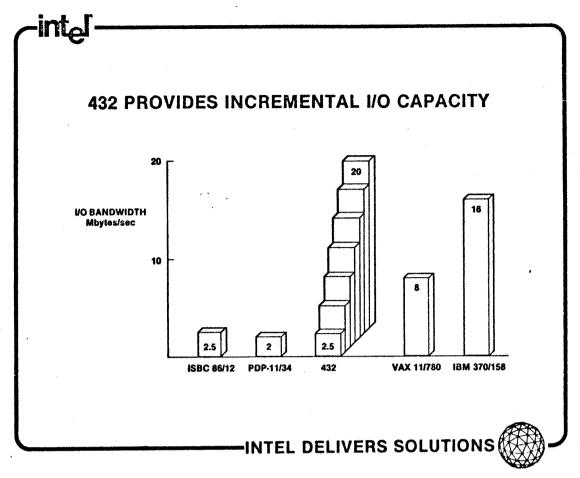

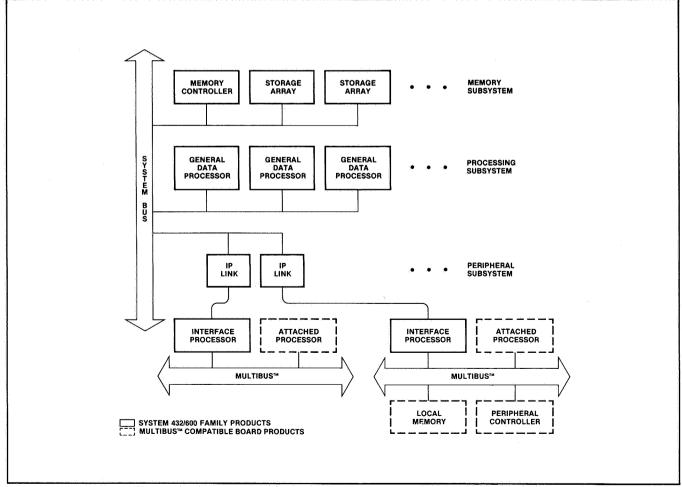

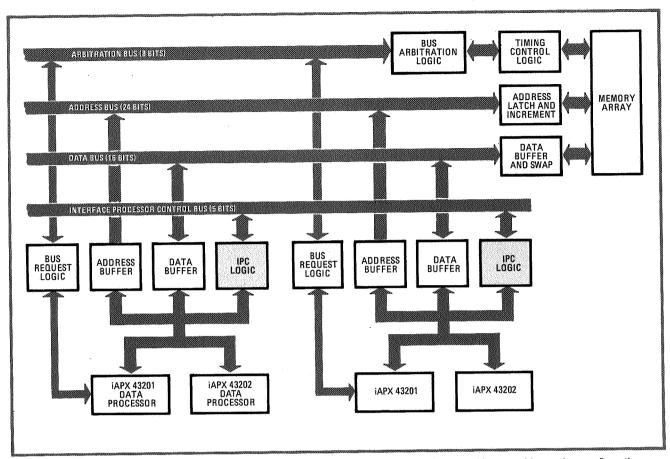

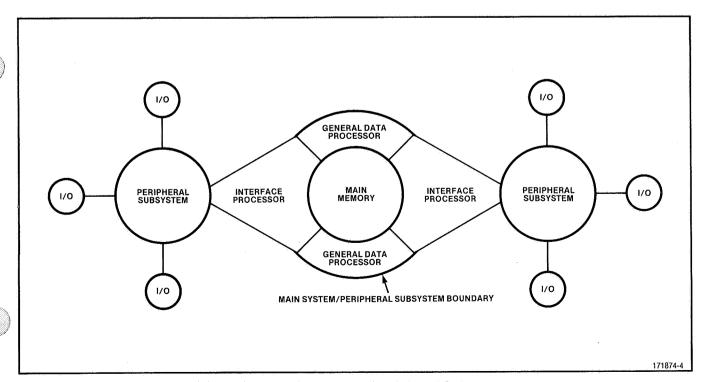

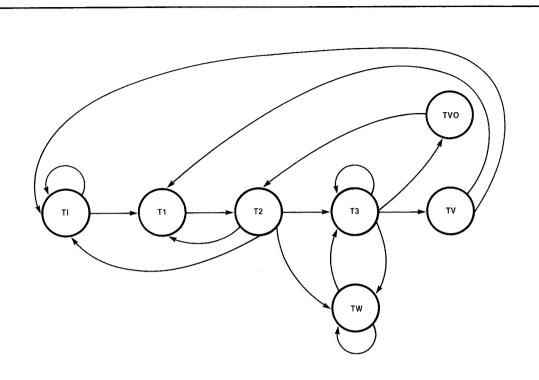

Like most mainframes, the 432 is split into functionally specialised data processors and I/O subsystems. Additionally, the designer can add extra data processors or I/O subsystems to improve performance in a softwaretransparent fashion. This means that a single set of hardware and software components can be applied to many different end-products, or to a single family of products offering multiple levels of performance. Moreover, the performance of a system can be upgraded, if necessary, to meet existing design requirements or to accommodate new application demands.

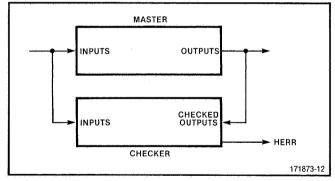

Because the number of data processors and I/O subsystems is under the control of the user, efficient multiprocessor arbitration and coordination facilities are essential. These do not need to be devised by the user, however; they have been built in to the hardware, thereby reducing configuration constraints. The kind of software-transparent multiprocessing that is possible with the 432 allows systems to be designed that have a 1-to-10 performance range.

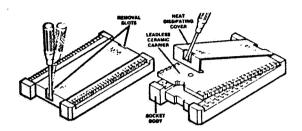

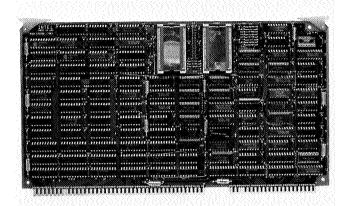

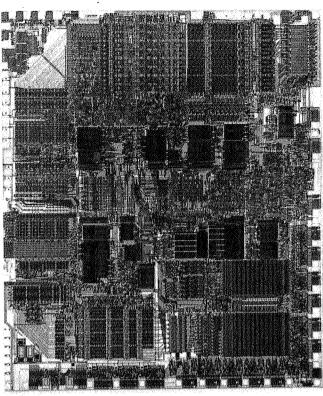

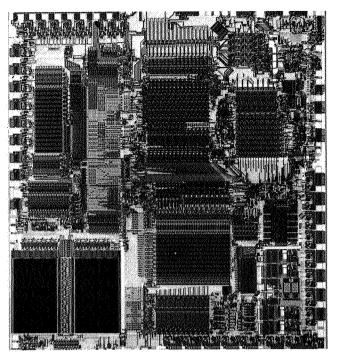

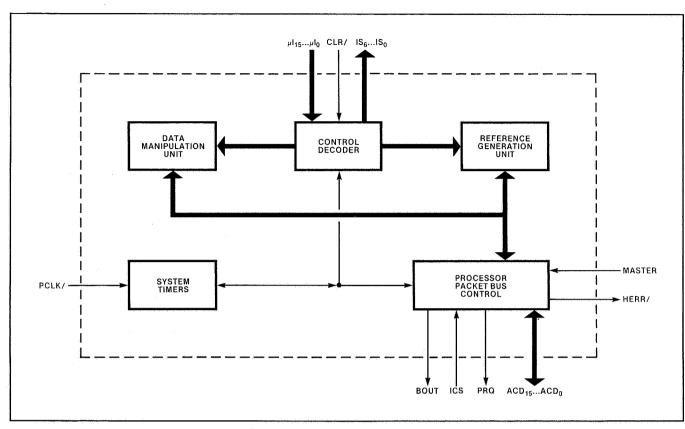

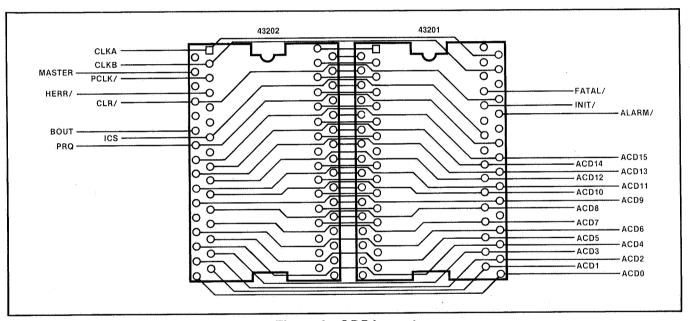

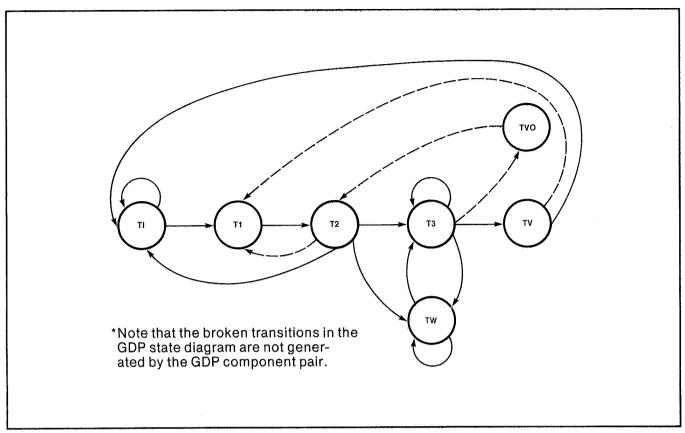

Two of the micromainframe's three chips make up its general data processor (GDP). They are the in-

# Intel's 32-bit microprocessor unveiled

struction decode unit (iAPX 43201) and microexecution unit (iAPX 43202). They act as a pipe-lined pair, one fetching and decoding instructions and the other executing them.

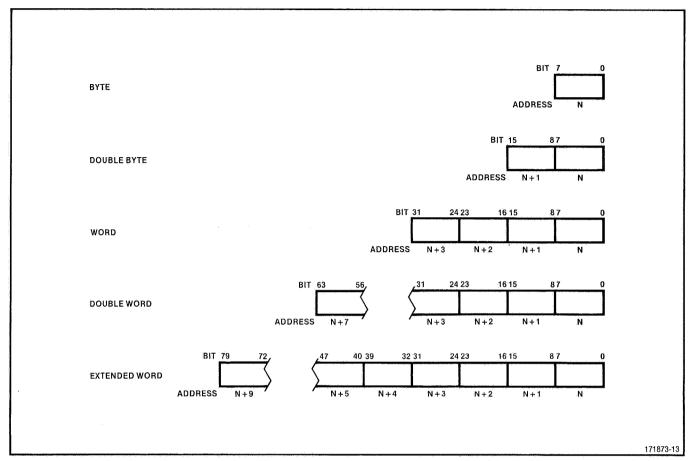

The 32-bit GDP supports a logical address space of 2" or more than 4 billion bytes. What's more, it governs a virtual memory address space of 2" or 1,000,000,000,000 bytes (a terabyte). This address region extends well beyond that of today's midrange mainframes. It effectively removes all address barriers, allowing large programs and data to be constructed.

Like contemporary mainframes, the micromainframe handles 32-bit data words. But it also operates on floating point values of 32-, 64-, even 80-bits wide. It multiplies 32-bit integers in 6-25 microseconds, and 80-bit floating point numbers in only 26-125 microseconds. This, says Intel, exceeds the performance of

several popular mainframe computers.

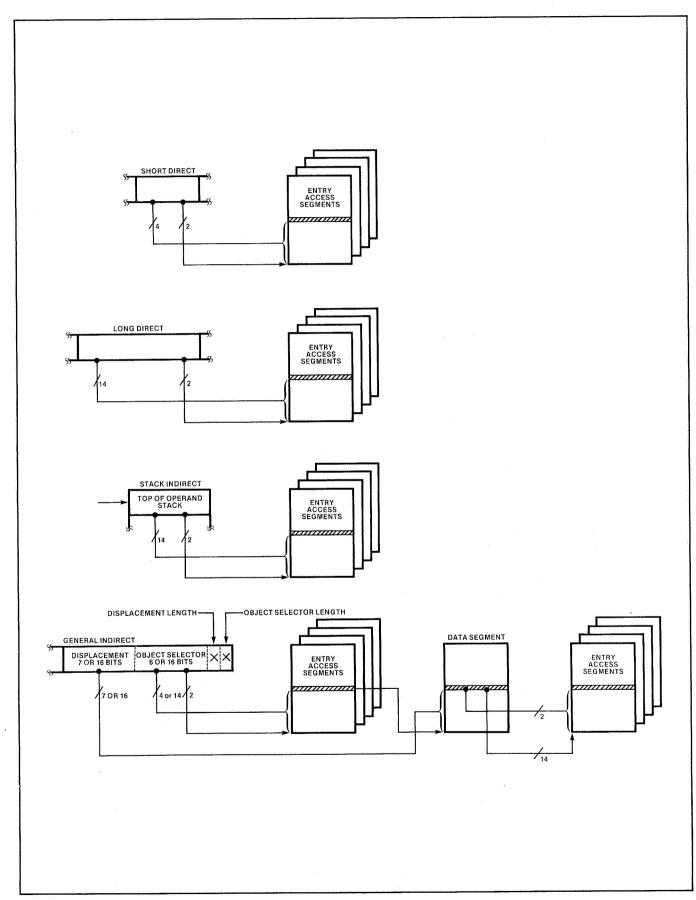

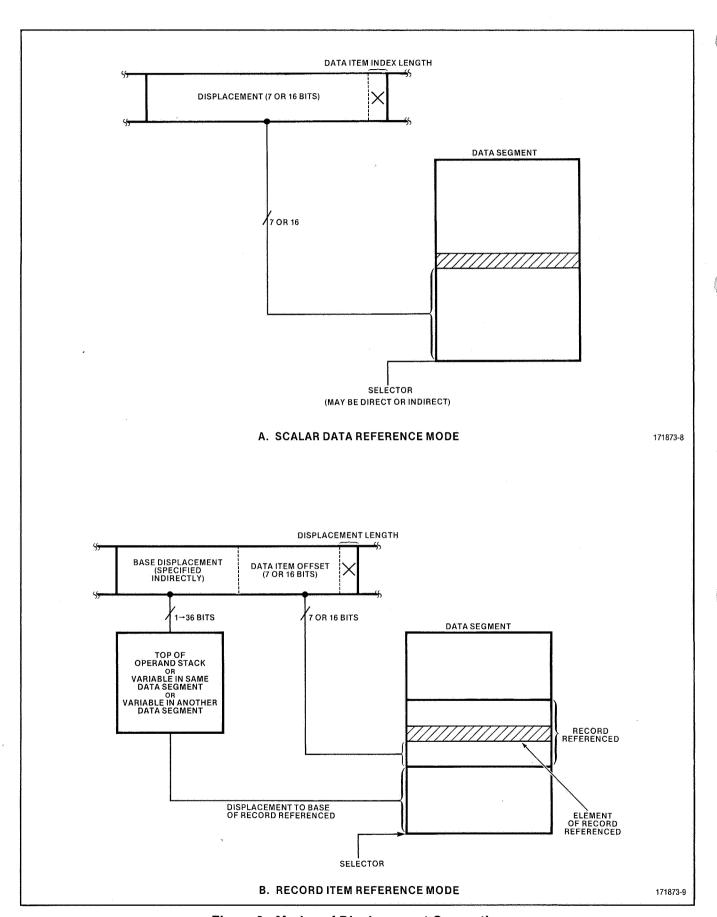

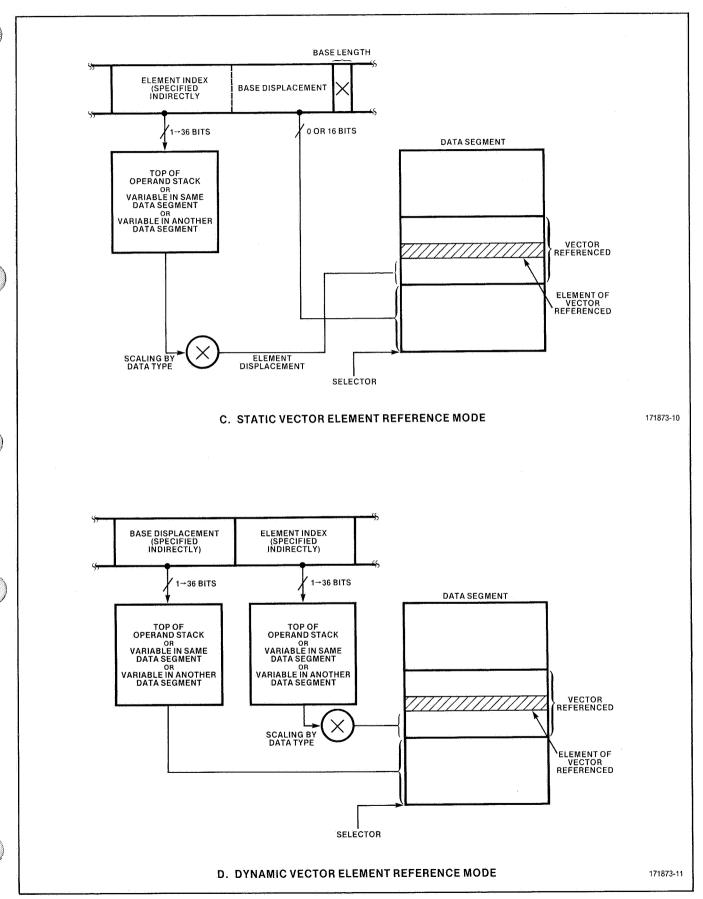

In addition to floating point data types, the micromainframe handles boolean and character data types. The iAPX 432 instruction set has been specifically designed for high-level languages. It supports from 0 to 3 operand specifiers per instruction, and features symmetric operand addressing modes for scalar, vector, and record elements. This makes high-level languages more efficient and obviates the need for assembly language programming.

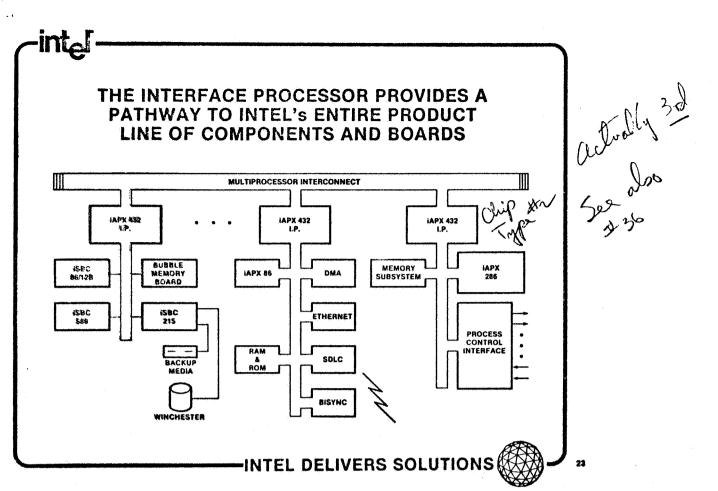

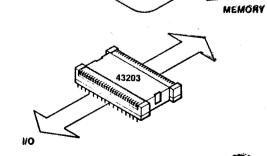

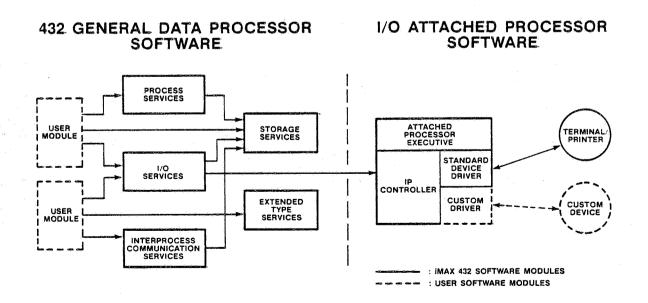

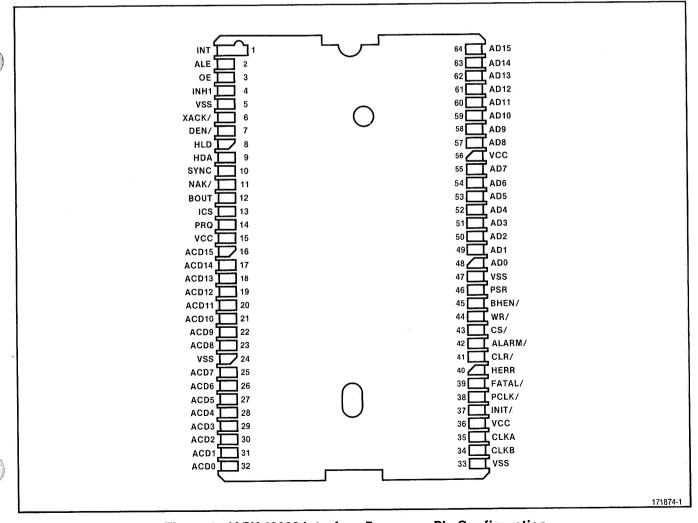

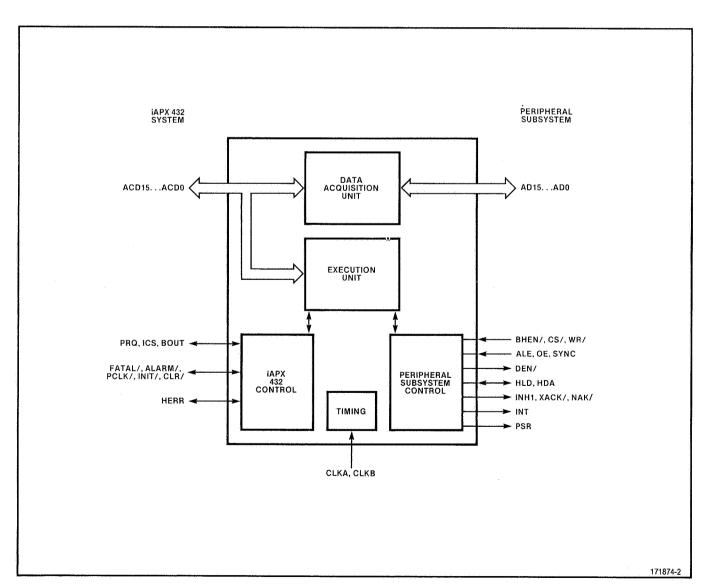

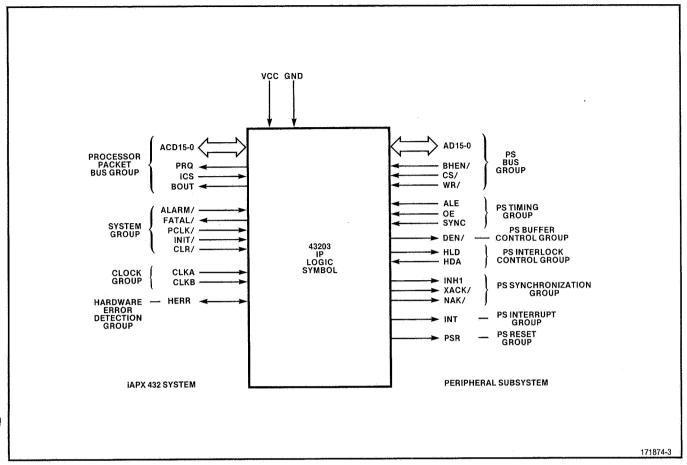

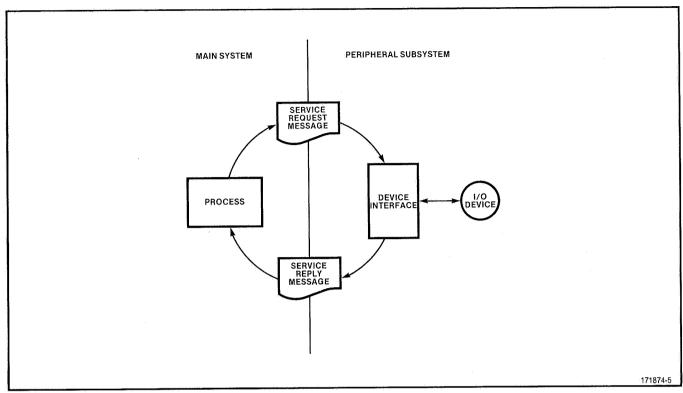

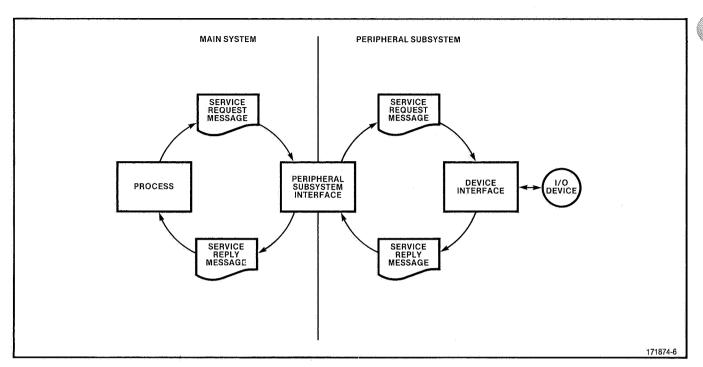

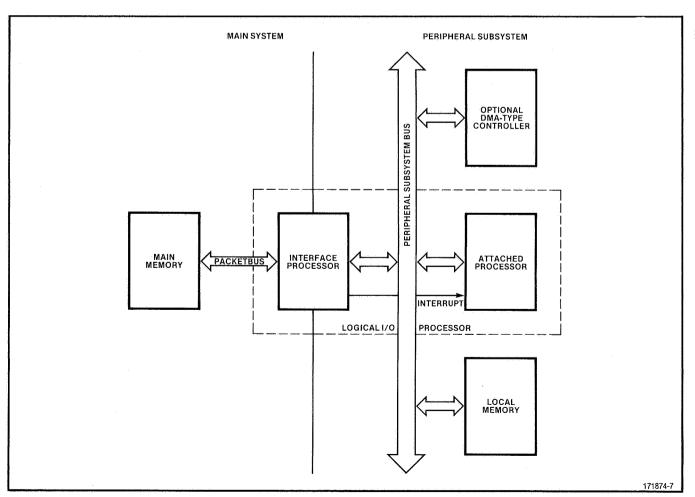

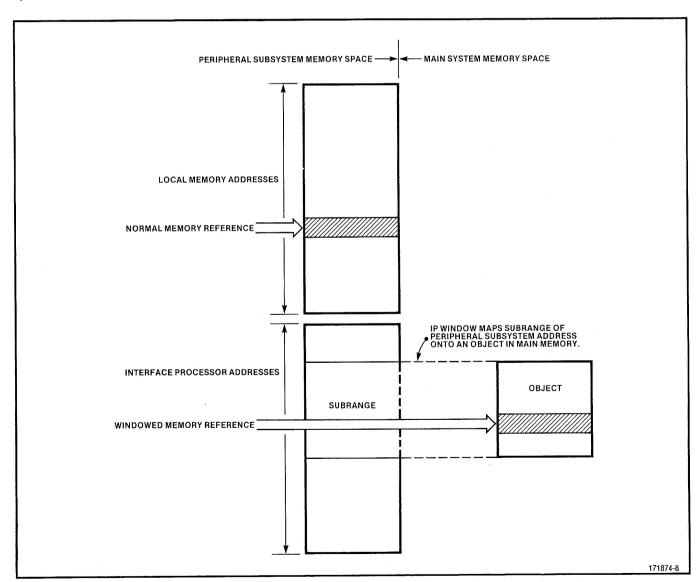

Communication with input and output devices (such as mass storage subsystems and high-speed printers) is handled by the third of the three-chip set—the interface processor (43203). It permits a satellite subsystem to act as an 'attached processor' which independently handles all I/O activity. The attached processor is an independent microcom-

Typical system interconnection using multiple processors

## **DESIGN NEWS**

puter subsystem configured from the existing line of Intel mid-range microprocessors, peripheral controllers, and Multibus-compatible devices. For example, a single attached processor can be built using the iAPX 86 (8086) as an I/O controller.

The 43203 is connected to the attached processor via a subsystem bus, and communicates with the general data processor (43201 and 43202) via a 'packet bus'. The packet bus is a time-multiplexed interface used for communications between the iAPX 432 processor and memory, and between processors. As many as ten bytes of data can be transferred during a single request or reply.

Micromainframe's attached processor scheme provides nearly unlimited system flexibility. Input/output processing is moved out of the computation system closer to the devices to be controlled, I/O and interrupt burdens are therefore removed from the central system.

A key feature of the 432 is the provision of high level instructions which replace the kind of subroutines normally found in an operating system. For example, there are 'send'

and 'receive' instructions which perform, via built in hardware, all the buffering and synchronisation required to transmit data structures between program.

In addition, the silicon operating system automatically distributes the workload among the GDPs. As more processors are added, the workload is automatically and dynamically shared among them. The operating system accounts for some 40% of the 64k bits of microcode—the next heaviest demand is made by the floating point algorithms which take up 18%. In contrast, the basic instruction set uses only 6% of the microcode.

Although the operating system is implemented in hardware, the major scheduling parameters are defined by software so that the improved execution efficiency and reduced software costs have not been attained by sacrificing flexibility.

One of the underlying assumptions behind the development of the 432 was Intel's conviction that current microcomputer programming practice would not be able to cope with the projected increase in microcomputer applications. Perhaps the single most important design goal was the need to increase programmer productivity and software reliability. Thus the 432 instruction set is optimised for the language ADA—most ADA instructions compile to a single 432 instruction—and built-in safeguards prevent incorrect software from corrupting good software:

ADA, a programming language developed with the co-operation of the United States Department of Defense, industry, and universities, is the micromainframe's system programming language. It is a language oriented toward systems program-ming, numerical problem solving, and real-time applications involving concurrent execution requirements. ADA combines PASCAL's simplicity and elegance with the structure and expressive capability necessary for multi-function software systems. It was selected as the 432's system programming language because it directly supports object-oriented programming methodology and is expected to further improve productivity for software development

The micromainframe's hardware, operating system, and system programming language all support the concept of 'objects'—a variable length data structure which is of a higher order than data typically recognised and manipulated by contemporary computer hardware.

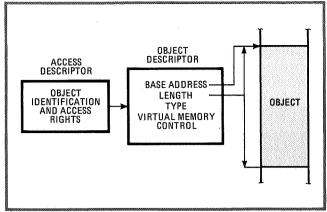

System programmers write program 'modules' which are based on objects. Each object is typed by a special 'object descriptor' and can only be physically addressed by a special 'access descriptor'. What may gain access to the object, and what operations may be done to it, are inherently controlled.

This facility ensures that every data structure in memory is uniquely protected in terms of which programs can access it, and to what extent it may be referenced by an authorised program. Programs only have access to the data that they 'need to know'.

Each data structure is also 'typed' to make sure that it is only used in conjunction with operations that make sense for it. For example, it is impossible to 'branch-to-data,' or 'over-write instructions'. These protection facilities guarantee that software errors are detected immediately and confined to offending programs.

The 43201 instruction decode unit, part of the general data processor

WI= Comm

# intel 432 Summary Presentation

1980 Intel Technical Symposium

### -int<sub>e</sub>l

### THE INTEL 432

### A 32-BIT MICROMAINFRAME:

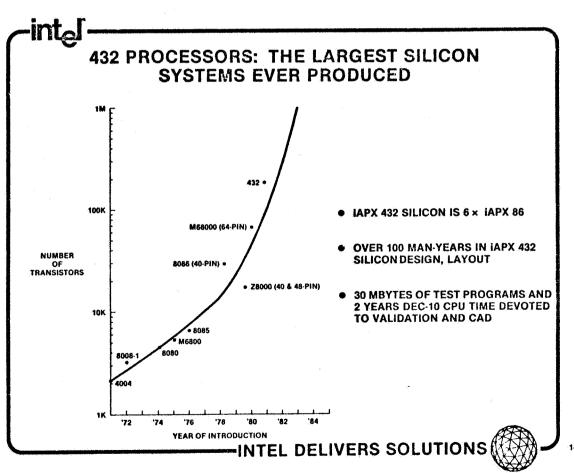

VLSI IMPLEMENTATION, OVER 200K DEVICES

240 BYTES VIRTUAL ADDRESS SPACE

224 BYTES PHYSICAL ADDRESS SPACE

8, 16, 32, 64, AND 80-BIT DATA TYPES

3 OPERAND ADDRESS MODES

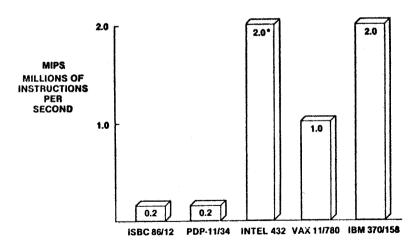

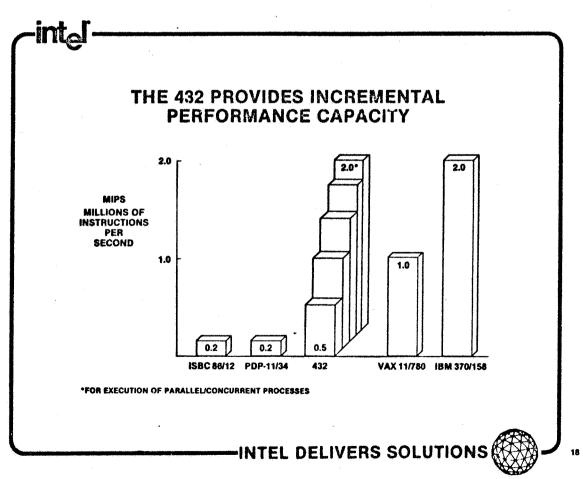

2 MIP PERFORMANCE RANGE

TRANSPARENT MULTIPROCESSING

OBJECT-ORIENTED ARCHITECTURE

ADDRESS CACHING

ORTHOGONAL INSTRUCTION SET

INDEPENDENT AND DECENTRALIZED I/O

SELF-DISPATCHING PROCESSORS

PROTECTION TO THE DATA STRUCTURE LEVEL

ADA ABSTRACTION, TYPING, AND CONCURRENCY

#### THE 432 MICROMAINFRAME...

... A TOTAL SYSTEM APPROACH

-INTEL DELIVERS SOLUTIONS

### -intel

**432 OBJECTIVE:**

TO SIGNIFICANTLY REDUCE THE

COST &

TIME TO MARKET

OF SOFTWARE INTENSIVE MICROCOMPUTER APPLICATIONS

-INTEL DELIVERS SOLUTIONS

### -int<sub>e</sub>l

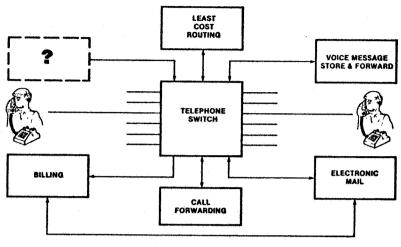

# ...TODAY, A TOTAL MANAGEMENT INFORMATION SYSTEM

- COOPERATING, MULTIPLE APPLICATIONS

- HIGH PERFORMANCE AND FUNCTION

- COMPUTER CRITICAL TO OPERATION OF BUSINESS

- CONTINUOUSLY GROWING

-INTEL DELIVERS SOLUTIONS

### -int<sub>e</sub>l

# OTHER INCREASINGLY COMPLEX MICROCOMPUTER APPLICATIONS:

- TRANSACTION PROCESSING

- ONLINE OFFICE INFORMATION

- COMPUTER AIDED DESIGN AND SIMULATION

- MULTIFUNCTION BUSINESS SYSTEMS

- FACTORY AUTOMATION AND CONTINUOUS PROCESS CONTROL

-INTEL DELIVERS SOLUTIONS

### -int<sub>e</sub>l

#### ATTRIBUTES OF COMPLEX APPLICATIONS

- MULTIFUNCTION

- **∠** CONCURRENT

- **► LARGE SCALE**

- GROWING AND EVOLVING

- **∠** SOFTWARE INTENSIVE

## COMPLEX APPLICATIONS ARE 432 APPLICATIONS

-INTEL DELIVERS SOLUTIONS

### -int<sub>e</sub>l

#### THE 432 MICROMAINFRAME:

- A DIRECT RESPONSE TO THE GROWTH IN APPLICATION COMPLEXITY

- A <u>UNIQUE COMBINATION</u> OF SYSTEM CAPABILITIES OPTIMIZED TO REDUCE THIS COMPLEXITY

-INTEL DELIVERS SOLUTIONS

-intها

#### THE IAPX 432:

- 1. LARGE SCALE COMPUTER POWER

- 2. INCREMENTAL PERFORMANCE CAPACITY

- 3. HIGHLY DEPENDABLE HARDWARE AND SOFTWARE

- 4. INCREASED PROGRAMMER PRODUCTIVITY

----INTEL DELIVERS SOLUTIONS

-intel

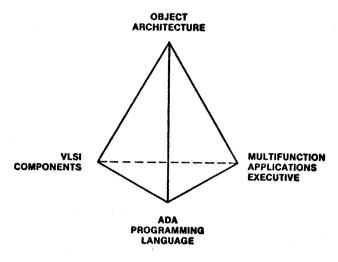

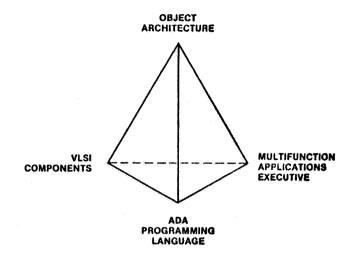

#### HOW?

BY COMBINING INTEL'S LEADERSHIP

IN VLSI TECHNOLOGY

WITH

AN ADVANCED OBJECT-BASED ARCHITECTURE

——INTEL DELIVERS SOLUTIONS lacktrianglet

## 432 LARGE SCALE COMPUTER POWER

- VIRTUAL ADDRESSING

- 240 BYTES OF VIRTUAL ADDRESS SPACE

- 224 BYTES OF PHYSICAL ADDRESS SPACE

- HIGH LEVEL LANGUAGE INSTRUCTION SET

- THE SILICON OPERATING SYSTEM

- INDEPENDENT AND DECENTRALIZED I/O

- PROTECTION TO THE DATA STRUCTURE LEVEL

- MAINFRAME SYSTEM PERFORMANCE

-INTEL DELIVERS SOLUTIONS

-intel

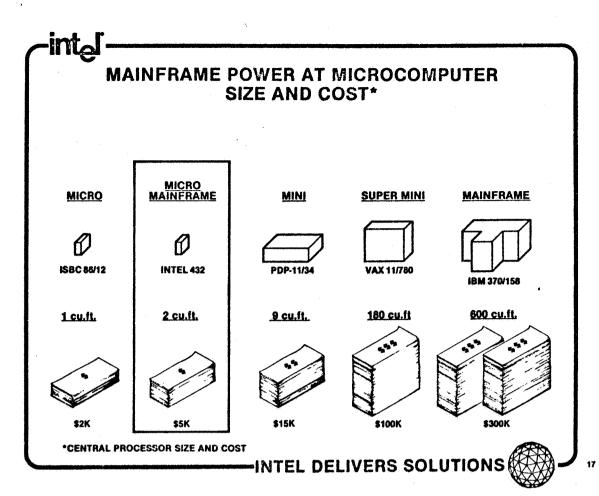

## MAINFRAME SYSTEM PERFORMANCE

THROUGH MULTIPLE PROCESSORS

## THE IAPX 432 HAS TRUE 32-BIT MAINFRAME FUNCTIONALITY

**IAPX 432 FUNCTIONALITY**

ADDRESS SPACE INSTANTANEOUS VIRTUAL

TYPICAL 16-BIT FUNCTIONALITY

DATA TYPES

8, 16, 32, 64 and 80-BIT BOOLEAN, CHARACTER ORDINAL, INTEGER, REAL LONG ORDINAL, INTEGER, REAL

216-218 NO SUPPORT

INSTRUCTION SET

HIGH LEVEL (e.g., A = B + C) MULTI-OPERAND (0-3)

8, 16-BIT BOOLEAN, CHARACTER ORDINAL, INTEGER

VECTOR, RECORD

ASSEMBLY LEVEL TWO OPERAND REGISTER BASED

NO

INDEPENDENT PARALLEL

DEPENDENT SLAVED

**PROTECTION**

FINELY GRAINED ... PER DATA STRUCTURE

COARSE

SUPERVISOR/USER

## -int<sub>e</sub>l

## ADVANCED ADDRESSING AND PROTECTION

- PROTECTION TO THE DATA STRUCTURE LEVEL

- ENCAPSULATION TO THE LOWEST LEVEL PROGRAM UNIT

- "NEED TO KNOW" ADDRESSING

- DETECTION AND CONFINEMENT OF ACCESS VIOLATIONS

...FOR HIGHLY DEPENDABLE SOFTWARE SYSTEMS

INTEL DELIVERS SOLUTIONS

intط

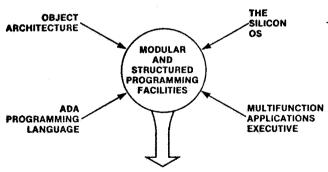

## IMPROVED PROGRAMMER PRODUCTIVITY

**BUILT-IN SOFTWARE DESIGN METHODOLOGY**

## intel

## THE 432 ARCHITECTURE

- OVERCOMES FUNCTIONAL BARRIERS

- TRUE 32-BIT MAINFRAME FUNCTIONALITY

- OBJECT-BASED SUPPORT FOR STRUCTURED PROGRAMMING

- HIGH LEVEL LANGUAGE INSTRUCTION SET

- THE SILICON OS

- IMPROVES PROGRAMMER PRODUCTIVITY

---INTEL DELIVERS SOLUTIONS

-int<sub>e</sub>l

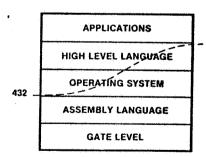

## THE 432 RAISES THE HARDWARE/SOFTWARE INTERFACE

THROUGH THE SILICON OS

-INTEL DELIVERS SOLUTIONS

28

## -int<sub>e</sub>l

## THE SILICON OS

- BUILT INTO THE INSTRUCTION SET

- PROCESS SCHEDULING AND DISPATCHING

- INTERPROCESS COMMUNICATION AND SYNCHRONIZATION

- STORAGE RESOURCE MANAGEMENT

- IMPROVES PERFORMANCE

AND

**LOWERS SOFTWARE COSTS**

-INTEL DELIVERS SOLUTIONS

## intel

## CAREFUL SEPARATION OF OS MECHANISMS (IN SILICON) AND POLICIES (IN SOFTWARE) ALLOW APPLICATIONS TO BE OPTIMIZED

## **EXAMPLE MECHANISMS**

PROCESSORS AUTOMATICALLY

DISPATCH PROCESSES BASED ON

PRIORITY

DEADLINE

TIME SLICE

MEMORY ALLOCATION

TOTAL STORAGE (

MAX INCREMENTS (

PARAMETERS

## **EXAMPLE POLICIES**

REAL TIME, TIME-SHARING, BATCH ANDIOR DYNAMIC LOAD SHARING CAN BE OPTIMIZED BY SOFTWARE POLICIES SETTING PARAMETERS

MEMORY ALLOCATION PROCEEDS AUTOMATICALLY UNTIL BOUNDS EXCEEDED. SOFTWARE POLICIES THEN HANDLE REQUEST FOR MORE

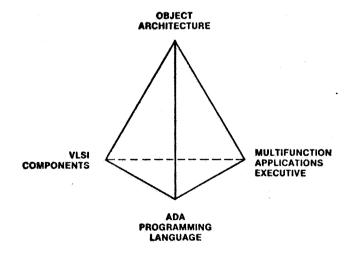

## THE MULTIFUNCTION APPLICATIONS EXECUTIVE

- BUILDS ON THE SILICON OS FOR ADVANCED

APPLICATION SUPPORT

- A LIBRARY OF FLEXIBLE TOOLS

- COMPLETE RUNTIME ENVIRONMENT

- EASILY MODIFIED AND/OR EXTENDED

-INTEL DELIVERS SOLUTIONS

## THE ADA PROGRAMMING LANGUAGE

- INTENDED FOR

- ∠ SYSTEMS PROGRAMMING

- NUMERICAL PROBLEM SOLVING

- → REAL-TIME APPLICATIONS

- PASCAL INSPIRED

- DIRECTLY REFLECTS AND SUPPORTS THE 432 OBJECT-BASED ARCHITECTURE

- IMPROVES PROGRAMMER PRODUCTIVITY THROUGH:

- STRONG TYPING

- ∠ DATA ABSTRACTION

- ✓ INFORMATION ACCESS CONTROL

intel

## A BUILT-IN SOFTWARE DESIGN METHODOLOGY FOR INCREASED PROGRAMMER PRODUCTIVITY

- AN EXTENSION AND GENERALIZATION OF STRUCTURED PROGRAMMING CONCEPTS

- BASED UPON MODULAR PROGRAMS AND MODULAR DATA STRUCTURES (OBJECTS)

- A COMPREHENSIVE APPROACH TO ORGANIZING AND BUILDING COMPLEX SOFTWARE SYSTEMS

-INTEL DELIVERS SOLUTIONS

inte