# **Pipelines**

12 SEP 1885

# **A Comparison of Two Common Pipelines Structures**

Michael Golden and Trevor Mudge

Electrical Engineering and Computer Science Department

University of Michigan

1301 Beal Avenue

Ann Arbor, Michigan, 48109-2122

email: {mgolden, tnm}@eecs.umich.edu

#### **Abstract**

We examine two pipeline structures that are employed in commercial microprocessors. The first is the load-use interlock (LUI) pipeline, which employs an interlock to ensure correct operation during load-use hazards. The second is the address-generation interlock (AGI) pipeline. It eliminates the load-use hazard, but has an address-generation hazard, which requires an address-generation interlock for correct operation. We compare the performance of these two pipelines on existing binaries and on applications that have been recompiled with a local code scheduler that understands the difference in the pipeline structures. Under the assumption of perfect branch prediction, the AGI pipeline outperforms the LUI pipeline on the SPEC92 integer benchmarks, even on binaries that have been compiled for the LUI pipe. When branch prediction is considered, the AGI pipeline performs significantly better than the LUI pipeline if branch prediction is more than 80% accurate and the data cache access time is greater than two cycles. Recompiling the benchmarks with a new local code scheduler optimized for the AGI pipeline provides little additional performance improvement.

**Keywords**: cache memory, interlocks, memory system, pipelines, RISC

#### 1 Introduction

Although pipelining is a widely used technique for speeding up instruction execution, the existence of dependences between instructions means that pipelines cannot run at 100% efficiency. Nevertheless, the improvement in speed through pipelining usually offsets any loss in performance[17].

This paper will examine three types of "hazards" that can reduce the efficiency of a pipeline: branch, load, and address-generation hazards. In particular we will compare two pipeline organizations employed in several commercial machines that make different trade-offs between these three hazards. The first, which we shall refer to as the load-use interlock (LUI) pipeline, issues and

completes its instructions in-order. It is subject to branch hazards and load hazards, but not address-generation hazards. The second, which we shall refer to as the address-generation interlock (AGI) pipeline, also issues and completes its instructions in-order but differs from the LUI pipeline in that the execute stage is placed later in the pipeline to avoid load hazards. However, this difference results in address-generation hazards and increases the penalty for branch hazards. In this paper we will report on experiments to determine if these penalties are outweighed by the benefits of eliminating load hazards.

The MIPS R2000 and R3000 use a precursor to the LUI pipeline. This precursor does not employ hardware interlocks for loads or branches. Instead, NOPs are inserted after loads and branches, as required, to ensure correct operation. Load interlocks were added in the R6000, a short-lived ECL implementation of the MIPS instruction-set architecture (ISA) [16]. Load interlocks were also subsequently employed in the R4000, R4200, and R4400 [12]. The AGI pipeline is used in the Intel i486 and Pentium and the Cyrix M1<sup>1</sup>, as well as in the R8000[2][3][6] [7]. The R8000, which was originally referred to in the literature as the TFP, also implements the MIPS ISA [5] [8]. All four processors with AGI pipelines are designed to preserve *binary compatibility* with earlier LUI microprocessors. A large body of software exists in the form of binaries optimized for the LUI pipeline structure, and it is not known how much performance is degraded when these binaries are run on the rearranged pipeline. To be acceptable, any reduction must be small to avoid the cost of recompiling applications.

There are two questions that this paper attempts to answer:

- 1. How does the AGI pipeline affect performance on binaries created for an LUI pipeline?

- 2. Does the AGI pipeline improve performance if the compiler performs local code scheduling specifically for this organization?

This paper is organized as follows. The next section discusses pipeline hazards in more detail and previous work on methods to reducing their negative affect on performance. With this as background, Section 3 describes the LUI and AGI pipeline organizations. The compiler and simulation tools are described in Section 4. Experimental results are presented in Section 5 followed by some concluding remarks in Section 6.

<sup>1.</sup> The M1 executes the Intel instruction set, but has one extra address calculation stage than the other pipelines.

# 2 Pipeline hazards and previous work /

#### 2.1 Branch hazards

We define the *scope* of a branch to be the number of instructions that can be issued before the branch is resolved. A *branch hazard* occurs when an instruction in the scope of the branch depends on the outcome of the branch. Although a processor may stall the issue of new instructions until it resolves a branch instruction, the introduction of pipeline bubbles caused by this approach can reduce performance to an unacceptable level.

Branch hazards can be eliminated statically by having the compiler schedule independent instructions in the scope of a branch. Alternatively, the pipeline may dynamically eliminate branch hazards by predicting the outcome of the branch, allowing control-dependent instructions to enter the pipeline, and squashing them if the branch has been mispredicted. These approaches are not mutually exclusive, and it is not unusual for some combination to be employed.

Both approaches to removing branch hazards have shortcomings. It is not always possible to eliminate branch hazards by reordering code. It may be necessary to insert NOPs so that any instructions that cause branch hazards are moved beyond the scope of the branch. As noted, this is the solution taken by the R2/3000. However, the presence of NOPs in the execution stream reduces efficiency. Branch prediction can also introduce inefficiency when a prediction fails and instructions that execute as a result of mispredictions must be squashed.

#### 2.2 Load hazards

Load hazards are a result of data dependences rather than control dependences. They occur when the instructions immediately following a load depend on the value retrieved by the load instruction. We define the scope of a load to be the number of instructions that can be issued before the data retrieved from memory by the load becomes available to later instructions. Because the amount of time required to access a value that may reside in any level of a memory hierarchy may vary, the scope of a load instruction may also vary. A load hazard occurs when an instruction in the scope of a load uses directly or indirectly the value read by the load.

In a pipeline that supports out-of-order execution, an instruction that depends on an outstanding load operation can simply be buffered at a reservation station until all of its operands are avail-

and a series

able and it can be sent to a function unit. In a pipeline that only allows in-order execution of instructions, there are three approaches to tolerating a load hazard: 1) reorder instructions so that there are no instructions that cause load hazards after the load; 2) stall the pipeline when an instruction that causes a load hazard is fetched until the load is completed (load-use interlock); and 3) use some form of load prediction to prefetch load data and effectively remove dependences that arise from the load.

All three approaches to removing load hazards have shortcomings. It is not always possible to eliminate load hazards by reordering code. It may be necessary to insert NOPs so that dependent instructions that cause hazards are moved beyond the scope of the load. Such a processor must still have some interlock to handle the case when the load instruction misses in the first level of memory and extra cycles are required to fetch the missing data. Once again, this is the solution taken by the R2/3000 and again, the presence of NOPs in the execution stream reduces efficiency. The use of load-use-interlock stalls avoids the code expansion of NOPs, but it too reduces efficiency. Finally, loads are much more difficult to predict and the last method is rarely used [4]. Again these approaches are not mutually exclusive.

## 2.3 Address-generation hazards

Address-generation hazards occur when a value is computed for a register that is used to form the address of the data retrieved by a load instruction. For the purposes of this discussion we consider only the base-register-plus-offset address mode for load instructions. In this case, the scope of address generation is the number of instruction slots between an instruction that modifies a register and its earliest availability for use as a base register in an address calculation.

As in the case of any data hazard, a machine that supports out-of-order execution of instructions can simply buffer the dependent instruction until all operands become available. For a pipeline that does not allow this model of execution, there are two approaches to tolerating an address-generation hazard: 1) insert instructions so that there is sufficient time to finish modifying the address register before its use by the load instruction; and 2) stall the pipeline until address generation is completed (address-generation interlock). In principle, address generation could also be predicted but it is never done. Removing address-generation hazards by stalling is, as with the other hazards, a source of inefficiency.

#### 2.4 Other hazards

In addition to the hazards that we are concerned with in this paper, there are others that have only a small impact on the performance of LUI or AGI pipelines, or that are avoided altogether in the LUI and AGI pipelines. In the first category are instructions that store values to memory. During a store operation, the memory system does not return a value to the CPU, so subsequent instructions can usually be issued without delay. A hazard can occur if, before the store completes, a load instruction is issued that retrieves data from the memory location that is the target of the store. Microarchitectural features such as write buffers or write caches with hazard detection logic have been used to solve this problem [11]. In this paper, the effects of store hazards are ignored.

In the second category are hazards resulting from true data dependences on instructions that perform ALU operations: if the results of an instruction are required by a succeeding instruction, and if the second instruction issues before the first instruction computes its result, then a hazard occurs. The LUI and AGI pipelines avoid this class of hazards by implementing ALU operations that only require one cycle and by employing *bypass* paths that send a value from one pipeline stage directly to another stage.

Within the scope of this paper, we shall not be concerned with machines that issue more than one instruction at a time, typified by superscalar or VLIW architectures. Of course, their individual execution pipes are likely to be of the LUI or AGI type, and future studies might investigate their relative merits in this setting where the matter of instruction dependence becomes much more complex. For two excellent discussions on this, the reader is referred to [10] and [18].

# 2.5 Previous work

Previous work has proposed both static and dynamic techniques of eliminating the hazards that instructions dependent on load instructions eause. Static techniques involve code scheduling in which the compiler attempts to hide the latency of load instructions by scheduling them well before their results are needed. In [14], Krishnamurthy presents a survey of techniques for local code scheduling. Global code scheduling techniques, such as superblock[9] and hyperblock[15] scheduling, allow code motion between basic blocks.

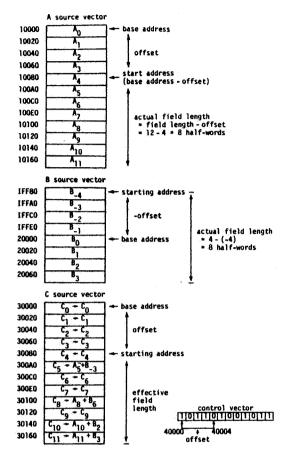

Austin, et al. classify load instructions into three categories [1]:

- 1. Global pointer references to global variables,

- 2. Stack pointer references to variables on the stack frame, and

- 3. *General pointer* references which cover all other loads, including references to pointers and arrays.

They notice that the offsets for global and stack pointer references are often quite large. The offsets are small—the most common offset is zero—for general pointer offsets. Negative offsets arise from negative array references and are most unusual. Because of loop optimizations such as strength reduction, most loads that perform array references within loops have zero offsets.

Because many offsets have small values, a logical OR operation will have the same effect as the full address calculation in most cases. Of course, this method fails for negative offsets and whenever there is a carry in any part of the addition. Their method rapidly predicts the set index into the first level cache by OR-ing together the appropriate bits in the base register and the offset instead of performing the full addition. They propose circuitry that will do this during the instruction fetch stage of the "classic five stage pipeline," (see below) so that during the ALU operation stage, the processor can access the cache while it computes the full effective address. The processor saves a cycle if the prediction is correct. If the prediction fails, the load must be reissued.

Because this only works if there are no carries between the bits of the effective address calculation, they propose that the compiler and linker align the global pointer, objects on the heap, and the stack frames to large powers of two. This eliminates carries in many address calculations. These software and hardware optimizations increase data memory allocation up to 20% and memory system usage by up to 50% for some benchmark programs.

Iliffe describes a "forward looking" architecture that immediately issues a memory load whenever the processor forms a potential address instead of waiting for an actual load instruction to be encountered in the instruction stream [13]. In Iliffe's proposal, all registers are tagged. A potential address is created through normal machine instructions that have a destination tagged as an address register. As soon as the processor writes a value to an address register, the machine issues a load to that address.

Sohi and Davidson describe the Structured Memory Access architecture, or SMA[22]. This

machine has an address processing unit that can accept a pattern in memory and issue loads to all addresses in the pattern before the values are actually used. This feature works well to exploit the natural regularity of memory accesses to structures like vectors and multidimensional arrays.

Golden and Mudge propose a microarchitectural cache called a load target buffer (LTB) which is indexed with the program counter during the instruction fetch stage of a pipeline[4]. If the LTB indicates that the current instruction is a load, the processor immediately issues a request to the memory system using a prediction of the required address. The LTB makes this prediction using a history of memory locations accessed by a given load instruction, and can successfully predict the targets of load instructions which have constant-stride reference patterns.

# 3 Two pipeline organizations

# 3.1 The load-use interlock pipeline

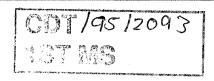

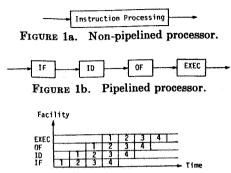

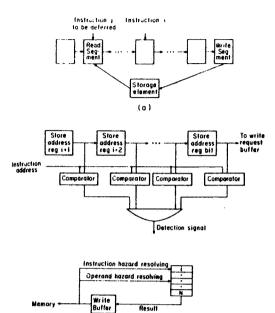

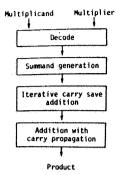

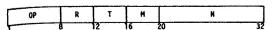

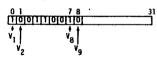

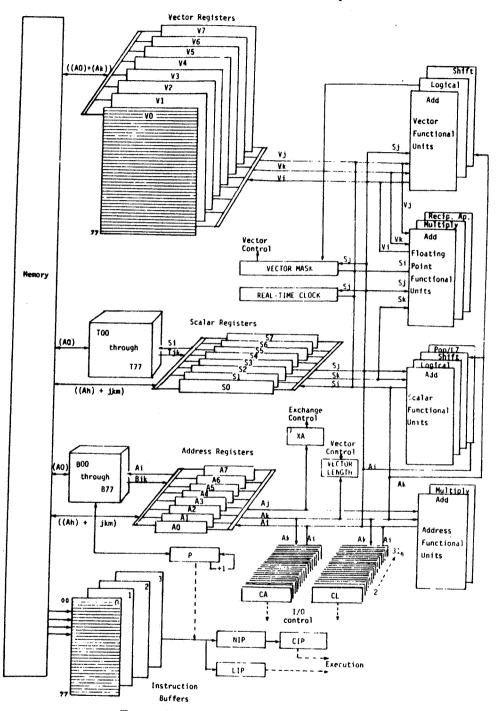

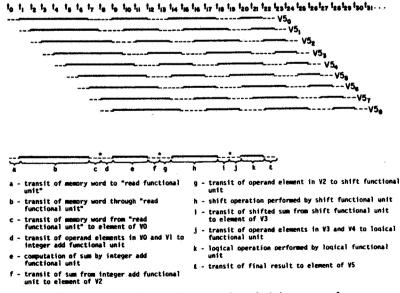

The LUI pipeline is shown in Figure 1. This has been referred to as the "classic five stage RISC pipeline" [20]. Each box represents a single machine cycle and a list of the functions that are performed during that cycle. Figure 1 labels the five stages with their primary function:

- IF instruction fetch

- RD register read and decode

- EX execute the ALU operation

- MEM data cache access

- WB write back to the register file

The bypass paths are also shown. The number of cycles spanned by the path indicates how long the bypass operation takes.

Figure 1 shows that conditional branches are not resolved until the end of the first half of the EX stage. This results in a branch scope of one cycle, during which a branch hazard can occur. This is solved by the inclusion of a *branch-delay slot* in the MIPS ISA. Correct operation requires that the instruction in the branch-delay slot must be able to execute independently of the result of the branch. If an independent instruction cannot be found, a NOP is inserted into the branch-delay slot.

Figure 1: The LUI Pipeline

The five stages and bypass paths are shown. The actions in the EX stage that are underlined are moved into the MEM stage in the AGI pipeline. See Figure 3.

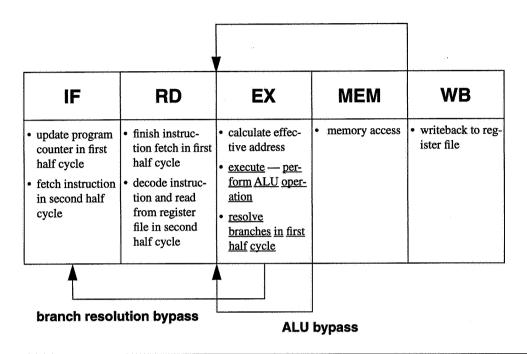

Figure 2: The LUI-N Pipeline

The extra memory cycles and the corresponding increase in the load-use bypass are shown.

During a load instruction, the effective memory address is computed during the EX stage and sent to the memory system. If the request hits in the first level cache, the result is available at the end of the MEM stage, where it may be forwarded back to the EX stage. The forwarding path spans two cycles, indicating that the MEM stage result is not available to the instruction that immediately

follows it in the pipeline, but to the second instruction after the load. Any instruction immediately after a load that uses the result of that load creates a load hazard. In such cases, the pipeline stalls for one cycle. Of course, if the instruction misses in the cache, the delay is much greater and the pipeline stalls for many cycles.

In the early MIPS machines (R2000 and R3000), as noted earlier, the absence of a load-use interlock is handled by requiring that the compiler guarantee that the instruction after a load is not dependent on the load. This instruction occupies the *load-delay slot*. If the compiler cannot find an independent instruction, it puts a NOP instruction in the load-delay slot [12].

In high clock rate microprocessors, even the on-chip primary cache can take more than one cycle to access. This paper will also consider a generalization of the LUI pipeline to systems with multiple-cycle data cache access times. These pipelines will contain additional MEM stages. A data cache with an access time of N cycles will be paired with a LUI pipeline with N MEM stages, and will be referred to as an LUI-N pipeline (see Figure 2). In an LUI-N pipeline, the scope of a load is N instructions and its load-use interlocks can last from 1 to N cycles. If the first dependent instruction in the load scope is k instructions after the load, then the interlock will stall the pipeline for (N-k)+1 cycles.

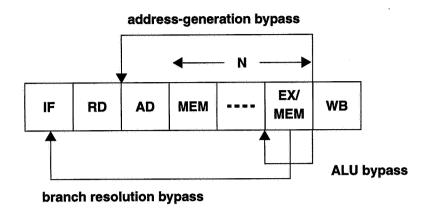

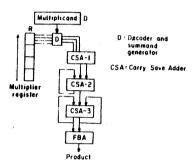

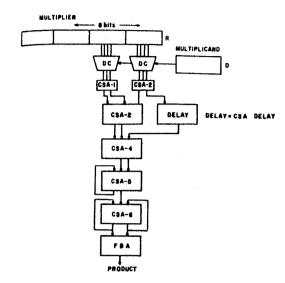

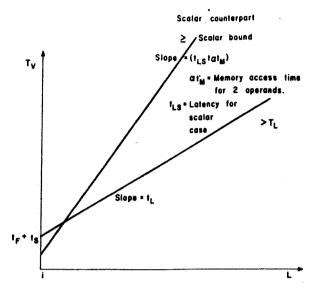

#### 3.2 The address-generation interlock pipeline

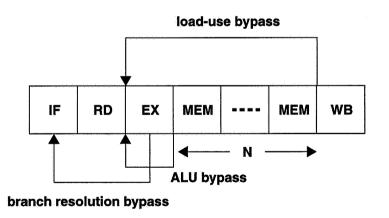

The AGI pipeline is shown in Figure 3. In this pipeline, the load-use interlock has been eliminated by delaying the EX stage by one cycle and combining it with the MEM stage. Combining the EX and MEM stages requires an extra adder, which is dedicated to computing the target address of memory operations. This address calculation is performed in the AD stage before the EX/MEM stage. In contrast, the LUI pipeline has only a single adder in the EX stage, which is used for both integer arithmetic instructions and address calculations. In the AGI pipeline, when an instruction that is dependent upon a load in the previous cycle reaches the EX/MEM stage, the results of the load are available from the ALU bypass. However, branch resolution now occurs one stage later because a conditional branch instruction may require a result from the instruction that immediately precedes it. This result will not be available until the end of the EX stage.

There are two disadvantages to this arrangement. First, an address-generation interlock is re-

Figure 3: The AGI Pipeline

The five stages and bypass paths are shown. The actions in the EX/MEM stage that are underlined are moved from the EX stage in the LUI pipeline. See Figure 1.

quired when a load instruction requires the register result of an uncompleted instruction to calculate the target address in memory. Second, the branch scope is now two cycles because branch resolution occurs in the first half of the EX/MEM stage of the pipeline. This means that in addition to the branch-delay slot, a second instruction will issue before the branch is resolved. We assume that this instruction is chosen by a prediction scheme, and that it may have to be squashed if the branch has been mispredicted. This contrasts with the LUI pipeline which, because of the branch-delay slot, needs no branch prediction strategy.

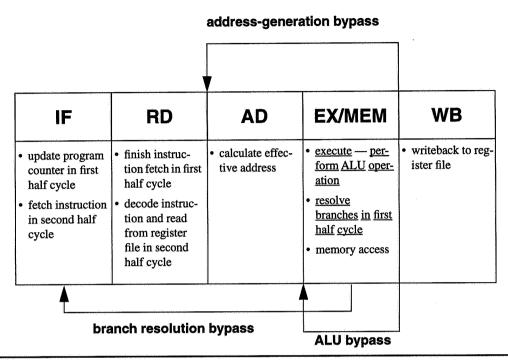

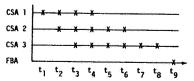

As cache access time grows beyond a single cycle, delay stages can be added to the AGI pipeline between the AD and EX/MEM stages. A processor that takes N cycles to access the cache will require N-1 extra MEM stages. We refer to this as an AGI-N pipeline, as shown in Figure 4. In an AGI-N pipe, N instructions must be squashed every time a branch is mispredicted, and addressgeneration interlocks can last from 1 through N cycles. If the first dependent load instruction is issued k cycles after the instruction that generates its base register, then the interlock will stall the pipeline for (N-k)+1 cycles.

Figure 4: The AGI-N pipeline showing the bypass paths

The extra memory cycles and the corresponding increase in the address-generation bypass are shown.

The code fragment written in MIPS assembly language shown in Figure 5 further illustrates the difference between the two pipeline organizations. NOPs in load-delay slots have been removed—load-use interlocks are modeled instead. The code is taken from the program eqntott, a SPEC92 integer benchmark. In this example, instruction I3 depends on instruction I2, which in turn depends on instruction I1. Because the branch instruction I3 depends on I2, a load-use interlock will occur in an LUI pipeline. This interlock does not occur in the AGI pipeline. Instead, an address-generation interlock will stall the pipeline since I1 calculates a value for the base register of the load instruction I2. In addition to the address-generation interlock, the AGI pipeline may face an additional possible performance loss if the branch is mispredicted. In the case of the LUI pipeline, the NOP in the branch-delay slot covers the branch penalty. For every memory access stage in the AGI pipeline, an additional instruction must be squashed after a mispredicted branch. For example, in an AGI-2 pipeline, both I4 and I5 would be squashed if the branch instruction I3 were incorrectly predicted not-taken. Note that for both the LUI and the AGI pipeline, the instruction after the branch occupies a branch-delay slot. Only the additional instructions in the branch scope for the AGI pipeline are speculatively executed.

```

# move the value in register a0 into register a3

I1:

move

a3,a0

use it as the base register to load register v1

v1,4(a3)

I2:

lw

# conditionally branch on v1 == 0

v1, zero, 0x400328

I3:

beq

nop

# v1 != 0, so put the value in v1 into a0

I4:

move

a0,v1

# and call copy_bnode(a0)

I5:

jal

copy_bnode

```

Figure 5: A MIPS assembly language fragment

This code fragment illustrates a load-use hazard and an address-generation hazard.

# 4 The compiler and simulator

This paper considers programs compiled for the MIPS I instruction set architecture—the version of the architecture that does not support load-use interlocks. This architecture was chosen for several reasons:

- The MIPS architecture has been implemented with a LUI pipeline and with an AGI pipeline. The R series machines all have LUI pipelines and the TFP has an AGI pipeline.

- The Gnu C Compiler (GCC) is available for the MIPS architecture [23]. GCC is in the public domain and the source codes are easily available, so the compiler may be modified.

- The MIPS is a load/store architecture, so all memory operations are contained in explicit load and store instructions. This simplifies the creation of compilers that optimize for the two different pipeline structures.

The experiments use the SPEC 92 integer benchmarks, summarized in Table 1. All of the benchmark programs are executed to completion using one of the "reference" input files provided by SPEC except xlisp, which uses the "short" input file. The benchmarks are compiled three times. The MIPS C Compiler creates one version of each program. The MIPS C Compiler heavily optimizes the code and assumes a single load-delay slot. In effect, this provides a binary that is optimized for load instructions that have a scope of one cycle on a cache hit. GCC is used to create two versions of each benchmark: one optimized for the AGI pipeline and one optimized for the LUI pipeline. The versions differ in the cost function given to GCC's scheduling algorithm.

GCC's scheduler assigns a priority to each instruction in a basic block. Instructions with high priorities are scheduled first. Several factors determine the priority of an instruction, but the most

| Bench-<br>mark<br>Name | Input File | Base Execu-<br>tion Time in<br>Cycles | Average<br>Basic<br>Block<br>Size |

|------------------------|------------|---------------------------------------|-----------------------------------|

| compress               | reference  | 79 192 765                            | 5.1                               |

| eqntott                | reference  | 1 381 970 038                         | 3.0                               |

| espresso               | bca.in     | 493 384 704                           | 5.6                               |

| gcc                    | stmt.i     | 133 778 490                           | 5.0                               |

| sc                     | loada1     | 436 172 261                           | 4.6                               |

| xlisp                  | short      | 1 171 528 797                         | 3.0                               |

Table 1: The SPEC92 integer benchmarks and their characteristics

The reference input files provided by SPEC are used for all of the benchmarks except xlisp, which uses the SPEC-provided short input file due to simulation time considerations. When several SPEC reference input files are available, the experiments use the file listed in the table. The base execution time is the time required to execute the benchmark to completion on a processor with a zero-cycle cache access time.

important is the scope of an instruction. An instruction with a large scope that produces results used by a later instruction is assigned a high priority equal to the number of instructions in its scope. Once the instructions are prioritized, GCC attempts to schedule each instruction so that the pipeline will never interlock. For a discussion of scheduling techniques for pipelined processors, see [14].

To provide a binary that optimizes for load-use hazards, one version of each benchmark is produced in which GCC is told that two instructions are required between a load and its use for interlock-free execution. To create a version optimized to reduce address-generation hazards, the scheduler is told that the scope of address generation is two cycles. The study includes the MIPS C Compiler version because it is the standard compiler for systems using the MIPS processors.

Comparing the code produced by GCC with the MIPS C Compiler's version provides a confidence check that the code that is produced by GCC for the AGI pipeline is equally well optimized.

Each version of the program is then instrumented to produce an instruction and data trace by pixie. A simulator based on the xsim tool developed by Smith consumes the trace [21]. The simulator models a machine with the following characteristics:

• There are no load-delay slots. Other delay slots, mainly those required by the MIPS architecture for integer multiply and divide instructions, are present in the machine model. This

includes a single branch-delay slot for both the AGI-N and the LUI-N pipeline.

- All operations except data cache accesses complete in a single cycle.

- There is a single execution pipeline.

- All memory references hit in the instruction and data caches.

- Instruction fetch requires a single cycle.

Load-delay slots have been eliminated in newer RISC architectures, such as the Alpha, in favor of load-use interlocks. As cache access times get longer, code expansion caused by NOPs in unfilled delay slots becomes a problem [19]. Typical RISC integer instructions complete in a single cycle, except integer multiplication and division, which usually take more than one cycle. The MIPS ISA requires delay slots in the scope of these instructions, which must be filled by independent instructions or NOPs.

# 5 Experimental results

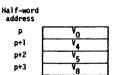

# 5.1 Experiments on an ideal pipeline

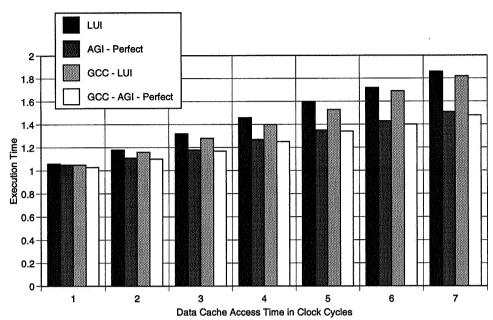

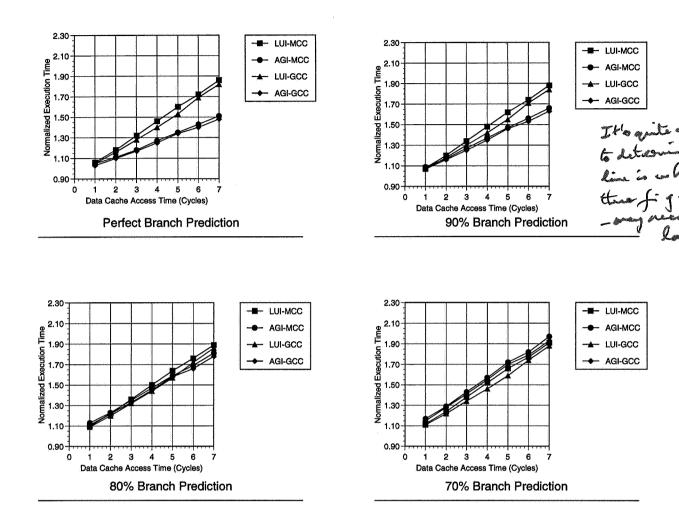

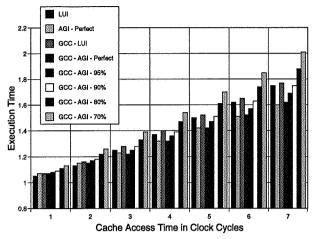

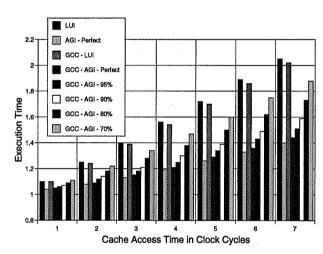

In the figures in this section, the x-axis shows the access time of the data cache in cycles. The y-axis shows an execution time that is normalized to the run time of code compiled by the MIPS C Compiler for a machine with an LUI pipeline and a zero-cycle cache access time (N = 0). In other words, all memory references are immediately available so there are no load-use hazards or address-generation hazards in the reference machine. The third column of Table 1 lists these base execution times for each benchmark in cycles. The harmonic means of the experimental results for all benchmarks are presented in Figures 6-9. Results for individual benchmarks are shown in Figures 10-15. High numbers indicate poor performance. When the benchmarks eqntott and xlisp are simulated for large cache access times, their run times overflow the cycle-counting capabilities of the simulator. Because of this, some of the experiments are missing from Figure 12 and Figure 15 for cache access times of six and seven cycles. To make the comparison between pipelines fair, xlisp and eqntott are removed from the harmonic mean calculations for these two cache access times.

The first experiment compares how the benchmarks perform on code compiled by the MIPS C Compiler for the MIPS R2000 performs on an LUI and an AGI pipeline for varying cache access

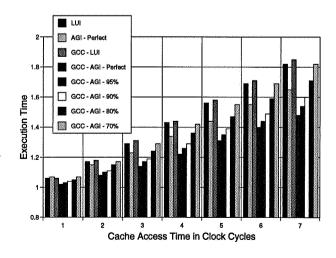

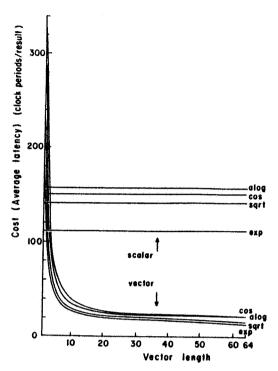

Figure 6: The harmonic mean of all benchmarks — 1-cycle I-Cache

This figure assumes perfect branch prediction. Notice that the improvement between GCC-LUI and GCC-AGI-Perfect is about the same as the improvement between LUI and AGI-Perfect. Informing GCC's local scheduler of the need to avoid address-generation interlocks has little effect. The AGI pipeline shows better performance than the LUI pipeline in all cases.

times. The results assume perfect branch prediction in the AGI case. These bars are labeled "LUI" and "AGI - Perfect" Figure 6. For low cache access times, there is very little difference between the two pipeline organizations. As the access time increases beyond about 3 cycles, the performance benefit of the pipeline with an address-generation interlock begins to appear. The AGI-3 pipeline completes the benchmarks almost 10% faster than the LUI-3 pipeline. The performance gap continues to grow as the cache access time gets larger.

This first experiment answers the question about the performance of existing binaries. For our sample set of benchmarks, the AGI pipeline actually performs slightly better than the LUI pipeline on binaries compiled for an LUI pipeline.

The next set of experiments considers code compiled by GCC for LUI pipelines against code compiled by GCC for AGI pipelines. The programs are run on the pipelines for which they were compiled with the assumption of perfect branch prediction. In Figure 6, these experiments are labeled "GCC-LUI" and "GCC-AGI-Perfect." Once again, a small benefit is seen through the use of AGI pipelines for small cache access times. As cache access times increase, AGI pipelines again provide a larger speedup.

Informing GCC's local scheduler of the new pipeline structure does not seem to affect execution time to a large extent. The percent change between the GCC-LUI experiments and the GCC-AGI experiments are similar to those between the LUI and the AGI-Perfect experiments. This may be because GCC's scheduler works only within a single basic block. For the benchmarks under consideration, the basic block size tends to be small, as small as 3 in the case of xlisp, so modifying the code scheduling costs may not have a large effect. The limited improvement obtained from the compiler suggests that more aggressive global scheduling techniques may be needed. However, the performance of the Gnu C Compiler versus the MIPS C Compiler—compare LUI vs. GCC-LUI—makes it clear that, for our machine model, GCC is as good as one of the best commercial compilers. This gives support for our remaining results with GCC.

This set of experiments gives a limited answer to the second question posed in the introduction. Simply altering the local scheduling algorithm does not significantly improve the compiler's ability to produce efficient code for the AGI pipeline. However, the performance of the AGI pipeline is already better, as shown above. More sophisticated compiler techniques may provide further improvement.

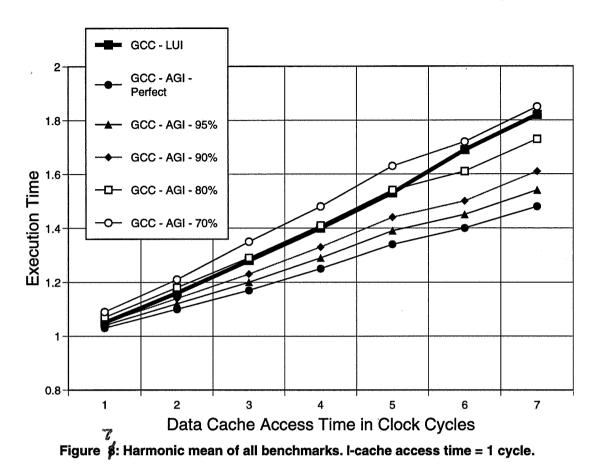

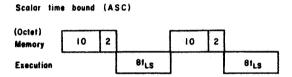

The final set of results, labeled "GCC-AGI-X%" represent AGI pipelines with X% branch prediction over all branches, including unconditional jumps and calls. These results are summarized in Figure 7. Because the MIPS branch delay slot is included in the simulator, all of the results for LUI pipelines are valid for any branch prediction accuracy. The branch penalty is accounted for by the instruction in the delay slot, which may be a NOP. In contrast, an AGI-N pipeline must squash N extra instructions when a branch is mispredicted. A branch penalty is approximated by assessing a fixed number of cycles for each mispredicted branch and adding it to the total execution time of the benchmark. The penalty for machines with LUI and AGI pipelines are calculated with the following formulas:

$$\begin{aligned} & \text{Penalty}_{LUI} = (N_i - 1) \times (1 - b) \times C_b \\ & \text{Penalty}_{AGI} = (N_d + N_i - 1) \times (1 - b) \times C_b \end{aligned}$$

where  $N_d$  is the date cache access time and  $N_i$  is the instruction cache access time in machine cycles, b is the branch prediction accuracy expressed as a probability, and  $C_b$  is the dynamic

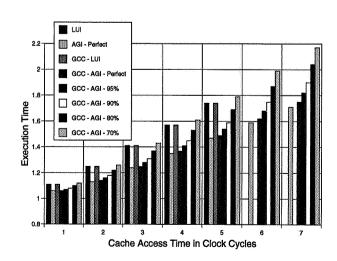

This figure shows the results when branch prediction is taken into account. The AGI pipeline suffers from reduced performance when accurate branch prediction is not available.

branch count of the program. In accordance with the pipeline structures described above,  $N_i$ =1 for both pipelines.

For machines with accurate branch prediction, the AGI pipeline still outperforms the LUI pipeline. Once the accuracy of branch prediction drops down to around 80%, the two types of machines perform equivalently. At lower levels of branch prediction accuracy, the early branch resolution of the LUI pipeline allows it to run programs more quickly.

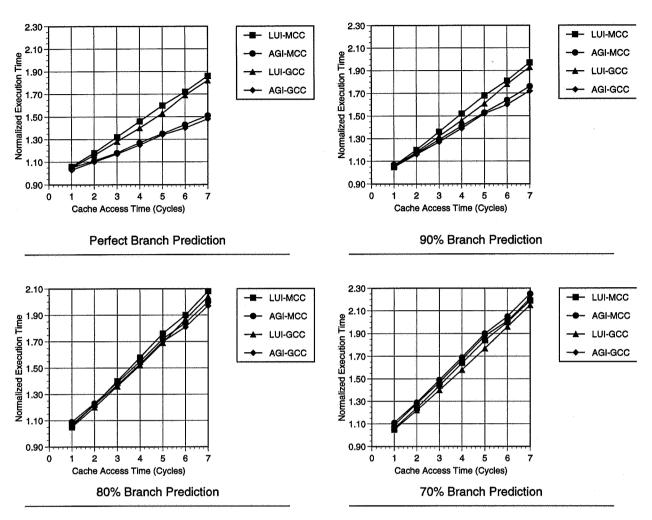

### 5.2 Pipelines with multi-cycle instruction cache access time

The experiments so far assume that the instruction cache can be accessed in a single cycle—the pipelines described in Section 3 have a single IF stage. As the I-cache latency increases, the penalty for a mispredicted branch increases, because more time is required to fetch the correct instruction from the memory system. In other words, the scope of a branch instruction grows.

Figure 8: Harmonic mean of all benchmarks. I-cache access time = D-cache access time.

The results labelled MCC have been compiled by the MIPS C Compiler. The results labelled GCC have been compiled by the Gnu C Compiler. The AGI pipeline still requires good branch prediction to outperform the LUI pipeline.

In an LUI system with a multi-cycle I-cache access time, the branch penalty is no longer completely hidden by a single branch delay slot. As a consequence, the requirement that an AGI pipeline have accurate branch prediction to outperform an equivalent LUI pipeline may be eased. Figure 8 shows this is not the case. In this figure, the I-cache access time has been set to equal the D-cache access time. The LUI pipeline experiences a branch penalty in this experiment, but it is less affected by poor branch prediction than the AGI pipeline. Branch prediction still must be better than about 80% accurate for the AGI pipeline to have a performance advantage for machines with slow caches. On machines that have fast caches or poor branch prediction, both pipelines have similar performance.

A chip designer may decide to optimize the speed of the I-cache over the speed of the D-cache in order to ensure a steady supply of instructions. The initial set of experiments represent a machine of this type—the I-cache has an access time of one cycle but the D-cache access time varies. If the I-cache access time is increased to two cycles, the performance penalty for a branch miss on the AGI pipelines increases by one cycle and, in the LUI pipeline increases to one cycle because the single branch delay slot cannot hide two cycles of I-cache latency. Figure 9 gives performance for a machine with varying access times for the D-cache but an I-cache access time fixed at two cycles. Once again, the same trend appears. For machines with poor branch prediction or a fast data cache, the LUI pipeline runs faster than the AGI pipeline. When the data cache access time increases and branch prediction becomes more accurate, the AGI pipeline becomes more efficient than the LUI pipeline.

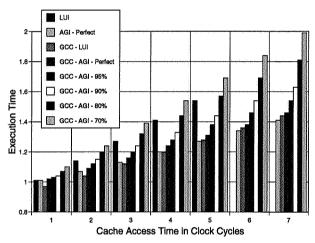

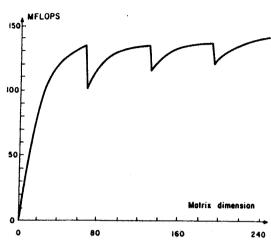

#### 5.3 Pipeline performance on individual benchmarks

Because significant performance improvement is seen in some of the benchmarks, even without sophisticated compiler support, one can examine the properties of the benchmark itself to see where the improvements occur. Figures 10-15 show the results of all experiments on a machine with a 1-cycle I-cache access time for each benchmark. Programs that rely heavily on dynamic data structures see a particularly large benefit from the AGI pipeline. For example, in the benchmark sc, which performs spreadsheet calculations, the AGI pipeline outperforms the LUI pipeline even with poor branch prediction. espresso and gcc also realize significant performance benefits. In these programs, the processor reads from records with many fields. A base register pointing to the beginning of the record needs to be set up, but only once. Once this register is initialized, the values in the fields can be loaded using constant offsets. Only the instruction that sets the base register can cause an address-generation interlock, while each load instruction that follows it has the potential of causing a load-use interlock. Using an AGI pipeline seems to be a good way to increase performance on these "pointer-chasing" benchmarks.

#### 6 Conclusions

A number of processors have recently been announced that eliminate the load-use interlock by overlapping the execute stage of the pipeline with cache access rather than address generation. These AGI machines are designed not only to execute code compiled specifically for them, but

Figure 9: Harmonic mean of all benchmarks. I-cache access time = 2 cycles.

The results labelled MCC have been compiled by the MIPS C Compiler. The results labelled GCC have been compiled by the Gnu C Compiler.

also to run codes compiled for older, LUI, implementations of similar architectures. When good branch prediction methodologies are available, the rearranged pipeline provides improved performance for machines with moderate to large cache access times, even if existing binaries are used. When a branch-delay slot can hide instruction cache latency in an LUI pipeline, high branch prediction accuracy is required for the AGI pipeline to have a performance benefit. As the I-cache access time grows, this trend remains the same.

Simply modifying the compiler's local scheduler shows only a small increase in the benefits of the AGI pipeline. Because basic blocks can be quite short in nonscientific programs, the local

scheduler does not have many instructions to work with. Global scheduling techniques may be able to further improve the performance of the AGI pipeline structure because these methods make more instructions available to be placed between the dependent instructions that cause the interlock.

Two questions remain unanswered. First, in the experiments described in this paper, perfect caches are assumed. In the presence of cache misses, the average time to fetch an instruction and operate on data memory will increase. Cache misses may be distributed such that the effect on these experiments is merely to increase the effective latency to the cache. However, they may be distributed such that pipeline behavior changes noticeably as cache access time and miss rates change.

Second, we have simulated machines that have a single execution pipeline. In a processor with multiple pipelines, each stall cycle can delay the completion of many instructions rather than just one. This may also affect the performance difference between the two pipelines. We leave the study of these two issues as future work.

# 7 Bibliography

- [1] T. M. Austin, D. N. Pnevmatikatos, and G. S. Sohi, "Streamlining data cache access with fast address calculation," *Proc. 22nd Ann. Int'l. Symp. Computer Architecture*, June 1995, IEEE Computer Society Press.

- [2] B. Case, "Intel reveals Pentium implementation details," *Microprocessor Report*, vol. 5, no. 23, pp. 9–17, 1993.

- [3] J. H. Crawford, "The i486 CPU: executing instructions in one clock cycle," *IEEE Micro*, pp. 27-36, February, 1990.

- [4] M. Golden and T. Mudge, *Hardware support for hiding cache latency*, Technical Report CSE-TR-152-93, The University of Michigan, Department of Electrical Engineering and Computer Science, Ann Arbor, MI, 48109-2122, 1993.

- [5] L. Gwennap, "TFP designed for tremendous floating point," *Microprocessor Report*, vol. 7, no. 11, pp. 9–13, August 1993.

- [6] L. Gwennap, "Cyrix describes Pentium competitor," *Microprocessor Report*, vol. 7, no. 14, pp. 1,6–10, October 1993.

- [7] L. Gwennap, "Intel reveals Pentium implementation details," *Microprocessor Report*, vol. 7, no. 4, pp. 9–17, March 1993.

owit

- [8] P. Y. T. Hsu, "Designing the TFP microprocessor," MICRO, vol. 14, no. 2, pp. 23–33, April 1994.

- [9] W. W. Hwu, S. A. Mahlke, W. Y. Chen, P. P. Chang, N. J. Warter, R. A. Birmingham, R. G. Oullette, R. E. Hank, T. Kiyohara, G. E. Haab, J. G. Holm, and D. M. Lavery, "The superblock: An effective technique for VLIW and superscalar compilation," *The Journal of Supercomputing*, vol. 7, no. 1/2, pp. 229–248, 1993.

- [10] M. Johnson, Superscalar Microprocessor Design, Prentice Hall, Englewood Cliffs, N.J., 1991.

- [11] N. P. Jouppi, "Cache write policies and performance," Technical report, Digital Equipment Corporation Western Research Laboratory, 250 University Ave., Palo Alto, CA, 94301, December 1991.

- [12] G. Kane and J. Heinrich, MIPS RISC Architecture, Prentice-Hall, Englewood Cliffs, NJ, 1992.

- [13] J. K. Iliffe, "A forward looking method of cache memory control," *Computer Architecture News*, vol.15, no. 4, pp. 4-10, September 1987.

- [14] S. M. Krishnamurthy, "A brief survey of papers on scheduling for pipelined processors", SIGPLAN Notices, vol. 25, no. 7, pp. 97-106, July 1990.

- [15] S. A. Mahlke, R. E. Hank, J. E. McCormick, D.I. August, and W. W. Hwu, "A comparison of full and partial predicated execution support for ILP processors," *Proc. 22nd Ann. Int'l. Symp. Computer Architecture*, June 1995.

- [16] "MIPS chip set implements full ECL CPU," *Microprocessor Report*, vol. 3, no. 12, pp. 1,14–19, December 1989.

- [17] O. Olukotun, T. Mudge, and R. Brown, "Performance optimization of pipelined memory caches," in *Proc. 19th Ann. Int'l Symp. Computer Architecture*, pp. 181–190, Gold Coast, Australia, May 1992, IEEE Computer Society Press.

- [18] B. R. Rau and J. A. Fisher, "Instruction-level parallel processing: history, overview, and perspective," *The Journal of Supercomputing*, vol. 7, no. 1/2, pp. 9–50, 1993.

- [19] R. L. Sites, Alpha Architecture Reference Manual, Digital press, Maynard, MA, 1992.

- [20] J. E. Smith and S. Weiss, "PowerPC 601 and Alpha 21064: a tale of two RISCs," *Computer*, vol. 27, no. 6, pp. 46–58, June 1994.

- [21] M. D. Smith, "Tracing with pixie", Center for integrated systems, Stanford University, Stanford CA, 94305-4070, 1.1 edition, April 1991.

- [22] G. S. Sohi and E. S. Davidson, "Performance of the structured memory access SMA architecture," *Proc. 1984 Int'l Conf. on Parallel Processing*, pp. 506-513, Bellaire, MI, August 1984.

- [23] R. M. Stallman, *Using and Porting GNU CC*, Boston, MA: Free Software Foundation, Inc., 2.4.5 edition, 1993.

Execution Time

LUI

AGI - Perfect GCC-LUI

GCC - AGI - Perfect

GCC - AGI - 95%

GCC - AGI - 90%

Figure 10: compress

Figure 11: gcc

Cache Access Time in Clock Cycles

Figure 12: eqntott

Figure 13: sc

Figure 14: espresso

Figure 15: xlisp

In these figures, I-cache access time is one cycle.

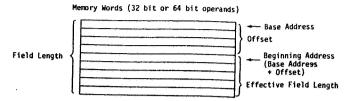

#### Pipeline Architecture

#### C. V. Ramamoorthy

Computer Science Division, Department of Electrical Engineering and Computer Sciences and the Electronics Research Laboratory, University of California, Berkeley, Berkeley, California 94720

and

H. F. Li

Department of Electrical Engineering and the Coordinated Science Laboratory, University of Illinois at Champaign-Urbana, Urbana, Illinois 61801

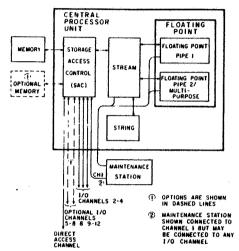

Pipelined computer architecture has received considerable attention since the 1960s when the need for faster and more cost-effective systems became critical. The merit of pipelining is that it can help to match the speeds of various subsystems without duplicating the cost of the entire system involved. As technology evolves, faster and cheaper LSI circuits become available, and the future of pipelining, either in a simple or complex form, becomes more promising.

This paper reviews the many theoretical considerations and problems behind pipelining, surveying and comparing various representative pipeline machines that operate in either sequential or vector pipeline mode, the practical solutions adopted, and the tradeoffs involved. The performance of a simple pipe, the physical speed limitation, and the control structures for penalty-incurring events are analyzed separately. The problems faced by the system designers are tackled, including buffering, busing structure branching, and interrupt handling. Aspects of sequential and vector processing are studied. Fundamental advantages of vector processing are unveiled, and additional requirements (costs) are discussed to establish a criterion for the tradeoff between sequential and vector pipeline processing. Finally, two recent machines (the Cray-1 and the Amdahl 470 V/6 systems) are presented to demonstrate how complex pipeline techniques can be used and how simple but advantageous pipeline concepts can be exploited.

Keywords and Phrases: computer architecture, pipelining, sequential processing, vector processing CR Categories: 5.24, 6.33

#### 1. INTRODUCTION

The principle of pipelining has emerged as a major architectural attribute of most present computer systems. In particular, super machines such as the Texas InstruSystem/360 Models 91 and 195, Cray Research Cray-1, CDC Star-100, Amdahl 470 V/6, CDC 6600, and CDC 7600 have distinct pipeline processing capabilities, either in the form of internally pipelined instruction and arithmetic units or in the form of pipelined special purpose functional units [1-4].

ments TI ASC, Burroughs PEPE, IBM

Copyright © 1977, Association for Computing Machinery, Inc. General permission to republish, but not for profit, all or part of this material is granted, provided that ACM's copyright notice is given and that reference is made to the publication, to its date of issue, and to the fact that reprinting privileges were granted by permission of the Association for Computing Machinery.

<sup>\*</sup> Research sponsored by US Army Research Office Contract DA-ARO-D-31-124-73-G157.

#### CONTENTS

1. INTRODUCTION

1.1 Historical Perspective

1.2 Pipeline Characteristics

1.3 Performance Characteristics

1.4 Control Structure, Hazards, and Penalties

1.5 Sequencing Control

1.6 Software Aspects

2. STRUCTURE OF A PIPELINED PROCESSOR

2.1 An Example Sequential Pipelined Processor

2.2 Buffering

2.3 Busing Structure

2.4 Branching

2.5 Interrupt Handling

2.6 Pipeline Processing of Arithmetic Operations

3. VECTOR PROCESSING

3.2 Implications, Requirements, and Tradeoffs

4. OVERVIEW OF TWO RECENT MACHINES

4.1 The Asynchronous CRAY-1 Computer

3.1 Vector Instruction

4.2 Amdahl 470 V/6 5. CONCLUSION

RFEERENCES

ACKNOWLEDGMENTS

Pipelining is one form of imbedding parallelism or concurrency in a computer system. It refers to a segmentation of a computational process (say, an instruction) into several subprocesses which are executed by dedicated autonomous units (facilities, pipelining segments). Successive processes (instructions) can be carried out in an overlapped mode analogous to an industrial assembly line. So, very loosely, pipelining can be defined as the technique of decomposing a repeated sequential process into subprocesses, each of which can be executed efficiently on a special dedicated autonomous module that operates concurrently with the others.

As an illustration, consider the process of executing an instruction. Normally it involves fetching the instruction, decoding the operations involved, and fetching the

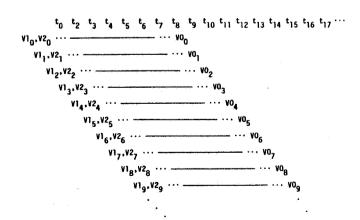

FIGURE 1c. Space-time diagram.

operands before it is finally executed. If this process is decomposed into these four subprocesses and executed on the four modules shown in Figure 1(b), four successive independent instructions may be executed in parallel. Specifically, while the EXEC module is executing the first instruction, the Operand Fetch (OF) module fetches the operand needed for the second instruction, the Instruction Decode (ID) module prepares the different operations for the third instruction, and the Instruction Fetch (IF) module fetches the fourth instruction. The overlapped execution among the four modules is best depicted by a space-time diagram. As drawn in Figure 1(c), the horizontal axis represents the time and the vertical axis the space (modules). From this diagram one can observe how independent instructions are executed in parallel in a pipelined processor.

Some theoretical developments and implications of pipelining are reviewed in this section. A top-down, level-by-level characterization of pipeline applications in computers and the associated configuration control are explained in Section 1.2, Pipeline Characteristics. To reveal the fundamental advantages of pipelining, the space-time measure model is employed to illustrate the ideal throughput (performance) of a pipelined system with no external restrictions or dependencies. This pictorial measure applies to a pipeline of any level operating in an ideal environment. Besides the ideal performance, the limitation of this technique to the lowest level in a computer, namely the logic gate level, is surveyed. Here a practical limitation to the ultimate speed achievable arises because the technique requires the insertion of latches of finite delay. It is shown that this delay plays a significant role in determining the bound on the fastest speed achievable.

On the other hand, when a pipeline operates on tasks with precedence constraints, the space-time measure for the ideal situation is not directly applicable. Section 1.3, Performance Characteristics, analyzes the performance of such a pipe when the precedence relationships are in the form of a tree. Appropriate bounds are provided which reflect that the pipe sometimes has a throughput rate close to its segment time and at other times has a rate close to its flush time. The dominating role played by task relationships in an actual pipeline is thus apparent.

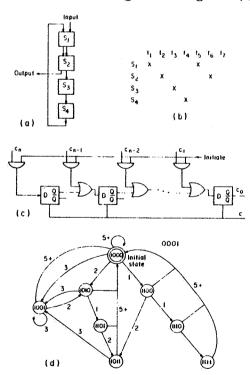

After the analytical evaluation of a pipeline's performance, the various applicable control schemes are classified and compared with respect to the flow of instructions and the resolution of conflicts. This classification covers most of the schemes existing in pipelined systems as well as some theoretically feasible combinations. In Section 1.4, Control Structure, Hazards, and Penalties, three kinds of hazards are formally classified. The detection and resolution techniques for these hazards under either "streamline" or "fully asynchronous" control are analyzed according to the incurred cost in hardware and incurred delay penalties in runtime. Section 1.5, Sequencing Control, presents a simple sequencing control using shift registers as an example of synchronous pipelines whose collisions are predeterminable. This scheme is useful for controlling lower level pipelines such as arithmetic pipes for which external conditions or precedence constraints are rare. Finally, in Section 1.6, Software Aspects, some software problems related to the efficient code generation of a vector pipeline are discussed.

In Section 2, Structure of a Pipelined Processor, the problems and solutions associated with a sequential pipelined system are examined more carefully. Three systems are used as examples to make cross-comparisons in several practical problems. These problems include: 1) buffering for

smoothing congestions; 2) busing structure to reduce delay penalties; 3) branch handling to reduce the disruption of flow; and 4) interrupt handling to ensure a proper interrupt response and later recovery. In Section 2.6, Pipeline Processing of Arithmetic Operations, an example of pipelining fast multipliers is provided to illustrate how a lowest level pipeline can be effectively designed. Such pipelines can often use control schemes like the one in Section 1.6.

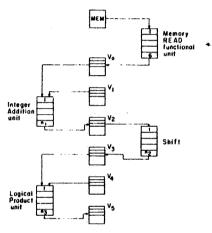

In Section 3, Vector Processing, many special characteristics associated with a vector pipelined system are analyzed separately. Vector pipelines have become economic ways to achieve high throughput for application with suitable parallelism. Specifically, jobs with identical transformations on a set of data can be carried out with minimal control overhead (instruction) and high speed. Two prominent machines, the TI ASC and the CDC STAR-100, are examined. To provide a clear picture, a detailed example of a typical vector instruction (format and execution) is provided. From it one can realize how to use vector instructions and how to achieve skewing on data elements. An analytical comparison between the performance of a vector pipe and that of a sequential pipe is also furnished. This comparison reveals where vector pipelines bring in speedup; however, the additional demands of vector pipelines for proper instruction sets, proper choices of algorithms, and intelligent compilers are also exposed.

Finally, in Section 4, Overview of Two Recent Machines, the special characteristics of two recent pipelined computers are surveyed. The chaining in the CRAY-1 is an example of pipelining applied between vector instructions. With it a very high throughput can be obtained. It is also interesting to observe that the simple pipeline design for the Amdahl 470 V/6 system has proved to be a success.

#### 1.1 Historical Perspective

Computer designers have exploited the overlapped mode of operations since the late fifties. We recount only some significant milestones in its development. For a

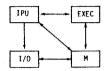

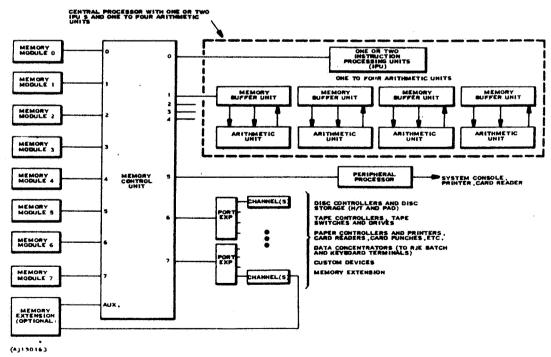

FIGURE 1d. Basic computer structure.

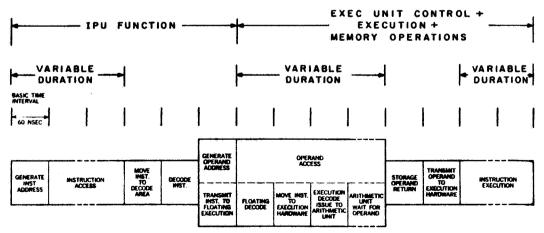

clear understanding of this development, let us model the computer system by the following subsystems (Figure 1(d)):

- The instruction processing unit (IPU)

performs the instructions fetch and

decode, and fetches the operands (if

any) required for the instructions.

- 2) The execution unit (EXEC) performs the desired operation on the operands.

- 3) The input/output unit (I/O) controls the peripheral devices.

- 4) M represents the primary memory of the computer system.

The earliest use of overlapped operations between the CPU (IPU+EXEC), the memory unit (M), and the input/output unit (I/O) can be found in the Univac I, developed during the early fifties. Here the central processor initiates an I/O process; then the CPU and the I/O proceed concurrently. When the I/O operation is completed, an interrupt signal is issued by the I/O controller to alert the CPU of the completion. This asynchronous I/O processing avoids having the CPU wait for the completion of I/O tasks and improves the throughput.

Another type of pipelining where overlap is achieved between the instruction processing unit and the execution unit, has been exploited by later machines. For example, the IBM 7094 used this type of overlap to its advantage. With a 72-bit-wide memory with a memory cycle time of approximately 2 µsec, it executed on the average an instruction (32 bits) with 32-bit operands in two cycles or 4 µsec [22]. With an interleaved and faster memory [1.4 µsec cycle time], the 7094 II achieved an average execution rate of one instruction per cycle of 2 µsec. The Honeywell H-800 (1959) pioneered in multiprogramming, overlapping of I/O, and concurrent computing among a number of programs resident in the memory. Similarly, the Univac LARC (1961) uses interleaved memory and a fourfold overlap (instruction fetch, indexing, data fetch, and execution) and can run one floating-point add per cycle of 4 µsec [22].

Pipelining within the instruction processing unit was implemented in the IBM 360/91 in the sixties. Some functions of the execution unit were also pipelined—for example, the addition and the division processes.

#### 1.2 Pipeline Characterization

Since pipelining can be applied at more than one level, a top-down, level-by-level characterization of pipelining can be conveniently established for analyzing a pipelined system. A pipe can be further distinguished by its design configurations and control strategies. These two points are elaborated below.

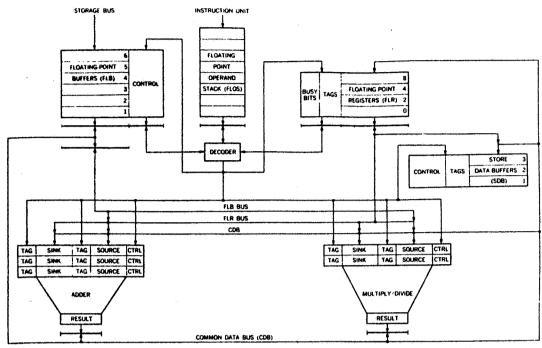

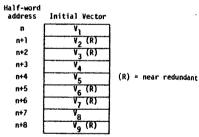

1) Levels of pipelining: Pipelining at the system level is exemplified in the design of the instruction processing unit. The IPU can be decomposed into various functional segments—instruction fetch, instruction decode, address generation, etc. (Figure 1(b)). It takes one minor cycle for a task (instruction) to pass through each segment. Thus, after a stream of tasks enters this pipeline, the pipeline starts outputting one task per minor cycle. Microprogram prefetch—that is, overlap of decoding the current microinstruction—is another example at this level.

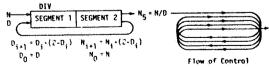

The next level for the application of pipelining is the subsystem level, typical examples of which are the pipelined arithmetic units. Pipelined add, multiply, divide, and square-root functions have been in existence in a number of contemporary computer structures. Figure 1(e) is the conceptual representation of the operation of the divide unit of the IBM 360/91, where, as  $D_i$  iteratively approaches 1,  $N_i$  approaches N/D, the quotient.

2) Pipeline configurations: In addition to the hierarchical levels of pipelining, differ-

FIGURE 1e. 1BM 360/91 divide.

ent design and control strategies classify a pipelined module into one of two forms; it can be either a static or a dynamic pipe. Sometimes a pipelined module only serves a single dedicated function—for example, the pipelined adder or multiplier in the IBM 360/91. Naturally, it can be termed a unifunctional pipe with a static configuration. On the other hand, a pipelined module can serve a set of functions, each with a distinguishable configuration. For example, in the TI ASC system the arithmetic unit in the processor is a pipe that has different configurations (interconnections of modules) for performing different types of arithmetic operations. Such a pipe is called a multifunctional pipe. A multifunctional pipe can be either static or dynamic. In the static case, at any time instant only one configuration is active, therefore pipelining (overlapped processing) is permissible only if the tasks (instructions) involve the same configuration. Most, if not all, multifunctional pipes in arithmetic units of existing machines fall into this classification because static pipes are easier to control, as will become clearer later on. Dynamic multifunctional pipes permit overlapped processing among several active configurations simultaneously. Throughput may be further enhanced, but more elaborate control and sequencing are required. This classification of static and dynamic pipes will be very useful when we consider and evaluate pipelined processor architecture in subsequent sections.

#### 1.3 Performance Considerations

In this section, the advantages, requirements, and limitations of pipelining are reviewed.

1) Throughput considerations: One of the most important performance measures of a system is its throughput rate, defined as the number of outputs (sometimes the number of instructions processed) per unit time. It directly reflects the processing power of a processor system—the higher its throughput rate, the more powerful the system is. Pipelining is one specific technique to improve throughput, as is the use of faster modules.

For this discussion, let us reconsider the example in Figure 1. For a nonpipelined processor, the execution time of an instruction is  $T_{np} = t_1 + t_2 + t_3 + t_4$ . Therefore, for every  $T_{np}$  units of time an instruction is completed; this corresponds to a throughput rate of  $1/T_{np}$ . In the pipelined case, suppose  $t_b = \max\{t_1, t_2, t_3, t_4\} = \text{speed of the}$ slowest facility in the pipeline. Then its maximum throughput rate is  $1/t_b$ , because for every  $T_p = t_b$  units of time, an instruction can leave the pipeline after its execution, if instructions are independent. A direct comparison shows that  $T_p < T_{np}$ ; hence the throughput rate of the pipelined processor  $(1/T_p)$  can be much larger than that of the nonpipelined processor. If  $t_1 =$  $t_2 = t_3 = t_4$ , then the comparison can show a fourfold throughput improvement. From this result we can anticipate that a high degree of parallelism leads to a high throughput rate.

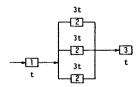

The throughput of a pipeline is determined by its slowest facility, or "bottle-neck." The throughput can be improved by subdivision of the bottleneck element (Figure 1(g)) or by putting facilities in parallel (Figure 1(h)). Both techniques are useful in removing bottlenecks. However, putting facilities in parallel creates more problems in distribution and synchronization of the tasks in the pipeline.

2) Efficiency considerations: Another important performance measure for a system is its efficiency, sometimes called its utilization factor. Efficiency also directly re-

FIGURE 1f. Facility 2 is the bottleneck.

FIGURE 1g. Subdivision of facility 2.

FIGURE 1h. Paralleling of facility 2.

flects how effective a processing scheme is and can be used to indicate how future improvements, such as removal of bottlenecks, should progress. Like most performance measures, it can be evaluated both analytically and experimentally by measurements. Here an attempt is made to illustrate the analytical efficiency of pipeline processing via the space-time relationship introduced earlier.

It is natural to view efficiency as the percentage of busy (productive) periods with respect to a certain time span. Here a slight complication arises because a pipelined processor consists of several modules, some of which may be busy while the others are idle. To evaluate the efficiency of the processor system as an entity, Chen [7] proposes a uniform space-time span index:

efficiency of pipeline

$= \frac{\text{total space-time span of tasks}}{\text{total space-time span of facilities}}.$

where the term "task" (process) is used to fit the loose definition of a pipeline. Sometimes the modules in the pipeline are of different natures with different importance (or cost) factors. A refined index which also includes such considerations has been suggested in [8]:

efficiency of pipeline

$= \frac{\text{total weighted space-time span of } L \text{ tasks}}{\text{total weighted space-time span of}}$  n facilities

For example, for a linear pipeline like the one in Figure 1 (where there is no looping inside the pipeline, so that a task will flow through each facility only once), an analytical efficiency measure can be expressed as follows (assuming the execution time of each module is time invariant):

FIGURE 2. IBM 360 Model 91 instruction sequencing illustration.

$\eta$  = efficiency of linear pipe

$$= \frac{L\left(\sum_{i=1}^{n} \alpha_{i} t_{i}\right)}{\sum_{i=1}^{n} \alpha_{i} \left(\sum_{i=1}^{n} t_{i} + (L-1) t_{i}\right)}$$

where  $t_i$  is the speed of the slowest facility (bottleneck);  $t_i$  is the speed of the *i*th facility in the pipeline;  $\alpha_i$  is the weight associated with the space-time span of the *i*th facility as determined by its importance, such as cost-speed factor; L is the number of tasks (instructions) pumped into the pipeline in a certain period of time assuming, for highest efficiency, that tasks are pumped in continuously); and  $\eta$  is the total number of facilities in the pipeline. (See Figure 2.)

In the ideal situation in which all modules have the same speed, the equation simplifies to

$$\eta = L/(n + (L-1));$$

so, when L approaches infinity (in the steady state of processing), the efficiency may approach unity. In all others cases, as L approaches infinity, the efficiency approaches

$$\eta \rightarrow \left(\sum_{i=1}^{n} \alpha_{i} t_{i}\right) / \left(\sum_{i=1}^{n} \alpha_{i}\right) t_{j} < 1.$$

Two observations should be noted at this point. First, this equation holds whether or not there are additional buffers inside the pipeline because of the linearity assumption. As is demonstrated later, buffering is an important tool for increasing throughput in many practical pipeline designs—for example, when two or more EXEC modules are available and one is a bottleneck. Second, in deriving the equation it has been assumed that a continuous supply of tasks (instructions) is available. In reality, execution may be discontinued for such reasons as precedence constraints, branching, interrupts, etc.

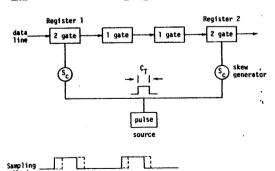

3) Clock rate and maximum speed limitations: As data and control flow from one pipe segment to another, the propagation delay through each segment and the possible signal skews have to be carefully balanced to avoid any improper gating in a high speed situation. In the maximum speed pipeline design, all segments have to be synchronized by the same clock for propagating the data through the pipe.

The study of a maximum clock rate serves to place a practical bound on the throughput achievable in a pipeline system limited by the propagation delays of the logic gates used. Several studies have been carried out to examine this problem under various assumptions of timing parameters. In all cases, three necessary conditions of signal balancing exist:

- The data must be gated by a clock wide enough to insure a properly stabilized output;

- The clock should not be too wide to allow data to pass through two or more segments within the same clock; and

- 3) The data that passes through a segment should arrive at the next segment before the next clock begins. Initially Cotten [27] tested this data rate and latching problem by using a hypothetical circuit as in Figure 3. The clock for various segments may have a skew S<sub>c</sub>, defined as the time difference between the arrival of the same pulse at different gates. The latch register is assumed to be composed of two gate levels with feedback connections. Then, under conditions 1) and 2), Cotten's clock requirements are:

$$C_T - S_c \ge 3t_{\max} - t_{\min}, \qquad (1)$$

$$C_T + S_c \leq 4t_{\min}, \qquad (2)$$

where  $C_T = \text{clock}$  width,  $S_c = \text{clock}$  skew,  $t_{\text{max}} = \text{maximum}$  single gate delay, and  $t_{\text{min}} = \text{minimum}$  single gate delay.

skew in clock sampling

FIGURE 3. Clock rate conditioning.

These two requirements can be combined to form

$$3t_{\max} - t_{\min} + S_o \le C_T \le 4t_{\min} - S_c. \quad (3)$$

Although here a segment of the pipe has been assumed to be composed of two gates, one can further the derivation by including condition 3). Then a third constraint exists as

$$C_T + C_T > 2t_{\text{max}} + T_{\text{max}} + S_c, \quad (4)$$

where  $C_T$  = inverted clock width and  $T_{\text{max}}$  = maximum propagation delay through the segment (excluding the latch).

Under Cotten's assumptions, the complete set of constraints for a general pipe segment is:

$$3t_{\max} - t_{\min} + S_c \le C_T$$

$$\le T_{\min} + 2t_{\min} - S_c \quad (5)$$

and

$$2t_{\max} + T_{\max} + S_c \le C_T + C_T.$$

(6)

Consequently the minimum clock period can be derived to be  $(C_r + C_r)$ , which satisfies the above constraint and also  $C_r + C_r \ge 2$  min  $C_r$  (that is, the period must be long enough to allow the data to propagate through a latch and then remain stable for min  $C_r$ ). Under zero skew and  $t_{\text{max}} = t_{\text{min}} = t$ ,

$$C_T + C_{\bar{T}} \geq 4t$$

.

This marks the highest frequency possible in an ideally synchronized system. If  $S_c$  is nonzero, then  $C_T + C_T \ge 4t + S_c$ , and the frequency has to be decreased.

Besides the positive clock skews, other skews may exist, such as skew between  $C_T$  and  $C_T$ . In [28], Hallin and Flynn propose another set of constraints that includes the skew, called  $\epsilon$ , and any uncertainty thereof:

$$T_D \ge 2t_M + S_c + \epsilon + U_c \tag{7}$$

$$2t_M + S_c \le C_T \le T_D + d \tag{8}$$

where  $T_D$  = propagation delay of a segment;  $t_M$  = propagation delay of a gate;  $\epsilon$  = skew between  $C_T$  and  $C_T$ ;  $U_c$  = uncertainty in the clock width; and d = minimum length pulse to change a gate output.

While Equations (7) and (8) include the additional terms of  $\epsilon$  and  $U_{\epsilon}$ , the distinctions of the minimum and maximum values of all propagation delay parameters have been ignored. Yet those distinctions are of prime importance in verifying the functioning of the circuit. One can further the derivation of the corresponding constraints, keeping conditions 1), 2), and 3) satisfied, under different sets of skews that may appear in the circuit. In any case, the (4t) period always places an absolute lower bound if a register latch is composed of two gates. If a gate delay is 2.5 nsec, the maximum frequency will be 100 megacycles, corresponding to a segment time of 10 nsec.

4) Design optimization: Design optimization for pipeline systems shares most of the fundamental difficulties of any system design. One such difficulty is to abstract a proper objective for optimization. No general objective is sufficient to describe individual situations, so individual objectives have to be formulated and solved.

One common approach is to look at the cost-effectiveness, or the cost-speed product. A given processor pipe can be segmented in various ways, resulting in different cost and speed parameters. In a synchronous pipe, such as a multiply or add pipe, a first order model of optimization may be used. The pipe is partitioned into k segments, and the resulting throughput and cost are:

segment time =

$$T/k + \lambda$$

$cost = \alpha k + \beta$

where T = time for the nonpipelined case;  $\lambda = \text{latch time}$ ;  $\alpha = \text{cost of each segment}$  (assumed to be the same); and  $\beta = \text{initial cost}$ . Thus

cost-speed product =  $(T/k + \lambda)(\alpha k + \beta)$ .

Lemma. Under the first order model, the optimal segmentation for a pipe is  $k = (\beta T/\alpha \lambda)^{\frac{1}{2}}$  (assuming a continuous space for optimization).

This result can be derived directly from minimizing the cost-speed product. It is useful for homogeneous straight-line pipes such as a pipelined adder where each segment cost and speed can fit into the characterization. For other cases, the first order model does not apply very well; then the segment speed  $f(T, k) + \lambda$  and the cost  $g(\alpha, k) + \beta$  for some discrete functions f and g specified by an alternative scheme are available. Consequently, minimizing the cost-speed product here corresponds to minimizing  $(\beta f + fg + \lambda g)$ , for which an integer programming algorithm is necessary to efficiently enumerate partially all possible schemes. An example of pipelining a processor can be found in [29].

As mentioned earlier, cost-effectiveness may not be a good objective. In some cases, the design objective is to minimize the cost while satisfying some speed constraint or vice versa. This is typically the case because the throughput of a pipe sometimes is not restricted simply by its segment speed, but also by other outside parameters such as memory speed. In other words, the local optimization has to be performed relative to the global system, leading to integer programming problems that involve semiexhaustive algorithms for optimization. For example, for a linear pipe, a dynamic programming formulation of complexity  $O(M^2N)$  is applicable where N is the number of segment nodes and M is the cost constraint. However, for systems that are not linear more complex iterative algorithms are needed.

5) Bounds on execution time and efficiency: For the purpose of establishing some upper bounds of a pipe in executing certain typical but related set of operations, the following theoretical model can be used. Here a pipe is characterized by the number of segments it contains, where each segment has the same synchronized speed.

Ideally, when the work to be accomplished has no internal precedence constraints, the maximum throughput can be attained with one output per segment clock. The existence of precedence requirements inhibits the continuous initiation of the pipe, resulting in lower throughput. The most common type of precedence structure is that of a tree.

One special problem of interest is: Given a pipe of m segments, what is the time bound needed to compute the sum (or product) of n numbers, assuming that each segment time is 1 unit? If  $n \geq 2m$  and is a power of 2, the pipe is kept busy until

(m-1) computations are left, with the needed (intermediate) results residing in the m segments. They will take an additional  $(m \log_2 m + m - 1)$  units to complete. So altogether, the (n-1) computations take  $(n + m \log_2 m - 1)$  units. On the other hand, if  $2 \le n \le 2m$ ,  $(n/2 + m \log_2 n - 1)$ units are required. The corresponding efficiencies, defined by the ratio of the total busy segment times to the total segment time span, can then be derived easily as  $(n-1)/((n-1)+m\log_2 m)$  and (n-1)/(n-1) $(m/2 + m \log_2 m - 1)$ , respectively. This implies that for  $n \gg m$  the pipe of m segments functions almost like a nonpiped processor with speed of one segment time instead of m segment cycles (the total time is O(n), not O(mn). However, for smaller n the time is  $O(m \log_2 n)$ .

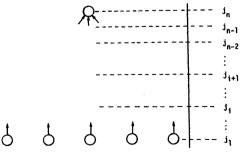

The previous special case assmues a set of uniform operations on a set of data, merging them into one result where the exact order of merging is unimportant. In the case where a specific tree is to be followed (the precedence structure is fixed), other lower bounds can be derived in a similar fashion. It can be shown that, for a general tree (not necessarily binary), if each node i is labeled by  $\ell(i)$  corresponding to its distance from the root, then execution of the nodes according to priorities in descending order of  $\ell(i)$  in a pipeline environment with identical pipeline characteristics is optimal. Therefore the shortest execution time can be achieved if the nodes are executed according to priorities corresponding to their level labels. However, if the pipes have different structures and/or capabilities, the problem becomes NP-complete. Without going into the latter case, the time bound for the former case can be derived, given a tree structure and a pipe structure (latency and flush time).

First let  $L_j$  be the number of nodes of the tree with label j where  $l \geq j \geq 0$ . For the simple case that there exists a  $J_0$  such that for  $\ell \geq j > j_0$ ,  $L_j \geq m$  and for  $j \leq j_0$ ,  $L_j \leq m$ , the time bound is given by

$$\sum_{j=l}^{j_0+1} L_j + m(j_0+1) - 1,$$

and this time bound is exact (from the optimality of the level algorithm). This

asserts that once the "critical level"  $j_0$  is reached, the rest of the tree of  $j_0$  levels needs precisely  $m(j_0 + 1) - 1$  to flush. So the time complexity is  $O(mj_0)$  if the former term is less significant.

Generalization of the simple case will lead to a more complex bound. One way to derive the bound is to chop  $L_j$ 's into pairs of sections, each of which corresponds to a simple case as depicted in Figure 4. Then if  $L_j$  is the number of nodes left at level j when all nodes at level j first become either ready or initiated (since some may have already been computed or initiated), the bound is

$$\sum_{i=1}^{u} \left[ \sum_{j=j_{i-1}}^{j_i} L_{j}' + m(j_i - j_{i+1}) \right] + m - 1.$$

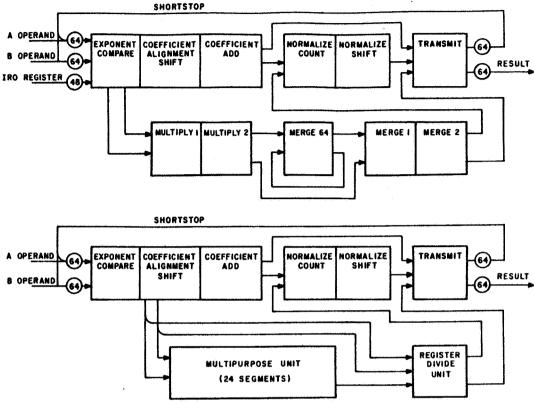

In deriving these bounds, it has been assumed that each node takes the same processing structure and has the same flush time. On the other hand, if more than one pipe exists, the bounds are much more complicated. First, the control of multiple pipelines, specifically the routing of intermediate results, is a practically unsolved problem. While the short-circuit (shortstop) path exists from the output of a pipe to its own input, the disjoint and direct update paths between pipes either incur too much cost or cause too much interference. Aside from this practical restriction, theoretically, with multiple pipes, similar time bounds are derivable. In the case of computing the sum or product of n numbers in a system with p pipes, assume  $n = p\ell$  for some  $\ell$ . If  $\ell \geq 2m$  (integer powers of 2), then the time bound is  $[\ell + m (\log_2 m)]$  $+ \log_2 \ell$  - 1]. If  $\ell \leq 2m$ , it is  $\lfloor \ell/2 \rfloor + 2m$  $m (\log_2 n + \log_2 \ell) - 1].$

FIGURE 4. Partitioning into simple cases.