# **Transputer**

## Occam and the Transputer

The following paper was presented in March 1984 at the IFIP working group 10.3 workshop on the Hardware Implementation of Concurrent Languages and Distributed Systems, and will be published by North-Holland in the workshop proceedings.

David May

27 June 1984

#### OCCAM AND THE TRANSPUTER

David May and Roger Shepherd

INMOS Limited

Whitefriars

Lewins Mead

Bristol, BS1 2NP

England

The transputer is a programmable VLSI device with communication links for point-to-point connection to other transputers. Occam (\*) is a language which enables a transputer system to be described as a collection of processes which operate concurrently and communicate via named channels. This paper describes how the transputer provides an efficient implementation of concurrency and message passing in a distributed system.

#### 1 Introduction

The transputer is a programmable VLSI device. It provides a 'building block' for high-performance concurrent systems in the same way as the logic gate provides a 'building block' for today's electronic systems. Occam is a language which simplifies the design of transputer systems just as boolean algebra simplifies the design of systems built from logic gates.

An important design objective of occam and the transputer was to provide the same concurrent programming techniques both for a single transputer and for a network of transputers. Consequently, the features of occam were carefully chosen to ensure an efficient distributed implementation on transputer systems and then the concurrent processing mechanisms within the transputer were designed to match.

The result is that a program ultimately intended for a network of transputers can be compiled and executed efficiently by a single computer used for program development. Once the logical behaviour of the program has been verified, the program may be configured for execution by a single transputer (low cost), or for execution by a network of transputer (high performance).

This paper describes the main properties of the transputer and discusses the influence of occam on its design. A brief summary of the relevant aspects of occam is included (see [1] for more details, and [3] for an introduction to occam).

<sup>(\*)</sup> Occam is a trademark of the INMOS Group of Companies

#### 2 Transputer systems

The transputer contains memory, a processor and a number of communication links which allow direct connection to other transputers [2]. A system is constructed from a collection of transputers which operate concurrently and communicate through links. Such a system can be programmed in occam, a language which enables a system to be described as a collection of processes operating concurrently and communicating through named channels [3].

#### 2.1 Point-to-point communications

One of the most significant aspects of the transputer view of system design is the use of point-to-point communication links to connect processing elements, each of which has its own local memory. This choice has many advantages; in particular, it enables arbitrarily large systems to be constructed using local processing and local communication. Furthermore, point-to-point communication links are easy to use and can be efficiently implemented.

However, the choice of local processing and communication necessitates a significant change in programming concepts and new algorithms need to be developed [4]. Most existing languages assume the existence of a global communication system (implicit in the presence of a uniformly accessable address space). Such communication systems (such as buses) suffer from the disadvantage that their speed reduces as their size increases. A consequence is that existing languages are not suitable for distributed concurrent processing, and this alone gives rise to the need for a new language.

#### 2.2 Simulated and Real concurrency

Existing concurrent languages have been designed to provide simulated concurrency. This is not surprising, since until recently it has not been economically feasible to build systems with a lot of real concurrency.

Unfortunately, almost any system can be simulated by a sequential computer. There is, therefore, no guarantee that a language designed for simulated concurrency will be relevant to the needs of systems with real concurrency. The choice of features in such languages has been motivated largely by the need to share one computer between many independent tasks. In contrast, the choice of features in cccam has been motivated by the need to use many communicating computers to perform one single task.

#### 3 Occam

Occam enables a system to be described as a collection of concurrent processes, which communicate with each other and with peripheral devices through channels. Occam programs are built from three primitive processes:

| $\mathbf{v}$ | : = | = e | assign | expi | ression | e | to | variable v |   |

|--------------|-----|-----|--------|------|---------|---|----|------------|---|

| C            | 1   | е   | output | expi | ession  | е | to | channel c  |   |

| C            | ?   | V   | input  | from | channel |   | to | variable v | , |

The primitive processes are combined to form constructs:

SEQuential components executed one after another PARallel components executed together ALTernative component first ready is executed

A construct is itself a process, and may be used as a component of another construct.

Conventional sequential programs can be expressed with variables and assignments, combined in sequential constructs. IF and WHILE constructs are also provided.

Concurrent programs can be expressed with channels, inputs and outputs, which are combined in parallel and alternative constructs.

Each occam channel provides a communication path between two concurrent processes. Communication is synchronized and takes place when both the inputting process and the outputting process are ready. The data to be output is then copied from the outputting process to the inputting process, and both processes continue.

An alternative process may be ready for input from any one of a number of channels. In this case, the input is taken from the channel which is first used for output by another process.

The benefits of point-to-point communication have already been mentioned above. The choice of synchronized communication simplifies programming as it prevents the loss of data. The choice of unbuffered communication removes the need for any store to be associated with the channel. Copying data from the outputting process to the inputting process is clearly essential for communication between transputers, and has significant additional performance advantages. It is easy to make copying within a machine fast by use of microcode.

#### 4 The transputer

A transputer system consists of a number of interconnected transputers, each executing an occam process and communicating with other transputers. As a process executing on a transputer may itself-consist of a number of concurrent processes the transputer has to support the occam programming model internally. Within a transputer concurrent processing is implemented by sharing processor time between the concurrent processes.

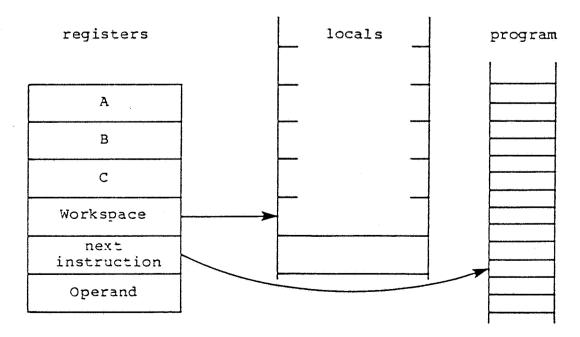

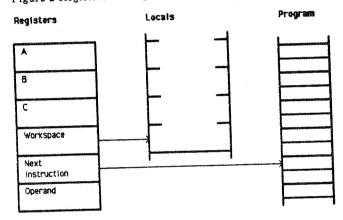

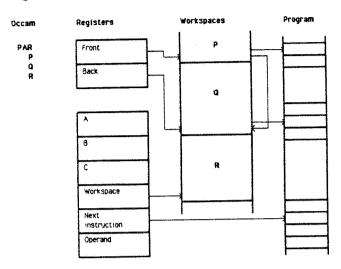

#### 4.1 Registers

The design of the transputer processor exploits the availability of fast on-chip memory by having only a small number of registers; six registers are used in the execution of a sequential process. The small number of registers, together with the simplicity of the instruction set, enables the processor to have relatively simple (and fast) data paths and control logic.

#### The six registers are:

The workspace pointer which points to an area of store where local variables are kept.

The instruction pointer which points to the next instruction to be executed.

The operand register which is used in the formation of instruction operands.

The A, B and C registers which form an evaluation stack, and are the sources and destinations for most arithmetic and logical operations. Loading a value into the stack pushes B into C, and A into B, before loading A. Storing a value from A, pops B into A and C into B.

Expressions are evaluated on the evaluation stack, and instructions refer to the stack implicitly. For example, the 'add' instruction adds the top two values in the stack and places the result on the top of the stack. The use of a stack removes the need for instructions to respecify the location of their operands. Statistics gathered from a large number of programs show that three registers provide the optimum balance between code compactness and implementation complexity.

#### 4.2 Instructions

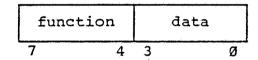

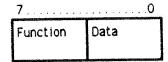

It was a design decision that the transputer should be programmed in a high level language. The instruction set has, therefore, been designed for simple and efficient compilation, and to support the occam process model. It contains a relatively small number of instructions, all with the same format, chosen to give a compact representation of the operations most frequently occurring in programs. Each instruction is one byte long, and is divided into two 4 bit parts. The four most significant bits of the byte are a function code, and the four least significant bits are a data value.

#### 4.2.1 Direct functions

The representation provides for sixteen functions, each with a data value ranging from Ø to 15. Thirteen of these are used to encode the most important functions performed by any computer. These include:

load constant

add constant

load local

store local

load local pointer

load non local

store non local

jump

conditional jump

call

The most common operations in a program are the loading of small literal values, and the loading and storing of one of a small number of variables. The 'load constant' instruction enables values between Ø and 15 to be loaded with a single byte instruction. The 'load local' and 'store local' instructions access locations in memory relative to the workspace pointer. The first 16 locations can be accessed using a single byte instruction.

The 'load non local' and 'store non local' instructions behave similarly, except that they access locations in memory relative to the A register. Compact sequences of these instructions allow efficient access to data structures, and provide for simple implementations of the static links or displays used in the implementation of block structured programming languages.

#### 4.2.2 Prefixing functions

Two more of the function codes are used to allow the operand of any instruction to be extended in length. These are:

prefix

negative prefix

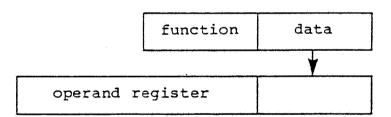

All instructions are executed by loading the four data bits into the least significant four bits of the operand register, which is then used as the the instruction's operand. All instructions except the prefixing instructions end by clearing the operand register, ready for the next instruction.

The 'prefix' instruction loads its four data bits into the operand register, and then shifts the operand register up four places. The 'negative prefix' instruction is similar, except that it complements the operand register before shifting it up. Consequently operands can be extended to any length up to the length of the operand register by a sequence of prefixing instructions. In particular, operands in the range -256 to 255 can be represented using one prefixing instruction.

The use of prefixing instructions has certain beneficial consequences. Firstly, they are decoded and executed in the same way as every other instruction, which simplifies and speeds instruction decoding. Secondly, they simplify language compilation, by providing a completely uniform way of allowing any instruction to take an operand of any size. Thirdly, they allow operands to be represented in a form which is independent of the processor wordlength.

#### 4.2.3 Indirect functions

The remaining function code, 'operate', causes its operand to be interpreted as an operation on the values held in the evaluation stack. This allows up to 16 such operations to be encoded in a single byte instruction. However, the prefixing instructions can be used to extend the operand of an 'operate' instruction just like any other. This allows the number of operations in the machine to be extended indefinitely.

The encoding of the indirect functions is chosen so that the most frequently occuring operations are represented without the use of a prefixing instruction. These include arithmetic and comparison operations such as

add greater than

Less frequently occurring operations have encodings which require a single prefixing operation (the transputer instruction set is not large enough to require more than 512 operations to be encoded!).

#### 4.2.4 Word length independence

A program which manipulates bytes, words and truth values can be translated into an instruction sequence which behaves identically whatever the wordlength of the processor executing it (apart from overflow conditions resulting from word length dependencies). This results from the fact that the instruction size is independent of wordlength, the method of representing long operands as a sequence of prefixing instructions, and the memory addressing structure.

A byte in memory is identified by a single word value called a pointer. A pointer consists of two parts: a word address and a byte selector. The byte selector contains as many bits as are needed to identify a single byte within a word and occupies the least significant bits of the pointer. For example, in a 24 bit transputer the word address would occupy the 22 most significant bits and the byte selector the 2 least significant bits.

Special instructions, such as 'load local pointer' and 'word subscript', are provided to construct and manipulate pointers. Pointer values are treated as signed integers. This enables the standard comparison functions to be used on pointer values in the same way that they are used on numerical values.

#### 4.2.5 Efficiency of encoding

Measurements show that about 80% of executed instructions are encoded in a single byte (ie without the use of prefixing instructions). Many of these instructions, such as 'load constant', and 'add' require just one processor cycle.

The instruction representation gives a more compact representation of high level language programs than more conventional instruction sets. Since a program requires less store to represent it, less of the memory bandwidth is taken up with fetching instructions.

Short instructions also improve the effectiveness of instruction prefetch, which in turn improves processor performance. As memory is word accessed, a 32 bit transputer will receive four instructions for every fetch. There are two words of prefetch buffer so that the processor rarely has to wait for an instruction fetch before proceeding. Since the buffer is short, there is little time penalty when a jump instruction causes the buffer contents to be refilled.

#### 4.2.6 Example

The following example illustrates the use of the instruction set for sequential programming. The variables v, w, and x are assumed to be in the first sixteen locations of local workspace. The compiler has allocated a local workspace location, here called StaticLink, to hold the address of the outer level workspace containing the variable y.

occam

$$x := (v + w) - (y + #24)$$

instruction sequence

load local v

load local w

operate add

load local StaticLink

load non local y

prefix 2

add constant 4

operate subtract

store local x

This requires a total of 9 bytes.

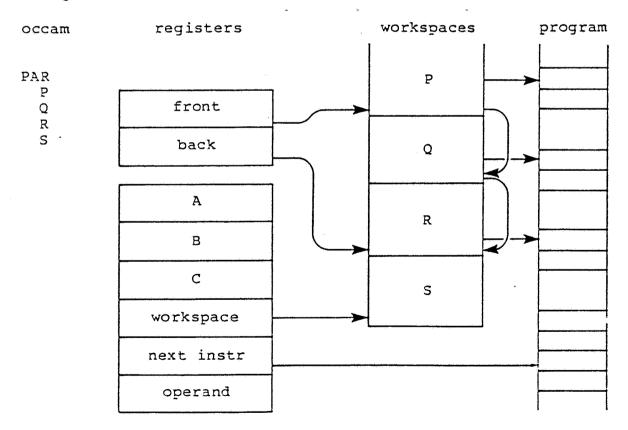

#### 4.3 Support for concurrency

The processor provides efficient support for the occam model of concurrency and communication. It has a microcoded scheduler which enables any number of concurrent processes to be executed together, sharing the processor time. This removes the need for a software kernel. The processor does not need to support the dynamic allocation of storage as the occam compiler is able to perform the allocation of space to concurrent processes.

At any time, a concurrent process may be

active - being executed

- on a list awaiting execution

inactive - ready to input

ready to output

- waiting until a specified time

The active processes waiting to be executed are held on a list. This is a linked list of process workspaces, implemented using two registers, one of which points to the first process on the list, the other to the last.

In this illustration, S is executing, and P, Q, and R are active, awaiting execution.

A process is executed until it is unable to proceed because it is waiting to input or output, or waiting for the timer. Whenever a process is unable to proceed, its instruction pointer is saved in its workspace and the next process is taken from the list. Actual process switch times are very small as little state needs to be saved; it is not necessary to save the evaluation stack on rescheduling.

The processor provides a number of special operations to support the process model. These include

start process end process

When a parallel construct is executed, 'start process' instructions are used to create the necessary concurrent processes. A 'start process' instruction creates a new process by adding a new workspace to the end of the scheduling list, enabling the new concurrent process to be executed together with the ones already being executed.

The correct termination of a parallel construct is assured by use of the 'end process' instruction. This uses a workspace location as a counter of the components of the parallel construct which have still to terminate. When the components have all terminated, the counter reaches zero, and a specified process can then proceed.

#### 4.4 Communications

Communication between processes is achieved by means of channels. A channel between two processes executing on the same transputer is implemented by a single word in memory; a channel between processes executing on different transputers is implemented by point-to-point links. The processor provides a number of operations to support message passing, the most important being

input message

output message

The 'input message' and 'output message' instructions use the address of the channel to determine whether the channel is internal or external. This means that the same instruction sequence can be used for both internal and external channels, allowing a process to be written and compiled without knowledge of where its channels are connected.

As in the occam model, communication takes place when both the inputting and outputting processes are ready. Consequently, the process which first becomes ready must wait until the second one is also ready.

A process performs an input or an output by loading the evaluation stack with a pointer to a message, the identity of the channel, and the count of the number of bytes to be transferred, and then executing an 'input message' or an 'output message' instruction as appropriate.

#### 4.4.1 Message passing on an internal channel

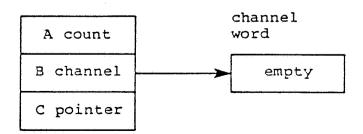

A program initializes an internal channel when it is declared. It does this by writing the value 'empty' to the channel. The value 'empty' is chosen so as not to correspond with the identity of any process.

When a process communicates using an internal channel the message passing instruction examines the contents of the channel.

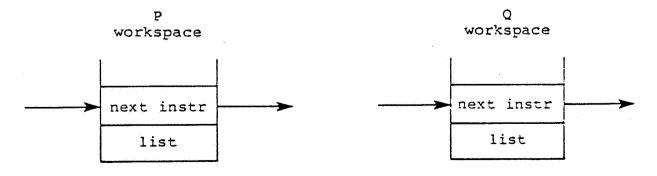

In this example, the process P is about to execute an input or output message instruction on an initialized channel.

P executing registers

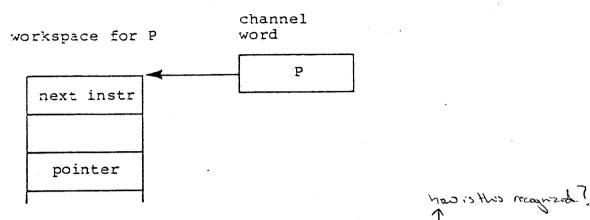

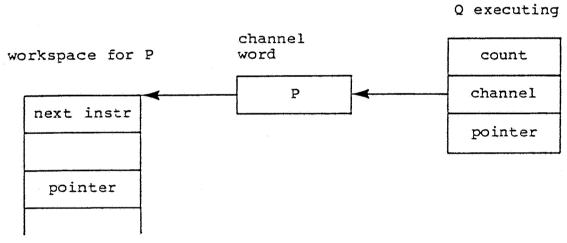

If the channel contains 'empty', then this is the first process to become ready to communicate via this channel. The identity of the process is stored in the channel, and the message pointer stored (with the instruction pointer etc) in the workspace. The processor then starts to execute the next process from the scheduling list.

If the channel contains the identity of a process, then this is the second process to become ready to communicate via this channel.

The message is copied, the first process is added to the active process list, and the channel is reset to the 'empty' state. It does not matter whether the inputting or the outputting process becomes ready first.

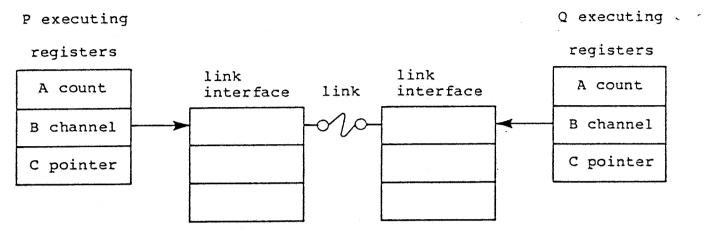

### 4.4.2 Message passing with point to point links

When a message is passed via an external channel the processor delegates to an autonomous link interface the job of transferring the message and deschedules the process. When the message has been transferred the link interface causes the processor to reschedule the waiting process. This allows the processor to continue the execution of other processes whilst the external message transfer is taking place.

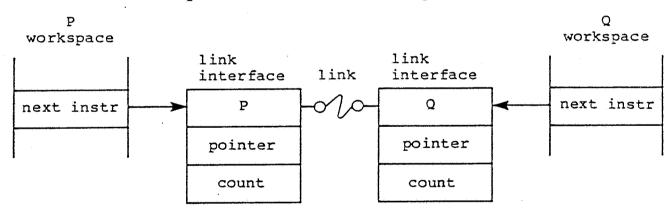

The following diagrams show the sequence of operations when two processes, executing on separate transputers, communicate using a link connecting the two transputers.

Each link interface uses three registers to hold the following information

- a pointer to the workspace of the process

- a pointer to the message

- a count of bytes to be transferred

When the 'input message' or 'output message' instruction is executed, these registers are initialized, and the instruction pointer is stored in the process workspace. The processor then executes the next process on the scheduling list.

When both link interfaces have been initialized, the message is copied. Each link interface then adds the respective process to the end of the corresponding processor's active list.

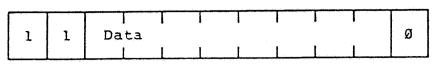

•

Data byte

Acknowledge

Data bytes and acknowledges are multiplexed down each signal line.

An acknowledge is transmitted as soon as reception of a data byte starts (if there is room to buffer another one). Consequently transmission may be continuous, with no delays between data bytes.

#### 5 Conclusion

By taking an integrated approach to the design of a VLSI computer and a concurrent programming language it is possible to produce a new level of system 'building block' and the corresponding design formalism.

In particular, it is possible to support the use of the same concurrent programming techniques both within a single transputer and for a network of transputers. The concurrent processing features of a general purpose programming language can be efficiently implemented by a small, simple and fast processor.

#### 6 References

- [1] INMOS Limited, Occam Programming Manual (Prentice-Hall International, London, 1984).

- [2] Barron, I.M. et al., The Transputer, Electronics, 17 November 1983, p 109.

- [3] May, M.D., OCCAM, ACM SIGPLAN Notices vol 18-4 (Apr 1983) pp69-79.

- [4] May, M.D. and Taylor, R.J.B., OCCAM, Microprocessors and Microsystems vol 8-2 (Mar/Apr 1984)

## Tiny:

## An Efficient Routing Harness for the INMOS Transputer

Lyndon Clarke (exploration and routing)

Greg Wilson (monitoring and documentation)

February 8, 1990

#### Abstract

Message-based MIMD computers that support arbitrary connections over a small number of communications links cannot support parallel applications with complex communication patterns unless the support software includes message routing. This paper describes design issues for such software, a router for the Inmos T800 transputer called Tiny as an example. Performance figures show that Tiny achieves near optimal routing performance given the hardware limits. Modifications to Tiny to monitor message traffic are also described.

#### 1 Introduction

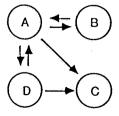

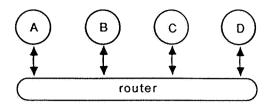

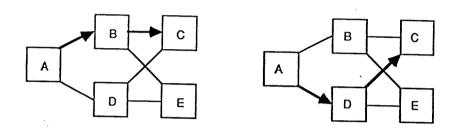

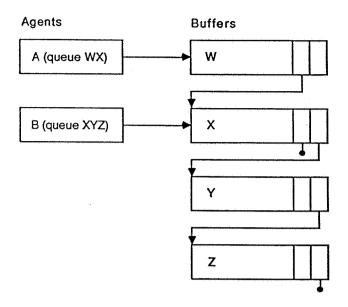

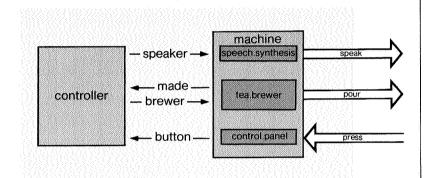

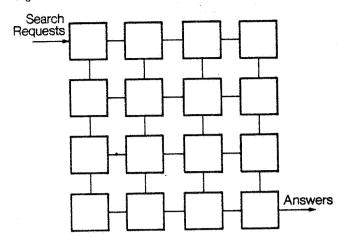

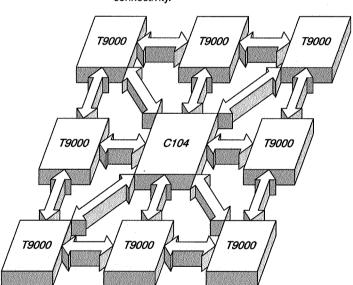

In order to realize the potential of an MIMD computer for complex parallel applications, it must be possible to send messages efficiently and reliably between arbitrary processors. One popular model for such applications is Communicating Sequential Processes (CSP), developed by Hoare [HOAR] and embodied in the occam language [OCC2]. Named channels connect processes pairwise (Figure 1). This approach forces synchronization at the time of communication: message data moves through the channel from process A to process B only when A is ready to send and B ready to receive. When not communicating, processes proceed independently.

Our experience shows that CSP is a difficult paradigm within which to develop large applications. Programmers usually want messages sent to a destination, but occam forces them to specify sending messages through a channel. If a message's destination is not on the same processor as its sender (which it usually is not), then message-passing processes must be created, along with multiplexers and demultiplexers, to accommodate low connectivity between processors. It is tedious to plumb such processes together properly, and difficult to trace the plumbing in someone else's program. In practice, programming in the CSP paradigm is like programming in assembly

Figure 1: The CSP Model of Concurrency

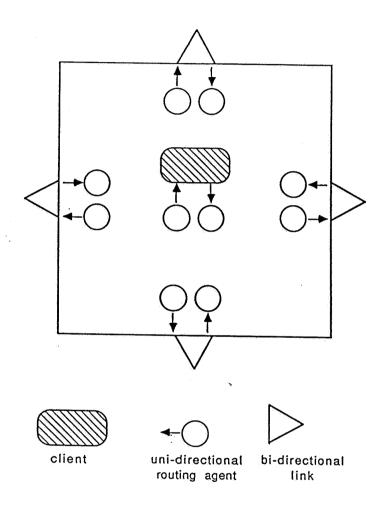

Figure 2: A More Useful Model of Concurrency

language; instead of tracing GOTOs, programmers spend a great deal of time asking, "Where does this message go to?"

The occam implementation of CSP on the transputer is also inefficient. The paradigm's insistence on the independence of processes means that when a message travels between two processes on a single processor its data must be copied from one part of memory to another. Programs which contain multiplexers and FIFO buffers to decouple applications processes may have to copy a message several times before it arrives at its destination, which inevitably degrades performance.

A more comfortable paradigm is one which allows (possibly asynchronous) communication between any two named processes. In this paradigm, A sends a message to B by giving the message to a router; A is then free to carry on calculating. When process B wants to receive a message it blocks until the router has one for it.

This paradigm is the one actually used in applications containing any but the simplest parallelism, even if only the first paradigm is directly available. Programmers build FIFOs and multiplexers to provide the illusion of global, asynchronous connectivity so frequently that it is worth doing it once, properly, to provide a package to applications programmers.

This was the motivation behind Tiny [CLA1] and TITCH (Tiny's immediate predecessor, now retired). To users, Tiny is a kernel running on each processor, connected to one or more clients by channels (Figure 2). Each process in the network has a unique user-assigned client identifier (CID). To send a message to process P the sender specifies P's CID, the buffer containing the data, the amount of data, and the channel through which that buffer is passed to the router (see Section 4.1). To receive a message, P specifies which channel it is listening to, and where the incoming data should be placed. Everything else is Tiny's responsibility.

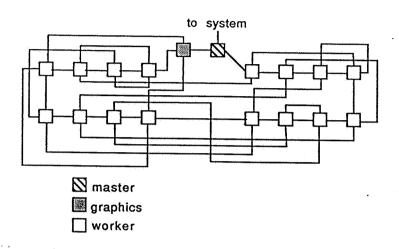

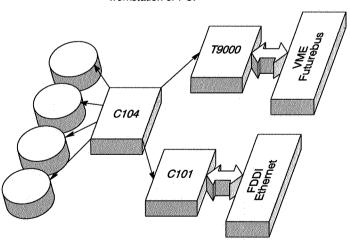

An essential feature of a general-purpose router is that it should be able to run on any topology, so that users can connect processors to suit their applications. Much of Tiny is therefore devoted to exploring the network and building up routing tables recording the shortest paths from each processor to each other. This allows applications to use randomly-connected graphs, in which mean and maximum inter-node distance and worst link loading increase only as log(n) [PRNC]. How networks are explored and routing tables built up is described in [CLA3].

Another important feature of Tiny is its efficiency. Most users of massively parallel computers are primarily interested in performance. If routers must reside on the chip, users therefore want them not only to deliver messages quickly, but also to steal as few CPU cycles from the application as possible. As Section 6 discusses, the performance of Tiny is very close to hardware limits.

#### Acknowledgements

Tiny was developed by Lyndon Clarke during Ph.D. research in the Department of Physics at the University of Edinburgh supported by the Science and Engineering Research Council. It has since become an important part of the Club Domain software of the Edinburgh Concurrent Supercomputer Project (ECSP). The amendments made to Tiny to monitor its internals were

made by Greg Wilson while he was supported by Meiko Limited, and as part of his Ph.D. research in the Department of Computer Science at the University of Edinburgh. We would like to thank Roy Campbell for his many helpful comments.

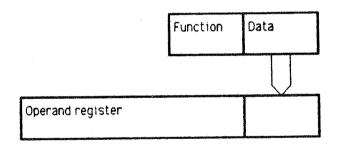

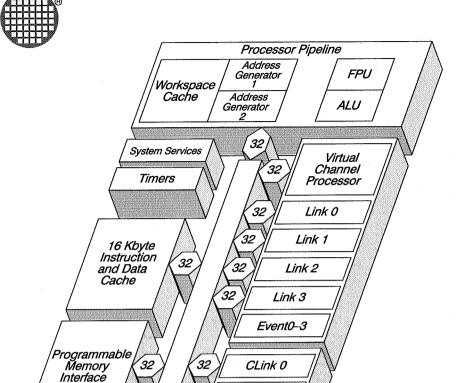

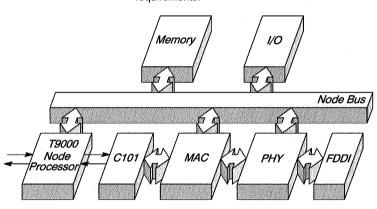

## 2 The INMOS T800 Transputer

The INMOS transputer [T800] was designed for use in both real-time control applications and multiprocessor computers. Each transputer contains a CPU, four kilobytes of on-chip memory, and four high-speed communications links, each with its own DMA controller. The T800 transputer also contains a 1 MFLOP floating-point unit.

The transputer was designed to run concurrent processes efficiently. It automatically maintains one queue each for low-priority and high-priority processes. Low-priority processes are timesliced automatically; when one is interrupted, it is placed at the tail of the low-priority queue and the next one scheduled. High-priority processes are not timesliced, and cannot be interrupted, even by other high-priority processes. A high-priority process runs until it deschedules itself or is blocked by an i/o operation.<sup>1</sup>

The transputer's CPU contains only three general-purpose registers, called Areg, Breg, and Creg, arranged as a stack. All instructions implicitly manipulate particular registers — for example, the instruction stnl (store non-local) stores the contents of Breg in the location pointed to by Areg, popping both values.

The transputer also contains a workspace pointer register called Wptr. This holds the base address of the active process's workspace. All local variable accesses are offset relative to Wptr; an instruction to load the value at address 5, for example, actually loads the value at (Wptr+5). When a low-priority process is descheduled the values of Wptr and the instruction pointer Iptr are saved, but the contents of the register stack are not. Descheduling can only take place after certain instructions, so care must be taken to ensure that nothing valuable is on the stack at such times.

The instructions in and out are of particular interest in the design of routing software. These are used to implement both internal and external communications. in interprets Creg as the address of a data block, Breg as the address of a communications channel, and Areg as a byte count. When in is executed to carry out internal communications, the transputer checks the value pointed to by Breg. If this contains mint (the least integer the transputer can represent), then the other process taking part in the communication has not yet rendezvoused. The process doing the in puts its workspace pointer in the channel word and stores the base address of the data to be transferred in a reserved location in its workspace. When the other process involved executes an out, it finds a valid address in the channel word, so it copies its data into the first process's workspace and reschedules that process. (If the sending process reaches the communication first, the reciprocal steps are carried out.)

External communication is done in much the same way. In this case, however, the values in the register stack are given to the controller responsible for the link over which the communication is taking place. When both of the link controllers involved have been given their orders, they arrange for data to be transferred without further CPU intervention, re-scheduling the communicating processes when the transfer completes. While external communication is slower than internal communication (since link bandwidth is lower than memory bandwidth), it retards other CPU activities only slightly by stealing memory cycles for DMA.

One final important feature of the transputer is the way its hardware implements choice in communications. The occam ALT construct takes pairs of channels and Boolean guards and accepts

<sup>&</sup>lt;sup>1</sup>Two other queues are maintained, one each for processes of each priority level waiting on clock interrupts. This "wait until" feature is exploited by the monitor described in Section 7.

a single communication on a channel whose guard is TRUE, then executes the code nested below that communication. For example:

```

ALT

time > startTime & connection[0] ? newTime

process(newTime)

time < stopTime & connection[1] ? newTime

process(newTime)

TRUE & interrupt ? any

stop := TRUE</pre>

```

will accept an integer newTime on element 0 of the channel array connection if time is greater than startTime, or on element 1 of connection if time is less than stopTime, or any value on interrupt.

To implement ALT, the transputer evaluates each Boolean guard and initializes each channel. When one of the branches is triggered, the transputer goes through these operations again to disable each channel, so that if several processes tried to rendezvous with the ALTing process, only one will succeed.

It is important to note that the servicing of ALT branches is arbitrary, not random. If several branches are ready, the transputer will choose one of them; if, when the same piece of code is next executed, the same branches are ready again, the transputer will choose the same branch. This has an important effect on the efficiency and correctness of CSP-style routers, as is discussed in the next section.

## 3 Router Design

The most important constraint on the design of a processor-resident router like the one in Figure 2 is the low number of inter-processor connections. Since these connections are the "narrowest" points in the system, i.e. the ones with the least bandwidth, each link controller should be given its own pair of processes (one each for input and output) so that external communications can be externally driven. Each client process should similarly be connected to the router through its own input and output handlers, to decouple the interface procedures from the underlying router. These various output handlers should be sufficiently buffered with FIFO queues to avoid the head-of-line blocking problem [HLUC], in which throughput is limited because messages which could be routed to idle output points are hidden behind messages which cannot currently be routed.

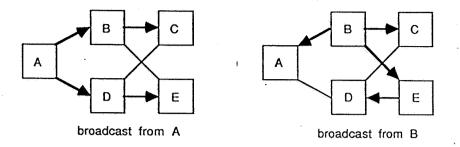

This leads to the process structure shown in Figure 3. Each routing process is either a multiplexer or a demultiplexer, and is referred to as an agent. In Tiny, the routing logic which decides where to send messages lies in the demultiplexing agents.

In order to maximize the performance of a computer in which message routing and computation compete for CPU cycles, each processor must act as if through-routing messages were more important than doing the user's calculations. (To understand this, consider what would happen if processor  $P_1$  gave higher priority to its own work than it did to routing messages to other processors. In this case, N-1 of the computer's N processors could be waiting for new tasks while only one of its processors was doing useful work.) This means that the router's processes must run at high priority, while the application processes run at low priority. However, since high priority processes on the transputer cannot be interrupted, the router must contain mechanisms to deschedule its agents explicitly. The transputer provides such mechanisms naturally by descheduling even high-priority processes when they attempt to communicate with an unready partner. Another more explicit method used by Tiny is described in Section 5.3.

Figure 3: Structure of Processes in a Router

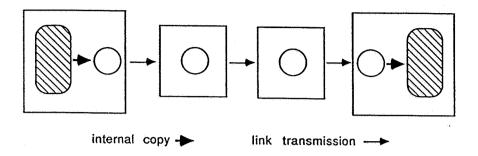

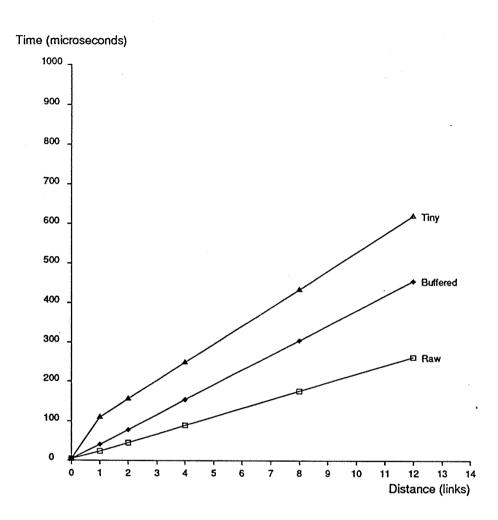

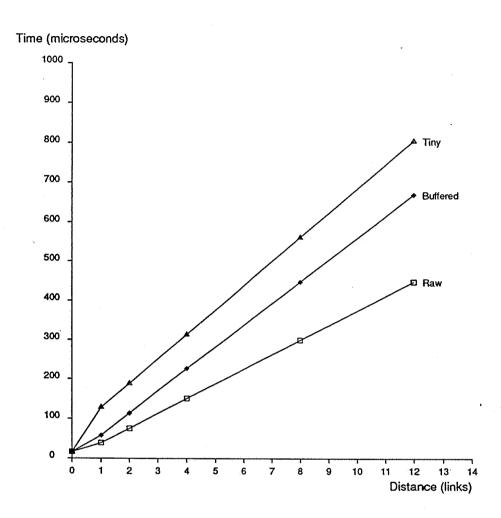

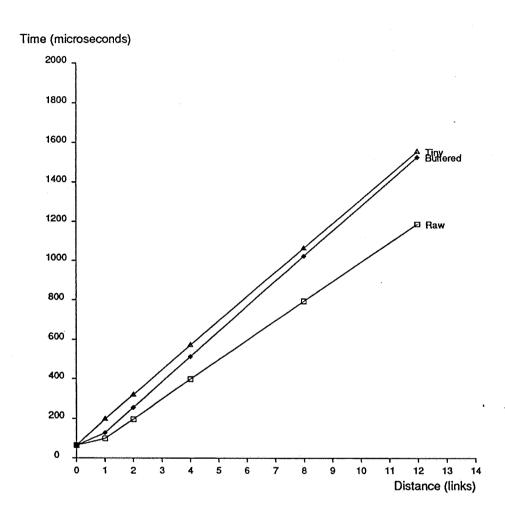

Figure 4: Time Taken to Copy a Message

## 3.1 Improving on CSP Routers

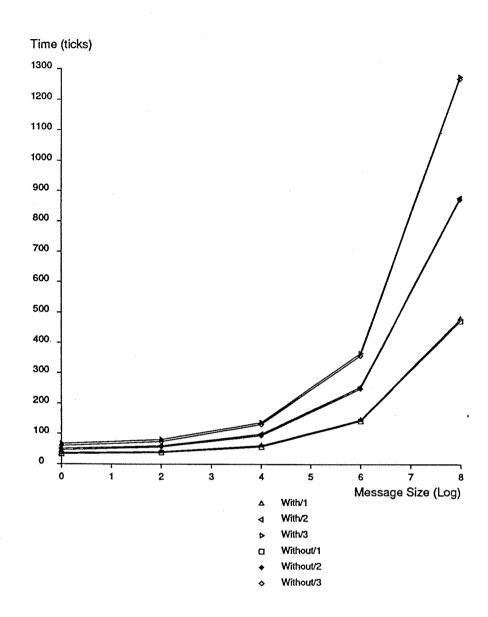

Tiny differs from pure CSP routers by avoiding the overheads of data copying that occur when the in and out instructions are used between agents on a single processor. The entire message is copied each time these instructions are used. If messages are large or frequent, this copying could consume the majority of the processor's time. Even ignoring the copying they initiate, in out are very expensive — the instructions Tiny uses instead (described in Section 5.3) consume a similar number of cycles, but perform much more useful work.

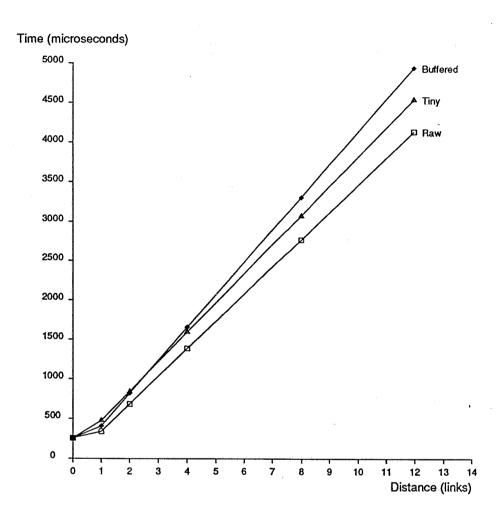

Instead of copying data, Tiny's agents pass pointers to buffers.<sup>2</sup> The total time spent copying each message is therefore only  $M(2t_C + Lt_L)$ , where M is the message size in bytes, L is the number of links the message passes through,  $t_C$  is the time to copy a single byte to or from a process's workspace, and  $t_L$  is the time to send a byte down a link (Figure 4). This overhead could be further reduced by eliminating  $t_C$ , and allowing user processes to manipulate buffer pointers directly. For the reasons given in Section 8, such a scheme is practical.

Another difference between pure CSP routers and Tiny is the elimination of ALTs to ensure both fairness and greater speed. Consider the occam procedure given by:

PROC mux( CHAN OF ANY input, CHAN OF ANY output, [] INT buffer)

```

INT buffer.size :

WHILE TRUE

ALT i = 0 FOR (SIZE input)

input[i] ? buffer.size; buffer

output ! buffer.size; buffer

```

This multiplexer repeatedly accepts input on any of its array of input channels, then outputs the message received. The problem is that in a transputer this multiplexer will always choose the same input channel if all channels are always ready. A better multiplexer is:

PROC fair.mux( CHAN OF ANY input, CHAN OF ANY output, [] INT buffer)

<sup>&</sup>lt;sup>2</sup>A way of doing this in occam is outlined in [WILS].

```

INT buffer.size, client :

WHILE TRUE

ALT i = client FOR (SIZE input)

VAL chan.id IS (client \ (SIZE input)) :

input[chan.id] ? buffer.size; buffer

SEQ

output ! buffer.size; buffer

client := chan.id + 1

```

(The backslash \ is occam's remainder operator, while (SIZE input) gives the dimension of the channel array being multiplexed.) This multiplexer repeatedly re-orders its inputs so that any order-dependent favouritism is eliminated, and looks suspiciously like a queue with multiple inputs. Each client puts buffers into the queue (which in this case only has depth 1), and the multiplexor removes them in order of their arrival. The ALT-less implementation of multiple-input queues described below not only speeds up the multiplexor, it also makes the multiplexor's behaviour independent of its number of inputs.<sup>3</sup>

## 4 Internal Structure

Tiny is made up of several interacting agents on each processor. Each handles the input or output half of a link, or a single input or output channel connecting Tiny to a client. Each agent's workspace, or A-page, contains space for certain transputer instructions and an agent handle used directly by Tiny.

Agents manipulate buffers, represented by B-pages which contain routing and ownership information and a pointer to the message's data. As with A-pages, the part of a B-page manipulated directly by Tiny is called its handle.

#### 4.1 Message Typing

Just as programmers assign types to variables within processes, in Tiny they may type messages by sending them on different channels. For example, in a simple grid decomposition in which processes repeatedly swap boundary conditions, each process receives two messages containing new boundary values during each iteration. If the process is connected to the router by a single channel, it must read the message, decide which boundary the data is for, and then copy the data into that boundary. If the channels connecting the process to the router have types left-bound and right-bound, the process can know a priori where the message data belongs. This makes for more efficient programs (less internal copying is required) and more efficient programming (message typing provides structure, which reduces programming errors).

Multi-channel interfaces are only slightly more complicated to implement than single-channel interfaces. The agents handling traffic from clients to Tiny are the same in either case. An intermediate agent called agent\_multi\_man is used; All messages to a client C are sent to its agent\_multi\_man, which forwards the message to the subsidiary agent responsible for the channel through which that message should be delivered.

#### 4.2 Routing Strategies

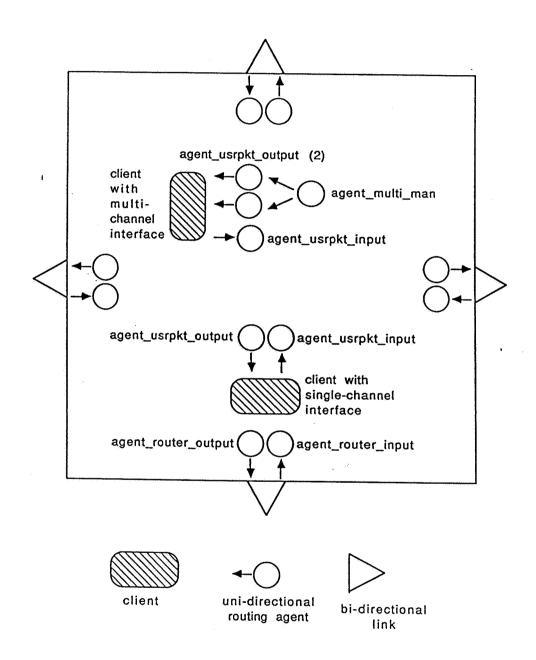

Two routing strategies, called adaptive and sequential, are available for point-to-point message traffic in Tiny. A third strategy is used to implement broadcasts. The sequential strategy guar-

<sup>3</sup>I.E. of the size of the channel array input.

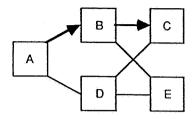

Figure 5: Sequential Routing Strategy

Figure 6: Adaptive Routing Strategy

antees that messages arrive in the order in which they were sent, which is useful for such things as implementing fragmentation of large messages. Tiny implements the sequential strategy by using the same shortest path<sup>4</sup> from any through-routing node towards the destination. (Figure 5).

The adaptive strategy decides locally at each through-routing node which of the shortest paths from that node to the destination seems likely to be quickest. Using this strategy, Tiny examines the output queues of each of the through-routing node's appropriate links, and enqueues the message for the link with the shortest queue (Figure 6).

Finally, the broadcast strategy is implemented using a broadcast tree for each processor P. The tree for each processor is determined once during initialization, and information is stored in each other processor Q to indicate Q's position in P's tree (Figure 7).

#### 4.3 The Interface

Two interfaces for Tiny were initially constructed. The first of these, called the PKT interface, copies data from the user's process into one of Tiny's internal buffers during a send, and copies data back during a receive. The PTR interface, on the other hand, swaps pointers to buffers so that the user's buffer becomes one of Tiny's internal buffers and vice versa during either type of interaction. While faster, this second interface was found to be too fragile to support general applications (see Section 8), and has been removed.

The interface provides the user with four functions: pktRead, pktWrite, pktSeqWrite, and

In fact, the one stored first in the routing table.

<sup>&</sup>lt;sup>5</sup> An alternative way of implementing adaptive routing would be to enqueue the buffer for each possible output link, and have the link which was ready first remove the buffer from the other links' queues. This would require doubly-linked lists, whose maintenance would slow the router down in the general case. In addition, the extra instructions which would have to be executed by the link which wound up sending the message would probably negate most of the time saved by always "guessing" right.

Figure 7: Broadcast Routing

pktBroadcast. These functions, described below, are characterized by blocking reads and non-blocking writes.

#### 4.3.1 Receiving a Message

void pktRead(CHAN \*in, int \*src, \*msg, \*size)

This procedure blocks until a message becomes available on the channel in. The source CID of the message is put in src; the message's size is put in size, and the message data is put in the buffer pointed to by msg.

#### 4.3.2 Sending a Message by the Quickest Route

void pktWrite(CHAN \*out, int dst, \*msg, size)

pktWrite sends a message from the caller to the client identified by dst using adaptive routing. As soon as the message data contained in the buffer pointed to by msg has been copied into one of Tiny's internal buffers this function returns control to the caller.

## 4.3.3 Sending a Message by a Fixed Route

void pktSeqWrite(CHAN \*out, int dst, \*msg, size)

pktSeqWrite sends a message from the caller to the client identified by dst using sequential routing. As soon as the message data contained in the buffer pointed to by msg has been copied into one of Tiny's internal buffers this function returns control to the caller.

#### 4.3.4 Broadcasting a Mesasge

void pktBroadcast(CHAN \*out, int \*msg, size)

pktBroadcast sends a message from the caller to every other client in the network connected to Tiny by the same type of interface channel (see Section 4.1). As soon as the message data contained in the buffer pointed to by msg has been sent down all the necessary links, this function returns control to the caller. (An unfortunate exception to this rule is discussed in Section 8).

Figure 8: Arrangement of Actual Routing Agents

## 5 Agents and Their Internals

The five different agents used within Tiny to implement the router shown in Figure 3 are described below; a typical mix of them is shown in Figure 8. All agents are written in a mixture of C and Tcode (transputer assembler).

- agent\_multi\_man: demultiplexes messages arriving at a client with a multi-channel interface, passing those messages to the client's input agents. Its main loop dequeues a buffer, then enqueues it for a subsidiary agent.

- agent\_router\_input: accepts messages on the input half of a hard link and routes them. Its main loop dequeues a buffer, gets a message into the buffer, and routes the buffer, putting it in another agent's queue.

- agent\_router\_output: handles the output queue for a hard link. Its main loop dequeues a buffer, sends its contents down the link, then decrements the extra reference count of the buffer (Section 5.4.1), and, if this is zero, returns the buffer to its owner.

- agent\_usrpkt\_input: accepts messages from a client process and routes them. Its main loop dequeues a buffer, gets a message into the buffer, makes a header for the message, then routes the buffer, putting it in another agent's queue.

- agent\_usrpkt\_output: gives a message to a client process and frees the buffer. This agent may be a subsidiary agent of an agent\_multi\_man, or may be used directly. Its main loop dequeues a buffer, gives the buffer's contents to the user, then decrements the extra reference count of the buffer, and, if this is now zero, returns the buffer to its owner.

#### 5.1 Agent and Buffer Pages

An agent page, or A-page, is a workspace for a single routing agent. The fields in an A-page are given below; those from AP\_RT to AP\_ENTRY called the agent handle, are pointed to by the workspace pointer Wptr when the agent is running.

| AP_LINK   | A pointer to the next agent, used to chain agents together        |

|-----------|-------------------------------------------------------------------|

|           | while they are being created.                                     |

| AP_FUNC   | An integer indicating the agent type.                             |

| AP_TSPACE | The start of 5 words reserved for transputer instructions [TREF]. |

|           | These are not explicitly manipulated by Tiny.                     |

| AP_TMPO   | A scratch pad used by the agent.                                  |

| AP_BP     | A pointer to the agent's active buffer.                           |

| AP_COUNT  | A count of the number of buffers in the agent's queue,            |

|           | plus 1 for the buffer currently being worked on. When             |

|           | this is 0, the agent should be asleep.                            |

| AP_HEAD   | A pointer to the first buffer in the agent's queue. If            |

|           | AP_COUNT is 1 or less, this value is invalid.                     |

| AP_TAIL   | A pointer to the last buffer in the agent's queue. If             |

|           | AP_COUNT is 1 or less, this value is invalid.                     |

| AP_QOFF   | The offset (in bytes) from the start of the buffers on            |

|           | this transputer to the word used by this agent to link its        |

|           | queue together (see the description of the buffer pages).         |

| AP_CHAN   | The address of the channel for which the agent is responsible.    |

| AP_PID    | The ID of the client for which the agent is responsible.          |

| AP_DEV    | The device number (i.e. channel number in a multi-channel         |

|           | interface) for which the agent is responsible.                    |

| AP_ROUTE  | A pointer to the agent's routing table segment (Section 5.2).     |

| AP_ENTRY  | A pointer to the routing table entry currently being used.        |

|           |                                                                   |

Buffer pages, or B-pages, contain information about message buffers, and are manipulated by agents. The fields in a B-page are listed below; those from BP\_LEN to BP\_OWNER are referred to as the buffer handle.

| BP_LINK  | Used to link buffers together during initialization.      |

|----------|-----------------------------------------------------------|

| BP_BYTES | The maximum size of the message buffer (in bytes).        |

| BP_LEN   | The length of the message data (in bytes).                |

| BP_SRC   | The CID of the process sending the message.               |

| BP_DST   | The CID of the message's destination.                     |

| BP_MSG   | A pointer to the message data associated with the buffer. |

| BP_XREFS | The number of extra references to the buffer. This field  |

|          | is used during broadcasts, when several agents might be   |

|          | reading from the buffer. When IREFS reaches 0, the        |

|          | broadcast is finished.                                    |

| BP_OWNER | A pointer to the workspace of the agent which owns the    |

|          | buffer (see Section 5.4.2).                               |

The remaining entries are links to other buffers, used to chain buffers together to form queues. The number of such links is the same for all buffers on any transputer, though it may differ between transputers. Each group of agents within a given transputer responsible for either a single link or a single client has a unique byte offset (stored in the AP\_QOFF field of its agent page) which indicates how far from the beginning of the B-page their queue's link entry is. Multiple links are provided so that a single buffer can be in the queues of several agents during a broadcast operation.

Storage for buffers is allocated by the user during initialization. Tiny is given a block of memory and two parameters describing the number of buffers to create and the size of each

buffer. This allows users to tailor memory usage to fit their application; typically, they allocate four or five buffers for each output agent's queue, each roughly one kilobyte in size.

#### 5.2 Routing Tables

Routing tables are built during topology exploration. Initially stored as arrays, their cross-referencing indices are converted to pointers during initialization. The structure of a routing table in array form is:

|            | The second secon | the state of the s |          |              |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|

|            | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | routing segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |              |

| I tree ntr | link indices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | routing segments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | l fahlee | tree choce l |

| TTOO_POT   | min mucco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | LOUVILLE SCETHICHUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | values   | TICC SPACE   |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |              |

where:

free ptr is an index into the free space used during initialization;

the link indices are 5 indices (one for each physical link and another for a "pseudo-link" representing the user's processes) indicating where in the routing segments the routing table for messages entering the processor on that link is located:

the routing segments contain a status word and a pair of indices into the tables for each process in the entire network;

the tables are lists of links to which messages may (or must) be sent;

free space is that part of the table which has not been used.

Users select which of Tiny's two routing algorithms it is to use at initialization. One of these provides provable freedom from deadlock [CLA4] by eliminating cycles in routing tables. This is done by routing messages for a destination through different links on a particular processor depending on the link through which that message reached the processor. To allow this, a pointer to a routing table is associated with each input link. These pointers may indicate the routing table, or different routing tables. A fifth routing table is required for routing messages which originate in the user processes on the transputer. Each link's index therefore indicates a segment of the form:

| status | $(txmt_0, brdcst_0)$ | ••• | $(txmt_n, brdcst_n)$ |

|--------|----------------------|-----|----------------------|

|        |                      |     |                      |

where status indicates whether the table is bad (i.e. Tiny hasn't built the table yet), in an array/index state (as described here), or has been converted to pointers. The remainder of the segment contains pairs of indices into the tables area. The table indicated by the first index is a negative-terminated list of the links through which messages for a particular process may be sent; if there are several equally-short paths to a process, the list will contain more than one entry (Section 5.4). The table indicated by the second index is a negative-terminated list of the links through which broadcast messages from other processors through this processor must be sent.

These negative-terminated tables consist of one or more integer entries, followed by the value -1. A typical such table would be:

3 0 -1

meaning that messages to or from the corresponding process could or must be sent through links 3 and 0.

#### 5.3 Enqueueing and Dequeueing Buffers

The basic operations performed by Tiny's internal agents are to enqueue or dequeue a message buffer. Agents can do this for other agents, i.e. an agent  $A_0$  can manipulate agent  $A_1$ 's internals to put a buffer B into  $A_1$ 's queue. At all times, each agent keeps a count of the number of buffers under its control. The buffer currently being worked on is called the *active buffer*; the agent's other n-1 buffers form its queue. The three different cases are:

| Number | Meaning                                                          |

|--------|------------------------------------------------------------------|

| 0      | No buffers in queue, no buffer being worked on — agent is asleep |

| 1      | No buffers in queue, active buffer being worked on               |

| > 1    | Buffers in queue, active buffer being worked on                  |

When an agent  $A_0$  wants to enqueue a buffer for an agent  $A_1$  it starts by resetting the workspace pointer register to point at  $A_1$ 's workspace. If  $A_1$  is asleep,  $A_0$  makes the buffer  $A_1$ 's active buffer and puts  $A_1$  back on the process queue. If  $A_1$  has an active buffer but no queue,  $A_0$  creates a single-buffer queue for it; if  $A_1$  already has a queue,  $A_0$  appends the buffer to that queue.

Dequeueing buffers is simpler than enqueueing them. The agent's buffer count is decremented, and, if the count has become zero, the agent takes itself off the active process queue. If the count has become 1 the buffer which was at the head of the queue is made the active buffer. Finally, if the count after the decrement is greater than 1, the buffer at the head of the queue is made the active buffer, and the head-of-queue pointer changed to point to the next buffer in the queue.

#### 5.4 Routing

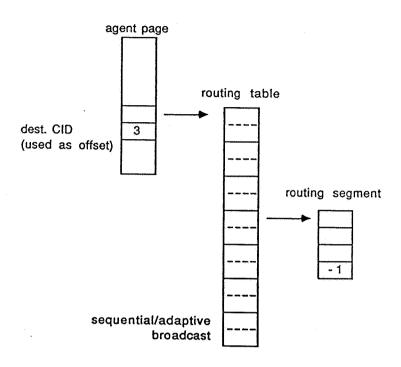

Messages are routed as soon as they arrive in a processor. Routing relies on a 3-word message header which Tiny keeps in each buffer page. The three entries in this header are the message source and message destination CID's, and the message length (in bytes).

To access the correct routing table entry for a message, Tiny adds the CID of the message's destination to the base address of the agent's routing segment (stored locally in AP\_ROUTE) to obtain the address at which a pointer to the routing table entry is stored (Figure 9). This extra level of indirection is needed because the routing tables used for broadcast messages may be of arbitrary size.

Tiny's first action when routing is to discover which strategy is being used by testing the two least significant bits in the destination field of the header. The RT\_FST bit indicates that the sequential strategy is being used, while RT\_ANY indicates adaptive routing. If FT\_FST is set, Tiny adds the destination CID to the routing table base address in the agent handle and looks up the routing table segment starting at that address. The entry found here is the address of the workspace of the agent responsible for that link. The current agent puts the buffer in that agent's queue.

If the adaptive strategy bit is set in the message header, Tiny accesses the routing table segment as above, but then examines the lengths of the queues of the agents responsible for the links down which it could send the message. The message is enqueued for an agent with a shortest queue length (Section 5.4).

When a message is first introduced into the network, Tiny checks to see whether it is a broadcast message. If it is, then the CID of the *source* process is put into message's destination field, and bit 2 set in this field. Since the low two bits in a transputer word act as a byte selector, while the other 30 bits are a word selector, this bit being 1 guarantees an odd word address, while the bit being 0 guarantees an even address one space lower in memory. When the word-selector

Figure 9: Accessing Routing Tables

bits of the destination field are added to the routing table base address stored in the agent page, Tiny will select the second of the two words in that routing entry. The table this points to contains the broadcast tree information for messages from the source process, rather than routing information for messages to that process.

#### 5.4.1 Multiple References to Buffers